ʯ��ׯ����ѧԺ

����ѧԺ

�������γ���Ʊ���

�� Ŀ �������

�� ��

ѧ ��

�� ��

ָ����ʦ

�� ��

20##��6��

Ŀ ¼

1. �γ����Ŀ��·······················································································

2. ��������ѡ��·······················································································

3. ��Ʒ��� ···························································································

4�� ģ������····························································································

5. VHDLʵ��··························································································

6. ���Է���······························································································

7. �γ���ƻع��ܽ� ···············································································

�� �� �� �� ····························································································

��¼ ······································································································

1�γ����Ŀ��

��1�� ���һ�������������ʱ��Χ��0��----59��59.9�롣

��2�� ��λ���ؿ����κ������ʹ�ã�ֻҪ��һ�¸�λ���أ���ʱ�������㣬�������´μ�ʱ������

��3�� ������/ͣ���أ���һ����/ͣ���أ�������ʱ����ʼ��ʱ���ٰ�һ����/ͣ������ֹͣ��ʱ��

2��������ѡ��

��1�� �� Ӳ����������

�����������Ʋ����˹���ǿ���VHDL���ԣ������к�ǿ����Ϊ������������Ʒ���������֧�ֿ��ģ����Ʒ�����

��2�� �� QuartusII������������

����Ʋ��õ���������������������Altera��˾��QuartusII����֧�ֶ���������뷽��������ԭ��ͼ���롢�ı����롣

��3�� ��EDAʵ�鿪��ϵͳ

����Ʋ��õ�EDAʵ�鿪��ϵͳ����Ҫ�����ṩ�ɱ�������������ص�·��EDAʵ�鿪������Χ��Դ����Ӳ����֤�á�

3��Ʒ���

����������Ƶ����������ʹ��ģ����Ƶ�˼�룬����һ��������ģ�飬Ȼ�����ѡ������һ����/ͣ����ʱ��������ʱģ�飬���������ʼ��ʱ����ʱ����ģ�齫ʱ���ź�ת��Ϊ�߶������룬����ʾģ����ʱ��0.1�롢���λ����ʮλ���ָ�λ����ʮλ�ź�ʵʱ��ʾ������

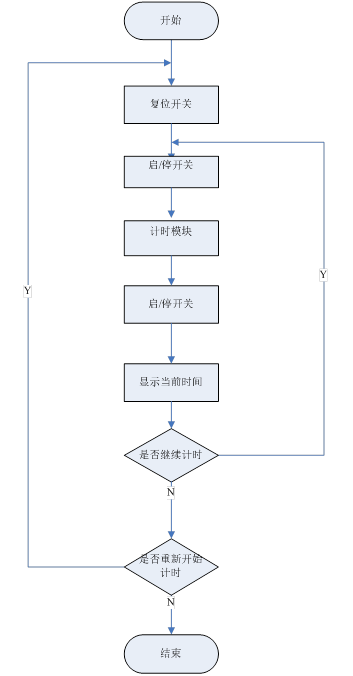

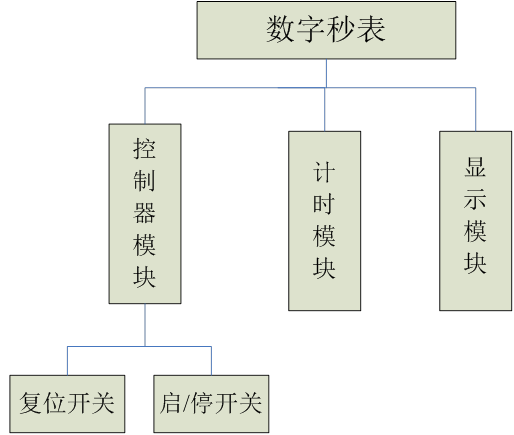

����ͼ���£�

4ģ������

��1�� ģ��һ��������

������λ���غ���/ͣ���ء���λ���ؿ����κ������ʹ�ã�ֻҪ��һ�¸�λ���أ���ʱ�������㣬�������´μ�ʱ��������һ����/ͣ���أ�������ʱ����ʼ��ʱ���ٰ�һ����/ͣ������ֹͣ��ʱ��

��2�� ģ�������ʱ

������/ͣ���غ���ʱ�ӿ�ʼ��ʱ����ʱ��Χ��0��----59��59.9�룬����ļ�ʱʱ���źţ�ʱ������Ϊ0.1s����������10nsģ��0.1s���������ʱ�������ʡȥ��Ƶ��·����ʱģ��������ʮ���Ƽ����������������Ƽ��������ɣ���ʮ���Ƽ�������ʾ0.1������λ���ָ�λ���������Ƽ�������ʾ��ʮλ�ͷ�ʮλ��

��3�� ģ������ʾ��

��ʱ���ź�ת�����߶������룬������7����������led����ܣ������ӵ͵�ƽ��ÿ������ܵ�a---g��������һ��bcd-�߶��������������������ˣ�����Ҫ7��bcd-�߶������������ֱ���ʾ0.1�롢�ָ��������λ����ʮλ���ָ������ָ�λ����ʮλ��

ģ��ͼ���£�

5 VHDLʵ��

��1����ʱģ�������ƣ�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY liujinzhi IS

PORT(CLK,reset,EN:IN STD_LOGIC;

CN: OUT STD_LOGIC;

COUNT6:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END liujinzhi;

ARCHITECTURE ART OF liujinzhi IS

SIGNAL SCOUNT6: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

COUNT6<=SCOUNT6;

PROCESS(CLK,reset,EN)

BEGIN

IF(reset='1')THEN

SCOUNT6<="0000";CN<='0';

ELSIF RISING_EDGE(CLK)THEN

IF(EN='1')THEN

IF SCOUNT6="0101"THEN

SCOUNT6<="0000";CN<='1';

ELSE

SCOUNT6<=SCOUNT6+'1';CN<='0';

END IF;

END IF;

END IF;

END PROCESS;

END ART;

��2����ʱģ��ʮ���ƣ�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY shijinzhi IS

PORT(CLK: IN STD_LOGIC;

reset: IN STD_LOGIC;

EN: IN STD_LOGIC;

CN: OUT STD_LOGIC;

COUNT10:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END shijinzhi;

ARCHITECTURE ART OF shijinzhi IS

SIGNAL SCOUNT10: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

COUNT10<=SCOUNT10;

PROCESS(CLK,reset,EN)

BEGIN

IF(reset='1')THEN

SCOUNT10<="0000";CN<='0';

ELSIF RISING_EDGE(CLK)THEN

IF(EN='1')THEN

IF SCOUNT10="1001"THEN

CN<='1';

SCOUNT10<="0000";

ELSE

CN<='0';

SCOUNT10<=SCOUNT10+'1';

END IF;

END IF;

END IF;

END PROCESS;

END ART;

��3�������߶���������

library ieee;

use ieee.std_logic_1164.all;

entity display_7448 is

port(

lt:in std_logic;

bi:in std_logic;

rbi:in std_logic;

rbo:out std_logic;

a:in std_logic_vector(3 downto 0);

segout:out std_logic_vector(6 downto 0));

end display_7448;

architecture display_7448p of display_7448 is

begin

process(lt,bi,a)

begin

if(lt='1' and bi='1' and rbi='1' and a="0000")then

segout<="1111110";rbo<='1';

elsif(lt='1' and bi='1' and a="0001")then

segout<="0110000";rbo<='1';

elsif(lt='1' and bi='1' and a="0010")then

segout<="1101101";rbo<='1';

elsif(lt='1' and bi='1' and a="0011")then

segout<="1111001";rbo<='1';

elsif(lt='1' and bi='1' and a="0100")then

segout<="0110011";rbo<='1';

elsif(lt='1' and bi='1' and a="0101")then

segout<="1011011";rbo<='1';

elsif(lt='1' and bi='1' and a="0110")then

segout<="0011111";rbo<='1';

elsif(lt='1' and bi='1' and a="0111")then

segout<="1110000";rbo<='1';

elsif(lt='1' and bi='1' and a="1000")then

segout<="1111111";rbo<='1';

elsif(lt='1' and bi='1' and a="1001")then

segout<="1110011";rbo<='1';

elsif bi='0' then

segout<="0000000";

rbo<='0';

elsif(lt='0' and bi='1')then

segout<="1111111";

rbo<='1';

end if;

end process;

end display_7448p;

��¼������ԭ��ԭ��ͼ���shuzimiaobiao\miaobiao.bdf

6���Է���

1�����ƣ�

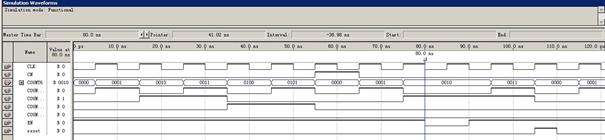

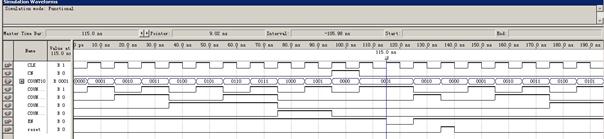

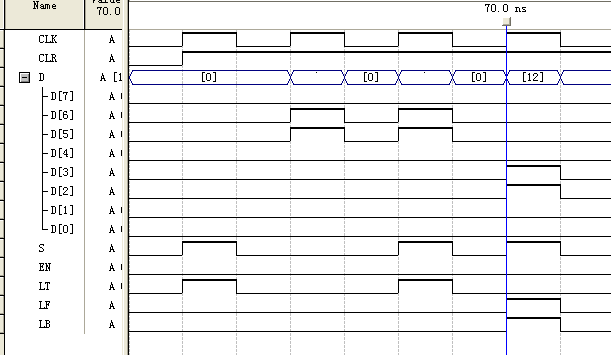

ͼ1 �����Ƽ���������ͼ

��ͼ��ʾ�������ʱ��ʼ��������Ϊ10ns��ʱ���ź�clkģ��0.1s��ʱ��clk���ɼ���ÿ��һ��clk,COUNT6��1�����ӵ�0101��6��ʱ������һ��clk��COUNT�ٴδ�0��ʼ������CN������λ��ENΪ��/ͣ���������ʱ�����У�������/ͣ��ʹEN=0����ʱֹͣ���ٰ�����/ͣ��ʹEN=1����ʱ������resetΪ��λ������reset=1ʱ�������ʱ���㡣

2ʮ���ƣ�

ͼ2 ʮ���Ƽ���������ͼ

��ͼ��ʾ�������ʱ��ʼ��������Ϊ10ns��ʱ���ź�clkģ��0.1s��ʱ��clk���ɼ���ÿ��һ��clk,COUNT10��1�����ӵ�1001��9��ʱ������һ��clk��COUNT�ٴδ�0��ʼ������CN������λ��ENΪ��/ͣ���������ʱ�����У�������/ͣ��ʹEN=0����ʱֹͣ;�ٰ�����/ͣ��ʹEN=1����ʱ������resetΪ��λ������reset=1ʱ�������ʱ���㡣

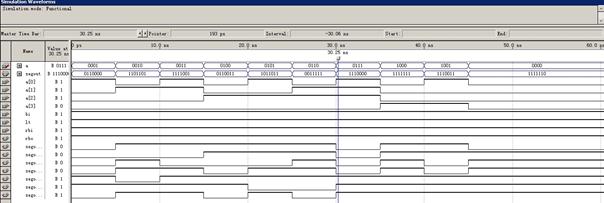

3�߶�������������

ͼ3�߶���������������ͼ

��ͼ��ʾ������ź�segouta_gΪ�����ź�a����Ӧ���߶������롣

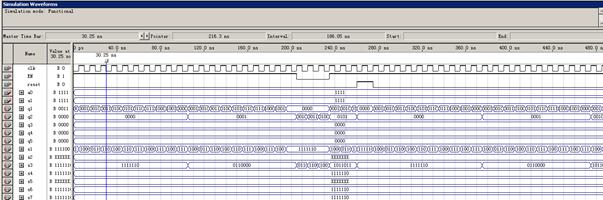

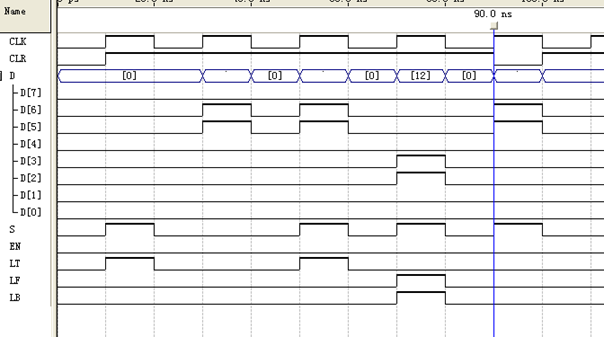

4���������

ͼ4 �����������ͼ

ͼ4 �����������ͼ

��ͼ��ʾ��s1-s7�ֱ���ʾ0.1�롢�ָ��������λ����ʮλ���ָ������ָ�λ����ʮλ�����λ���ָ�λΪʮ���ƣ���ʮλ����ʮλΪ�����ơ�ENΪ��/ͣ���������ʱ�����У�������/ͣ��ʹEN=0����ʱֹͣ���ٰ�����/ͣ��ʹEN=1����ʱ������resetΪ��λ������reset=1ʱ�������ʱ���㡣����������ͼ��֪������������ﵽ�����Ҫ��

7�γ���ƻع��ܽ�

VHDL������һ�ֺ����õ�Ӳ���������ԣ�ͨ�����ܵ�ѧϰ��ʵ�����ڻ���ʵ������ʦҪ�����ƣ�ͨ���Լ�����ʵ����ͬѧ�ǵĽ������о������һ����ƣ����������Ӧ�еĻ������̣��ܿ��ģ�Ҳʹ�Ҷ�EDA�γ�VHDL�������˸���̵��˽⣬ͬʱҲ�������ҵ���Ȥ��ͨ������������Կ���������������ﵽ�����Ҫ����������������������ģ�黯��Ʒ������ײ��Ԫ��ʹ��Ӳ���������� VHDL�����������������ԭ��ͼ�ķ��������������������EDA�������ߣ�ʵ��ϵͳ���ܡ�

��������ļ�ʱ��Χ��0��----59��59.9�룬��λ���ؿ����κ������ʹ�ã�ֻҪ��һ�¸�λ���أ���ʱ�������㣬�������´μ�ʱ������������/ͣ���أ���һ����/ͣ���أ�������ʱ����ʼ��ʱ���ٰ�һ����/ͣ������ֹͣ��ʱ�������ȽϷ��㡣��֮������������нϺõ�Ӧ��ǰ����

�����

��1����������ԭ����VHDL��ơ�

��2������������ϵͳ��ơ�

�ڶ�ƪ��20xx���������γ���Ʊ���

ʯ��ׯ����ѧԺ

��Ϣ����ѧԺ

�������γ���Ʊ���

�� Ŀ �����������

�� ��

ѧ ��

�� ��

ָ����ʦ

�� ��

20##��6��

Ŀ ¼

1. ��������··························································································· 3

2. ��������ѡ��····················································································· 3

3. ��Ʒ��� ·························································································· 3

4�� ģ������·························································································· 4

5. VHDLʵ��························································································· 5

6. ���Է���··························································································· 13

7. �γ���ƻع��ܽ� ············································································ 15

�� �� �� �� ························································································· 15

��¼ ··································································································· 15

һ�� ��������

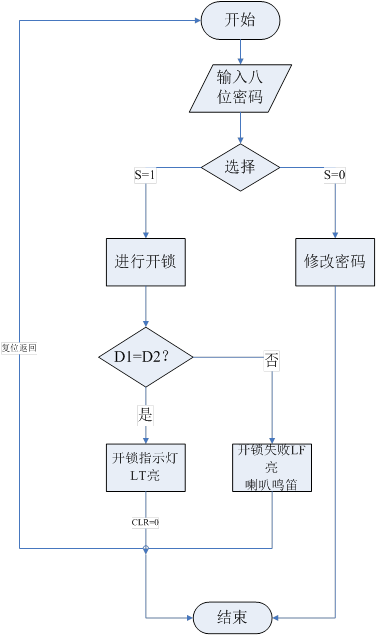

���������������������������������룬������������û��Լ�ѡ������������������������һ�£�����������Ӧ��տ�����·�������������źš�

��Ƶİ�λ������������

��1�� ��������Ϊ8λ��������������������λ����λֵ�����ڸ���������һ�£��Ұ��涨������ʱ�����ɿ���������������ָʾ��LT������ϵͳ���д���״̬�������������źš�

��2�� ���������������ȷ������Ҫ�����ڸ����������ǿɵ��ģ���Ԥ�÷��㣬�����Ժá�

��3�� �������ı�����ʽ�ǵ���ָʾ��LF����ʹ����������������ֱ�����¸�λ���أ�������ֹͣ����ʱ�����������Զ�����ȴ���һ�ο�����״̬��

������������ѡ��

��1��Ӳ����������

��������������Ʋ����˹���ǿ���VHDL���ԣ������к�ǿ����Ϊ������������Ʒ���������֧�ֿ��ģ����Ʒ�����

��2��QuartusII������������

����Ʋ��õ���������������������Altera��˾��QuartusII����֧�ֶ���������뷽��������ԭ��ͼ���롢�ı����롣

��3��EDAʵ�鿪��ϵͳ

����Ʋ��õ�EDAʵ�鿪��ϵͳ����Ҫ�����ṩ�ɱ�������������ص�·��EDAʵ�鿪������Χ��Դ����Ӳ����֤�á�

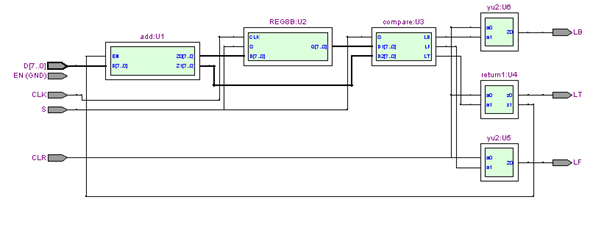

������Ʒ���

��������Ƶĵ�����������ʹ��ģ����Ƶ�˼�룺��ʼ�����λ�������֣�Ȼ�����ѡ����ѡ��S=0ʱ�����и����벢����Ĵ����У�S-1ʱ�����п������������ɹ�����LT=1������ʧ�ܣ���LF=1������LB=1�������ѡ�

����ͼ���£�

�ģ�ģ������

1.ģ��һ����ѡ��

�����������ѡ��S=0�����룬S=1�ͽ�����һ��������

2.ģ������Ĵ���

�����и����룬�������������Ĵ����ȴ���һ�αȽϣ������п�������������ڼĴ�����ԭ�е����롣

3.ģ�������Ƚ���

���Ĵ����д������������п����Ƚϵ�������ȣ������ɹ���ָʾ��LT=1��������ʧ�ܣ�ָʾ��LF=1������LB=1�������ѡ�

4.ģ���ģ���λ

�����ɹ�ָʾ��LT�������¸�λ��CLK=0�����ش�ѡ��״̬��

5.ģ���壺��λ����

����ʧ��ָʾ��LF�������¸�λCLK=0�����ء�

6.ģ����������

����ʧ������LB���ѣ����¸�λCLK=0��ֹͣ���ѡ�

�壺VHDLʵ��

1.ģ��һ����ѡ��

library ieee;

use ieee.std_logic_1164.all;

entity add is

port(D:in std_logic_vector(7 downto 0);

EN:in std_logic;

Z0:out std_logic_vector(7 downto 0);

Z1:out std_logic_vector(7 downto 0));

end ;

architecture one of add is

begin

process(D,EN)

begin

if EN='0' then

Z0<=D;

Z1<=D;

END IF;

end process;

end one;

3.ģ������Ĵ���

library ieee;

use ieee.std_logic_1164.all;

entity REG8B is

port(CLK: in std_logic;

S:in std_logic;

D:in std_logic_vector(7 downto 0);

Q:out std_logic_vector(7 downto 0));

end;

architecture ONE of REG8B is

signal M: std_logic_vector(7 downto 0):="00000000";

begin

process(S,CLK)

begin

if CLK'event and CLK='1' then

case S is

when '1' => Q<=M;

WHEN OTHERS =>M<=D;

end case;

end if;

Q<=M;

end process;

end;

4.ģ�������Ƚ���

library ieee;

use ieee.std_logic_1164.all;

entity compare is

port(S:in std_logic;

D1:in std_logic_vector(7 downto 0);

D2:in std_logic_vector(7 downto 0);

LT:out std_logic;

LF:out std_logic;

LB:out std_logic);

end;

architecture ONE of compare is

begin

process(S,D1)

begin

if S='0' then

LF<='0';

LB<='0';

LT<='0';

elsif( D1=D2) then

LT<='1';

LF<='0';

LB<='0';

else

LF<='1';

LB<='1';

LT<='0';

end if;

end process;

end;

5.ģ���ģ���λ

library ieee;

use ieee.std_logic_1164.all;

entity return1 is

port(a0,a1:in std_logic;

z0,z1:out std_logic);

end return1;

architecture one of return1 is

begin

z0<= a0 and a1;

z1<= a0 and a1;

end;

6.ģ���壺��λ����

library ieee;

use ieee.std_logic_1164.all;

entity yu2 is

port(a0,a1:in std_logic;

Z0:out std_logic);

end yu2;

architecture behave of yu2 is

begin

z0<=a0 and a1;

end behave;

7.ģ����������

library ieee;

use ieee.std_logic_1164.all;

entity yu2 is

port(a0,a1:in std_logic;

Z0:out std_logic);

end yu2;

architecture behave of yu2 is

begin

z0<=a0 and a1;

end behave;

��ϳ��ܵ�VHDL����ʵ�֣�

library ieee;

use ieee.std_logic_1164.all;

entity numberlock is

port(D:in std_logic_vector(7 downto 0);

CLR:in std_logic; --��λ

CLK:in std_logic; --ʱ���ź�

S:in std_logic; --ѡ���ź�

EN:in std_logic;

LT:out std_logic; --����

LF:out std_logic; --����

LB:out std_logic); --����

end;

architecture one of numberlock is

component REG8B --�Ĵ���

port(CLK: in std_logic;

S:in std_logic;

D:in std_logic_vector(7 downto 0);

Q:out std_logic_vector(7 downto 0));

end component;

component compare --�Ƚ���

port(S:in std_logic;

D1:in std_logic_vector(7 downto 0);

D2:in std_logic_vector(7 downto 0);

LT:out std_logic;

LF:out std_logic;

LB:out std_logic);

end component;

component yu2 --����2��������

port(a0,a1:in std_logic;

Z0:out std_logic);

end component;

component add --����

port(D:in std_logic_vector(7 downto 0);

EN:in std_logic;

Z0:out std_logic_vector(7 downto 0);

Z1:out std_logic_vector(7 downto 0));

end component;

component return1 --����

port(a0,a1:in std_logic;

z0,z1:out std_logic);

end component;

signal temp1,temp2,temp3:std_logic_vector(7 downto 0);

signal temp4,temp5,temp6,temp7:std_logic;

begin

U1:add port map(D=>D,EN=>temp7,Z0=>temp1,Z1=>temp2);

U2:REG8B port map(S=>S,D=>temp1,CLK=>CLK,Q=>temp3);

U3:compare port map(S=>S,D1=>temp3,D2=>temp2,LT=>temp4,LF=>temp5,LB=>temp6);

U4:return1 port map(a0=>CLR,a1=>temp4,Z0=>LT,Z1=>temp7);

U5:yu2 port map(a0=>CLR,a1=>temp5,Z0=>LF);

U6:yu2 port map(a0=>CLR,a1=>temp6,Z0=>LB);

end;

�������Է��棺

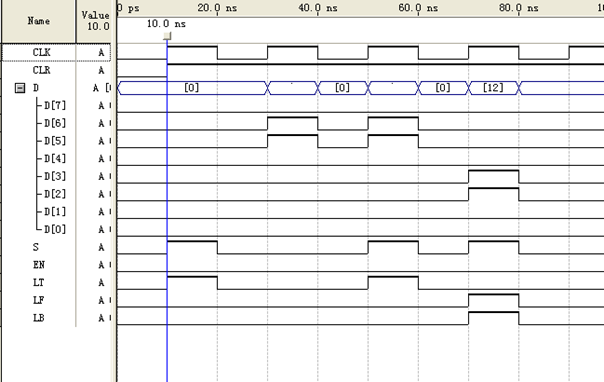

���Գɹ�����ͼ���£�

1.

˵������������Ч����������Ϊ00000000ʱ��Sѡ1���п����������ɹ����LT=1��

˵������������Ч����������Ϊ00000000ʱ��Sѡ1���п����������ɹ����LT=1��

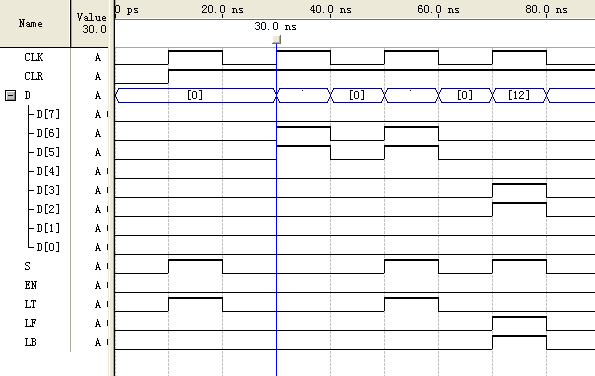

2.

˵������������Ч����������01100000��ѡ��S=0���������롣

˵������������Ч����������01100000��ѡ��S=0���������롣

3.

˵������������Ч�������ĺ������01100000��ѡ�����������ɹ�LT=1.

˵������������Ч�������ĺ������01100000��ѡ�����������ɹ�LT=1.

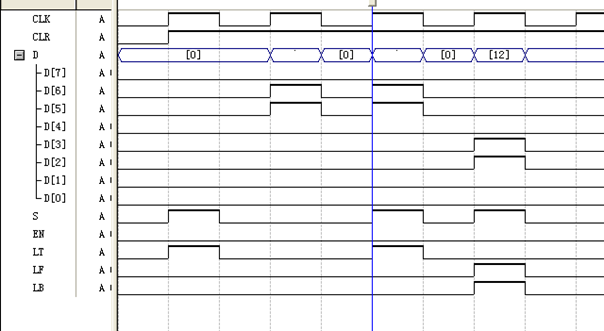

4.

˵������������00001100���п�����00001100������01100000������ʧ��LF=1��LB=1��

˵������������00001100���п�����00001100������01100000������ʧ��LF=1��LB=1��

5.

˵���������ɹ�����и�λ���ɹ���

˵���������ɹ�����и�λ���ɹ���

������������ʾͼ���£�

�ߣ��γ���ƻع��ܽ

��ε��������������һ��ʼ��һ��˼·��û�У�֮��������ĥ���˾���˼·��������ʦ��ָ���������˷�ģ�����Ʒ��������ģ��Ľ��б�д���ԣ������ۺ���һ�飬�������������Ʒ�����ͨ����ογ���ƣ��Ҹ����������δ�ʵ���н����о���ʵ����ƣ�������������VHDL���Եı�д��ʵ�֡�

�����

��������ԭ����VHDL��ơ�