数字电路课程设计报告

题目:两位十进制计数显示器

院 系 信息工程学院

专 业 通信工程

学 号 AP1005839

学生姓名

指导教师

报告日期 2013年4月

1、设计任务与要求

本设计主要采用芯片有555定时器、74LS162计数器、74LS48七段字形译码器,以及七段LED数码管。能过以上元器件的组合,构成一个两位十进制计数显示器,实现循环依序显示0~99的数字。

要求每位同学独立设计电路原理图,制作PCB电路板并印制上自己的学号。

2、电路设计

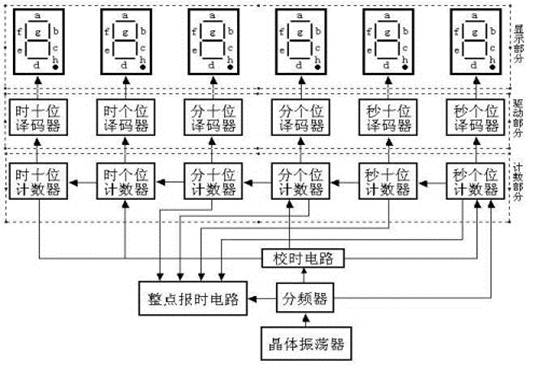

2.1、电路组成框图

图1 电路组成框图

本设计的电路组成框图如图1所示。电路的基本工作原理:首先通过波形产生电路产生—方波脉冲作为时钟信号,将此信号输入到计数电路中,编译成—4位十进制信号输出,经显示驱动电路译码—7位输出信号驱动七段LED显示器,使其从0~9循环显示字形。

2.2、电路总原理图

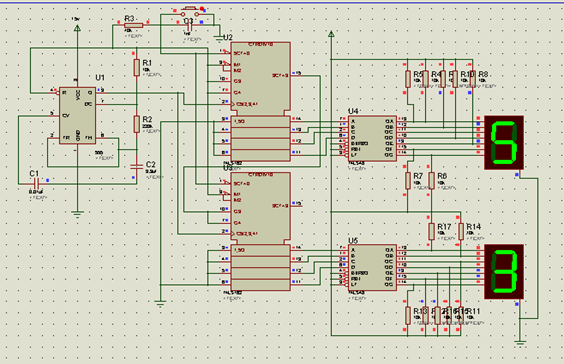

图2 电路总原理图

电路总原理图主要有波形产生模块、计数模块、驱动显示模块及显示模块组成。如图所示,波形产生模块通过555产生周期为1.023s的方波,周期的大小是由R1、R2、C2决定,然后通过74LS162进行计数再由驱动电路驱动显示两位十进制计数器。

2.3、各模块工作原理

2.3.1波形产生电路

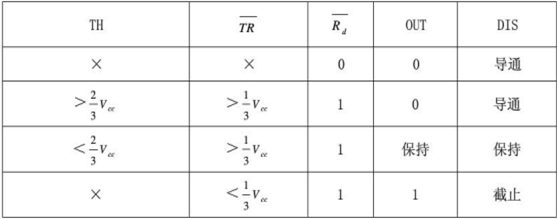

表1 555定时逻辑功能表

图3 555定时器内部结构

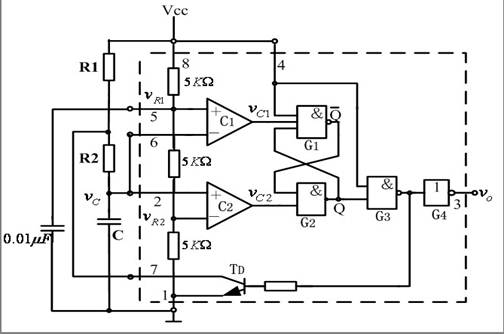

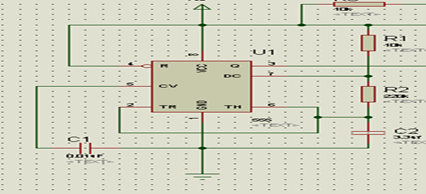

图4 555波形产生电路

如图所示。波形产生如555定时器构成,555构成多谐振荡电路工作原理如下:

接通电源后,电源VDD通过R1和R2对电容C2充电,当Uc<1/3VDD时,振荡器输出Vo=1,放电管截止。当Uc充电到≥2/3VDD后,振荡器输出Vo翻转成0,此时放电管导通,使放电端(DIS)接地,电容C通过R2对地放电,使Uc下降。当Uc下降到≤1/3VDD后,振荡器输出Vo又翻转成1,此时放电管又截止,使放电端(DIS)不接地,电源VDD通过R1和R2又对电容C2充电,又使Uc从1/3VDD上升到2/3VDD,触发器又发生翻转,如此周而复始,从而在输出端Vo得到连续变化的振荡脉冲波形。脉冲宽度TL≈0.7R2C2由电容C2放电时间决定,TH=0.7(R1+R2)C2,由电容C2充电时间决定,脉冲周期T≈TH+TL。

参数计算:充电时间: TH=0.69(R1+R2)*C2=0.523s

放电时间: TL=0.69*R2*C2=0.500s

震荡周期: T=TH+TL=1.023s

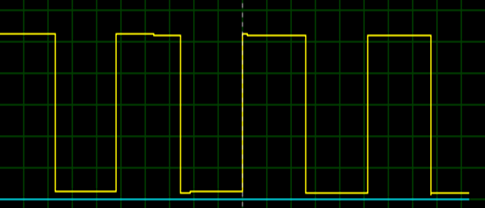

仿真波形:

图5 仿真波形图

2.3.2、计数器电路

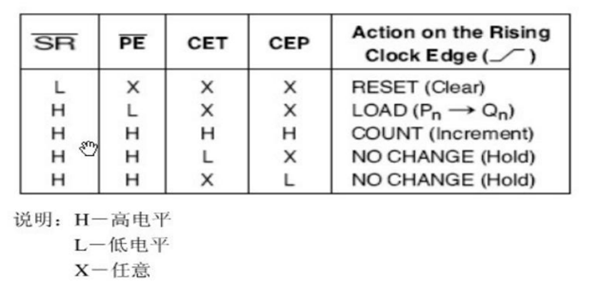

表2 74LS162功能表

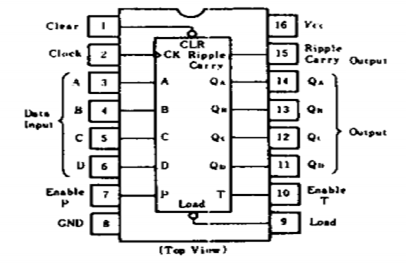

图6 74LS162管脚图

本实验的计数电路由两个74LS162构成。74LS162是十进制同步计数器,功能表如上图所示,当清零端SR为低电平时,在时钟上升沿作用下实现同步清零。当置数端PE为低电平时,在时钟上升沿作用下实现同步置数。SR,PE为高电平,CEP或CET为低电平时,保持结果。当CEP、CET、PE、SR同时为高电平时,在时钟上升沿作用下Q0—Q3输出计数结果。当计数器计到9时进位输出端TC输出高电平。时钟信号分别输入到两个74LS162芯片的2脚分别产生个位与十位计数计数。个位74LS162,使CEP、CET(状态控制端)、PE(置数端)、SR(清零端)接高电平,使之计数:而十位的74LS162与个位共用相同的时钟,PE、SR高电平,CET,CTP接个位的进位信号TC。当个位的TC进位信号来的时候,使CEP、CET变高电平,CLK到来的时候,可实现进位数,没有进位的时候保持,输出端接译码电路。

2.3.3显示驱动电路

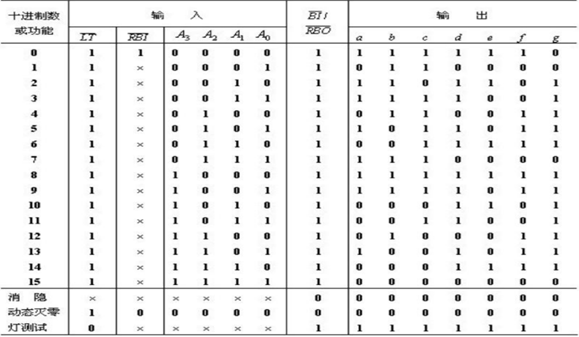

显示驱动电路由两个74LS48译码器和14个上拉电阻组成。74ls48的功能表如下:

表3 74LS48真值表

74LS48是共阴数码管译码器。个位和十位的74LS48的灯LT(测试端)、RIB(灭零端)、BI/RBO(动态输出端)均接高电平,实现正常译码。设计时输出端接上上拉电阻,以增加共阴数码管的亮度。

2.4、PCB图

图7 PCB图

3、焊接调试记录

根据以上原理图制好板后,开始焊接,焊好后开始调试,第一次调试时发现电路有时候不能正常工作,用手感受芯片的温度没有发烫,所以排除芯片短路的可能,后来发现有时用力压压电路板又能正常工作,故怀疑是虚焊造成的,用万用表对所有的焊接点进行测试后发现没有虚焊点,有时能正常工作说明芯片的连接电路没有问题,判断可能是某个原件损坏,最后一个个排查后发现555定时器芯片的外接电路的电容接触不良,更换电容后电路的所有功能都能正常实现,焊接调试结束。

4、总结

在这次的两位十进制计数显示器过程中,更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。也锻炼了自己独立思考问题的能力和通过查看相关资料来解决问题的习惯。虽然这只是一次简单的课程设计,但通过这次课程设计我们了解了课程设计的一般步骤,和设计中应注意的问题。设计本身并不是有很重要的意义,而是对待问题时的态度和处理事情的能力。设计的过程,设计的思想和设计电路中的每一个环节,电路中各个部分的功能是如何实现的。各个芯片能够完成什么样的功能,使用芯片时应该注意那些要点等等这些环节都要求我们不能马虎对待,只有认真做好每个环节才能让我们学到更多掌握得更好。

参考文献

[1]李瀚荪. 简明电路分析基础[M].北京高等教育出版社.2002

[2]徐秀平. 数字电路与逻辑设计[M].北京电子工业出版社.2010

[3]廖惜春. 模拟电子技术基础[M].武汉华中科技大学出版.2008

[4]阎石. 数字电子技术基础[M].北京高等教育出版社.2006

[5]周良权. 数字电子技术基础[M].北京高等教育出版社.1994

第二篇:课程设计 数字电子钟设计报告

数字电子钟设计报告

目 录

1.实验目的………………………………………………………………………2

2.实验题目描述和要求 …………………………………………………………2

3.设计报告内容…………………………………………………………………2

3.1实验名称………………………………………………………………………2

3.2实验目的………………………………………………………………………2

3.3实验器材及主要器件…………………………………………………………2

3.4数字电子钟基本原理…………………………………………………………3

3.5数字电子钟单元电路设计、参数计算和器件选择…………………………3-8

3.6数字电子钟电路图……………………………………………………………9

3.7数字电子钟的组装与调试……………………………………………………9

4.实验结论………………………………………………………………………9

5.实验心得………………………………………………………………………10

参考文献 …………………………………………………………………………10

1.实验目的

※掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;

※提高电路布局﹑布线及检查和排除故障的能力;

※培养书写综合实验报告的能力。

2.实验题目描述和要求

(1)设计一个有“时”、“分”、“秒”(24小时59分59秒)显示,且有校时功能的电子钟;

(2)用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试;

(3)画出框图和逻辑电路图,写出设计、实验总结报告;

(4)选做:整点报时。在59分51秒、53秒、55秒、57秒输出500Hz音频信号,在59分59秒时输出1000Hz信号,音频持续1s,在1000Hz音频结束时刻为整点。

3.设计报告内容

3.1实验名称

数字电子钟

3.2实验目的

·掌握数字电子钟的设计、组装与调试方法;

·熟悉集成电路的使用方法。

3.3实验器材及主要器件

(1)cc40192( 6片)

(2)cc4011(6片)

(3)74LS2O(2片)

(4)共阴七段显示器(6片)

(5)电阻、电容、导线等(若干)

3.4数字电子钟基本原理

数字电子钟的逻辑框图如图3-4所示。它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

图3-4

图3-4

3.5数字电子钟单元电路设计、参数计算和器件选择

(一)计数器

秒脉冲信号经过6级计数器,分别得到“秒”个位、十位、“分”个位、十位以及“时”个位、十位的计时。“秒”“分”计数器为六十进制,小时为二十四进制。

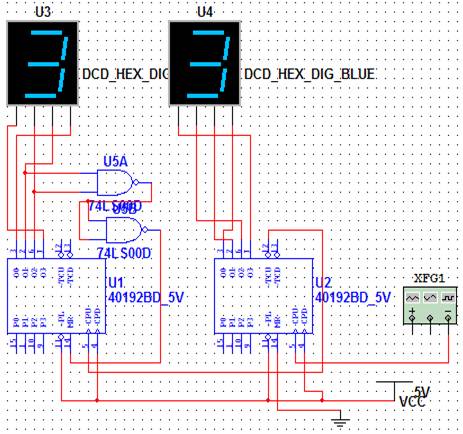

(1)六十进制计数

由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完成一分钟之内秒数目的累加,并达到60秒时产生一个进位信号,所以,选用两片cc40192和一片cc4011组成六十进制计数器,来实现六十进制计数。其中,“秒”十位是六进制,“秒”个位是十进制。如图3-4-3-1所示。

图3-4-3-1所示(60进制计数构造)

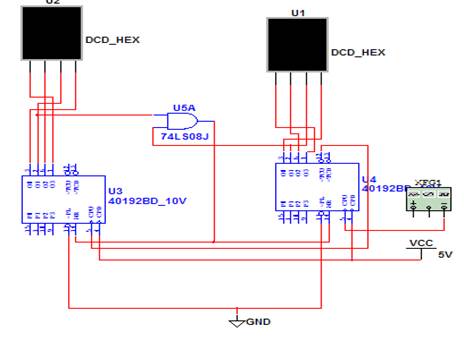

(2)二十四进制计数

“12翻1”小时计数器是按照“01——02——03——……——22——23——00——01——02——……”规律计数的,这与日常生活中的计时规律相同。在此实验中,它是由两片cc40192和一片cc4011构造成的同步二十四计数器,利用异步清零端实现起从23——00的翻转,其中“24”为过渡状态不显示。其中,“时”十位是3进制,“时”个位是十进制。如图3-4-3-2所示.

如图3-4-3-2所示.

(二)显示器

本系统用七段发光二极管来显示译码器输出的数字,显示器有两种:共阳极显示器或共阴极显示器。74LS48译码器对应的显示器是共阴极显示器。

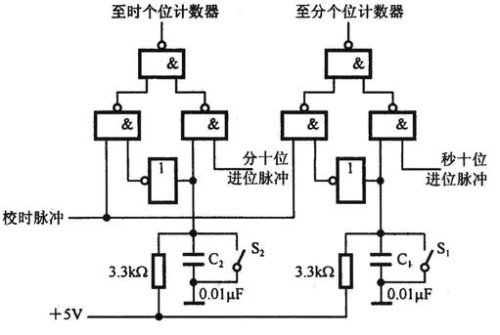

(三)校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。对校时的要求是,在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。需要注意的时,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,为防止这一情况的发生我在原本接校时脉冲的端口接到了实验装置的“单次脉冲”端口,这样既时限内了防抖动,又可以利用手动操作来完成校时。

校时电路图

(四)整点报时电路

数字钟整点报时是最基本的功能之一。实验要求的是在离整点差10秒时,每隔一秒鸣叫一次,每次持续时间为一秒,共响5次,前4次为低音500Hz,最后一声为高音1000Hz。整点报时电路如图6所示。

整点报时电路主要由控制门电路和音响电路两部分组成。

1、控制门电路部分:

由11个与非门组成。图中与非门的输入信号Q4、Q3、Q2、Q1、分别表示“分十位”、“分个位”、“秒十位”、“秒个位”的状态,下标中的D、C、B、A分别表示组成计数器的四个触发器的状态。

由上图可以看出:

Y1=QC4*QA4*QD3*QA3

Y2=Y1*QC2*QA 2

以上二式表示当分十位为5(即QC4QA4=101)、分个位为9(即QD3QA3=1001)、秒十位为5(即QC2QA2=101)时,即59分50秒时发出控制信号。

根据设计要求,数字钟电路要求在59分51秒、53秒、55秒、59秒时各鸣叫一次。

当计数器达到59分50秒时,分、秒计数器的状态为:

QD4QC4QB4QA4=0101(分十位)

QD3QC3QB3QA3=1001(分个位)

QD2QC2QB2QA2=0101(秒十位)

QD1QC1QB1QA1=0000(秒个位)

前四声计数器状态发生在59分51秒至59分58秒之间。因此,只有秒个位的状态发生变化,而其他计数器的状态无需变化,所以可保持不变。

此时 QC4=QA4=QD3=QA3=QC2=QA2=1不变,将它们相与即得Y2。

而51秒、53秒、55秒、57,59秒时的秒计数器个位状态分别为

QD1QC1QB1QA1=0001(51秒)

QD1QC1QB1QA1=0011(53秒)

QD1QC1QB1QA1=0101(55秒)

QD1QC1QB1QA1=0111(57秒)

并根据需要,前四声为低,则接如500Hz的脉冲信号。

最后一声的各计数器状态分别如下:

QD4QC4QB4QA4=0000(分十位)

QD3QC3QB3QA3=0000(分个位)

QD2QC2QB2QA2=0000(秒十位)

QD1QC1QB1QA1=0000(秒个位)

即只须将分进位信号和1KHz的脉冲信号接入即可。如图4-2-4所示

如图4-2-4所示(图中报警器用指示灯来表示)

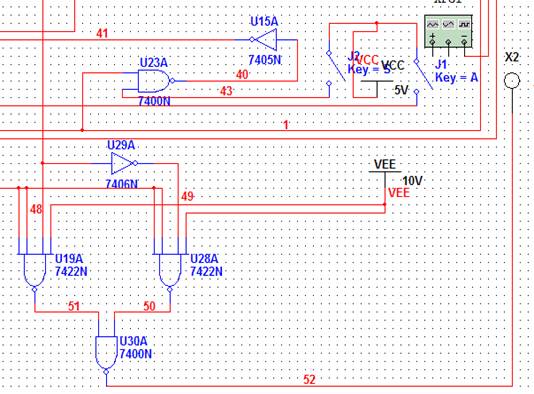

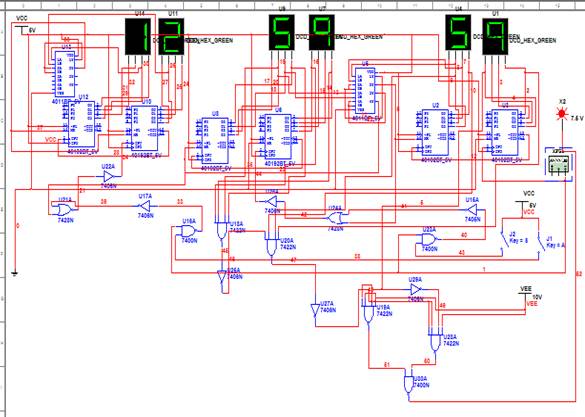

3.6数字电子钟电路图

3.7数字电子钟的组装与调试

由图中所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以增加多级逻辑门来延时。如果显示字符变化很快,模糊不清,可能是由于电源电流的跳变引起的,可在集成电路器件的电源端Vcc加退藕滤波电容。通常用几十微法的大电容与0.01μF的小电容相并联。

4.实验结论

通过运用数字集成电路设计的24小时制的数字电子时钟,经过试验,成功实现了一下基本功能:

1. 能准确计时,以数字形式显示时、分、秒的时间。

2. 能实现整点报时的功能,并分别在51秒、53秒、55秒、57秒、59秒实现了“四短一长”的报时效果。

3. 能定时控制,且能惊醒校正时间(通过开关调时、分)。

5 .实验心得

通过这次数字电子钟的课程设计,我们才把学到的东西与实践相结合。从中对我们学的知识有了更进一步的理解,而且更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。也锻炼了自己独立思考问题的能力和通过查看相关资料来解决问题的习惯。虽然这只是一次简单的课程设计,但通过这次课程设计我们了解了课程设计的一般步骤,和设计中应注意的问题。设计本身并不是有很重要的意义,而是同学们对待问题时的态度和处理事情的能力。各个芯片能够完成什么样的功能,使用芯片时应该注意那些要点。同一个电路可以用那些芯片实现,各个芯片实现同一个功能的区别。

另外,我还渐渐熟悉了mutisim这个仿真软件的各个功能,让我体会到了期中的乐趣,还在电脑制作文档的过程中,使我对办公软件有了更进一步的了解和掌握。

参考文献

1. 现代数字电路与逻辑设计 清华大学出版社 北京交通大学出版社.

2. 模拟电子技术(修订版) 清华大学出版社 北京交通大学出版社

3. 模拟电子技术教程 电子工业出版社

5. 朱定华主编.电子电路测试与实验.北京:清华大学出版社,2004.