七彩装饰灯控制电路

一 设计任务

1.1设计目的和意义

1.1.1目的

本课题的设计目的:

1.掌握电子系统的设计和分析方法,能进行独立的电子系统设计,并掌握其设计基本方法在实践中的综合运用,掌握电路设计的基本方法、步骤,培养综合设计与调试能力,提高分析和解决实际问题的能力。

2. 学习基本的逻辑电路的设计方法,通过器件选择、电路仿真模拟、电路搭建等,增强实际动手操作能力,将理论与实际联系起来,更深刻的理解理论知识。

1.1.2意义

课程设计是培养学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过程.随着科学技术发展的日新日异,数字电子技术已经成为当今计算机应用中空前活跃的领域, 在生活中可以说得是无处不在。因此作为二十一世纪的大学来说掌握数字电子技术是十分重要的。而课程设计是深入学习,真正掌握数字电子技术的有效途径:

1、有利于基础知识的理解

通过《数字电子技术基础》的学习,掌握了数字技术基础知识和基本技能,具备了在日常生活与学习中应用数字技术解决问题的基本态度与基本能力。但是,对于器件选择、电路仿真模拟、电路搭建等知识内容的理解比较肤浅。通过课程设计就能真正理解,从而进一步加强理论知识的学习。

2、有利于逻辑思维的锻炼

在常规的理论学习中,我们的思维常常处于混乱的状态。写起作文来前言不搭后语,解起数学题来步骤混乱,这些都是缺乏思维训练的结果。课程设计是公认的、最能直接有效地训练创新思维,培养分析问题、解决问题能力的途径之一。整个设计过程都需要有条理地构思,中间有判断推理的抽象思维训练,也有分析问题、解决问题、预测目标等能力的培养。

3、有利于与其他学科的整合

在课程设计设计中,我们会遇到与模拟电子技术、电路分析等相关问题,通过课程设计可以加强各门相关课程之间的联系和学习,可谓一举两得。

4、有利于治学态度的培养。

在课程设计中,会遇到各种问题和困难,可能要通过几次乃至十多次的反复修改、调试,才能成功,但这种现象会随着学习的深入而慢慢改观。可以培养严谨治学、一丝不苟的科学精神和不怕失败、百折不挠的品格。

1.2初始参数和要求

设计要求:

采用中规模集成电路设计七彩装饰灯控制电路,彩灯要有3~12种不同的颜色颜色,彩灯的状态可调可编程,颜色和流水的方式自己设定,但要求有多种状态,如正向流水循环点亮、逆向流水逐次熄灭以及彩灯同时亮、同时灭等状态。

二 系统设计

2.1系统工作原理

2.1.1 设计思路

对于这个设计题目,我首先分析了整个电路系统要求实现的逻辑功能,初步拟定了下列三种设计方案:

方案一:利用计数器搭接分频电路,利用计数器控制循环时间,利用译码器实现彩灯的控制,有正向流水循环效果和逆向流水循环效果,而利用单稳态触发器控制灯实现同时灭的状态控制。但是此方案难以实现彩灯同时亮状态,设计要求不能完全实现不够完善。

方案二:采用MCS8051单片机以及晶振电路,用编程的方法实现彩灯的状态控制,彩灯的状态可以有更多流水状态,包括奇偶数灯的亮灭,每个灯的亮灭时间控制等均可以容易的实现,但是,此方案在数电课程设计的范围内显得有些简单,且不符合课程内容形式,故也给予否决。

方案三:采用74LS161搭接成2、4、8、16分频器电路,采用双向循环移位寄存器来实现彩灯的正向流水循环和逆向流水循环控制,信号源用555定时器搭接成多谐振荡器来产生时钟信号,本设计中暂定8路彩灯(实际中可根据具体的情况增加或减少彩灯数量),需要8路双向移位寄存器,为此可使用74LS198来实现,而移位寄存器的状态由74LS161搭接成从01、10、11循环的模为3的计数器电路来控制实现。整个设计思路可以较好的实现设计要求。

2.1.2系统原理框图

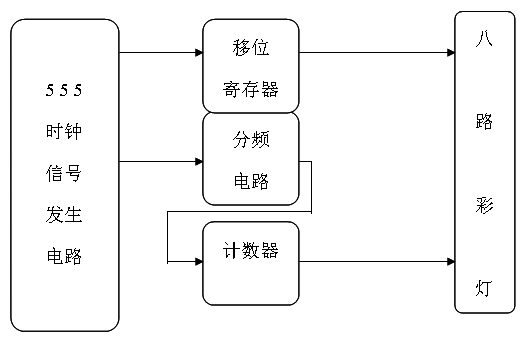

经过以上的对比分析,最终确定的方案三,主要由时钟信号发生电路、分频电路、计数电路、移位寄存器电路以及八路彩灯构成。时钟信号采用555定时器来产生,分频电路和计数电路可分别由74LS161来搭接,移位寄存器电路可由一片74LS198来实现,也可由两片74LS194级联来实现。系统原理框图如下图1所示:

图1 系统原理框图

2.2器件选择

74LS系列中规模集成电路是现代TTL类型中的应用产品,是逻辑IC的重点产品之一,品种丰富,价格低廉,电路的速度高,而且学习和实验过程中对这一系列器件比较熟悉,故本设计中主要选择74LS系列的中规模集成芯片来实现七彩装饰灯的控制电路。

为此,选用两片74LS161,两片74LS194,一片555定时器,八路不同颜色的彩灯作为此次设计的主要元器件。各个芯片的原理及功能简介如下:

2.2.1 74LS194

一个触发器能存储一位二进制数,n位二进制数则需n个触发器来存储。当n位数据同时出现时称为并行数据,而n位数据按时间先后一位一位出现时称为串行数据。串行数据需要一个时钟信号来分辨每一个数据位。用n个触发器组成的n位移位寄存器可以用来寄存n位串行数据,可以实现串行数据到并行数据的转换,也可实现并行数据到串行数据的转换。

在寄存器中存储的数据由低位向高位移动一位时,即数据右移,例如二进数0011向高位移动一位变成0110,二进制数由3变为6。同理,数据由高位向低位移动称为左移,左移一位,数据相当于除2。因此移位寄存器有左移寄存器和右移寄存器之分。也有可逆移位寄存器,即在控制信号作用下,既可实行右移,也可实行左移。

74LS194移位寄存器的控制输入端S1和S0是用来进行移位方向控制的,S0为高电平时,移位寄存器处于向左移位的工作状态,二进制数码在CP脉冲的控制下由高到低逐位移入寄存器,因此可以实现串行输入;在S1为低电平时,移位寄存器处于向右移位的工作状态,二进制数码在CP脉冲的控制下逐位移出寄存器(低位在前,高位在后)。

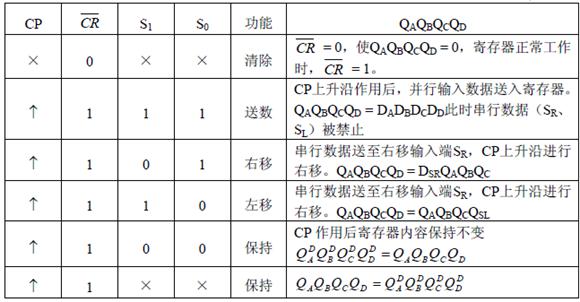

74LS194的功能表

图2 74LS194的内部逻辑图和时序图

图3 74LS194外部引脚图及仿真软件中的逻辑图

由以上功能表和时序图可知74LS194功能有如下功能:

当RD=1,CP=0,无论有无输入数据信号,各触发器保持原状态不变。

当RD=1,S1S0=00,无CP脉冲输人,各触发器保持原状态不变。

当RD=1时,根据控制信号S1S0的4种不同取值组合,在CP脉冲作用下,

实现4种不同的操作:

S1S0=00,各触发器保持原状态不变;

S1S0=01,右移串行送数功能;

S1S0=10,左移串行送数功能;

S1S0=11,并行输入,即CP上升沿可将加在输人端A、B、C、D的数码QA、QB、QC、QD送入寄存器中。

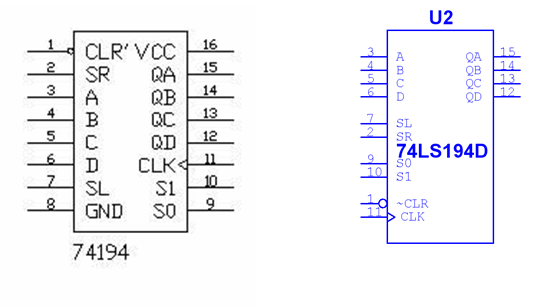

本设计中采用两片74LS194级联实用,可以实现连接八盏彩灯,当然可以进行三片、四片甚至更多的级联,以实现更多的彩灯控制。

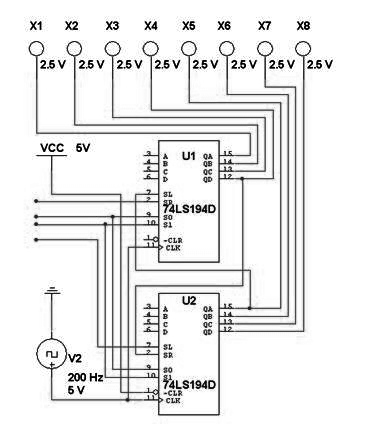

图4 两片74LS194级联

图4 两片74LS194级联

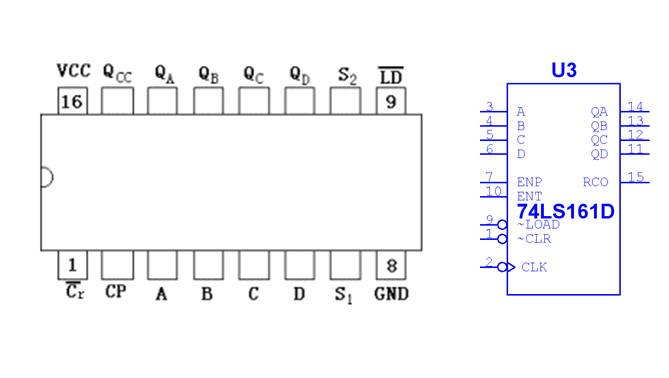

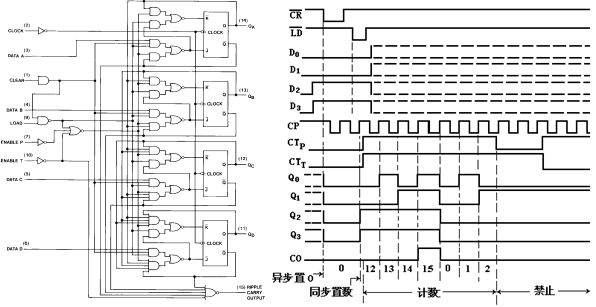

2.2.2 74LS161

模为16,4 位二进制同步计数器(异步清除)161 为可预置的 4 位二进制同步计数器, 161 的清除端是异步的。当清除端 CLk 为低电平时,不管时钟端 CLK 状态如何,即可完成清除功能。161 的预置是同步的。当置入控制器 LOAD 为低电平时,在 CLK上升沿作用下,输出端 QA-QD 与数据输入端 A-D 相一致。当 CLK 由低至高跳变或跳变前,如果计数控制端 ENP、ENT 为高电平,则 LOAD 应避免由低至高电平的跳变.161 的计数是同步的,靠 CLK 同时加在四个触发器上而实现的。当 ENP、ENT 均为高电平时,在 CLK 上升沿作用下 QA-QD 同时变化,从而消除了异步计数器中出现的计数尖峰。161 有超前进位功能。当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为 QA 的高电平部分。在不外加门电路的情况下,可级联成 N 位同步计数器。在 CLk 出现前,即使 ENP、ENT、CLR 发生变化,电路的功能也不受影响。在此给出74LS161的引脚排列以及管脚功能:

图5 74LS161外引线排列图及逻辑符号

图6 74LS161的内部逻辑及时序图

由此可知,74161具有以下功能。

异步清零。CLR=0时,计数器输出被直接清零,与其他输入端的状态无关。

同步并行预置数。在CLR=1条件下,当LOAD=0且有时钟脉冲CP的上升沿作用时,A3、A2、A1、A0输入端的数据 A、B、C、D将分别被QA、QB、QC、QD所接收。

保持。在LOAD=1条件下,当ET·EP=0,不管有无CP脉冲作用,计数器都将保持原有状态不变。需要说明的是,当EP=0,ET=1时,进位输出RCO也保持不变;而当ET=0时,不管EP状态如何,进位输出RCO=0。

计数。当CLR=LOAD=EP=ET=1时,74161处于计数状态。

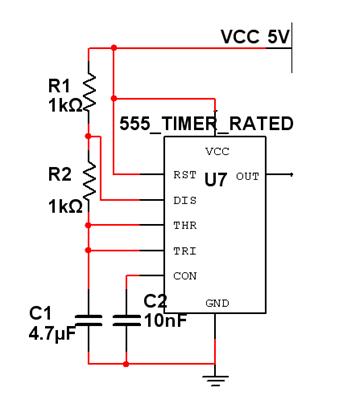

2.2.3 555定时器

555 定时器是一种模拟和数字功能相结合的中规模集成器件。555 定时器性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。555 定时器的内部电路框图和外引脚排列图分别如下图所示。它内部包括两个电压比较器,三个等值串联电阻,一个 RS 触发器,一个放电管 T 及功率输出级。它提供两个基准电压VCC /3 和 2VCC /3

图7 555 定时器的内部电路框图和外引脚排列图

555 定时器的功能主要由两个比较器决定。两个比较器的输出电压控制 RS 触发器和放电管的状态。在电源与地之间加上电压,当 5 脚悬空时,则电压比较器 C1 的同相输入端的电压为 2VCC /3,C2 的反相输入端的电压为VCC /3。若触发输入端 TR 的电压小于VCC /3,则比较器 C2 的输出为 0,可使 RS 触发器置 1,使输出端 OUT=1。如果阈值输入端 TH 的电压大于 2VCC/3,同时 TR 端的电压大于VCC 1/3,则 C1 的输出为 0,C2 的输出为 1,可将 RS 触发器置 0,使输出为低电平。

555的应用:

(1)构成施密特触发器,用于TTL系统的接口,整形电路或脉冲鉴幅等;

(2)构成单稳态触发器,用于定时延时整形及一些定时开关中。

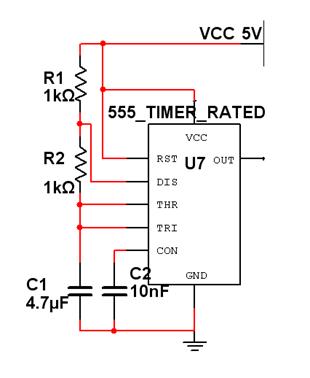

(3)构成多谐振荡器,组成信号产生电路;电路图如下:

R1、R2、C1为定时元件,C2的作用是防止干扰电压对电路的影响。

振荡周期:T=0.7(R1+2R2)Cln2

占空比: D= (R1+R2)/(R1+2R2)

占空比: D= (R1+R2)/(R1+2R2)

图8 555构成多谐振荡器

2.2.4 元器件清单

2.3电路设计

整个电路由4个模块构成:分别为信号发生电路、移位寄存器电路、分频器电路和计数器电路。时钟信号采用555定时器来产生,分频电路和计数电路可分别由74LS161来搭接,移位寄存器电路可由一片74LS198来实现,也可由两片74LS194级联来实现。

2.3.1 信号发生电路

基本原理是,当接通电源后,由于电容两端的电压不能突变,定时器的2端低触发端为低电平,输出端3端为高电平。电源经过R1、R2给电容冲电,当电容电压充电到电源电压的2/3时,555内部的MOS管道通,输出为低电平。电容通过R2和MOS管放电,当电容电压下降到电源电压的1/3时,MOS管截止,电容放电停止,电源经过R1、R2再次给电容冲电,如此反复形成震荡。R1、R2、C1为定时元件,C2的作用是防止干扰电压对电路的影响。

振荡周期: T=0.7(R1+2R2)Cln2

占空比: D= (R1+R2)/(R1+2R2)

占空比: D= (R1+R2)/(R1+2R2)

图9 信号发生电路图

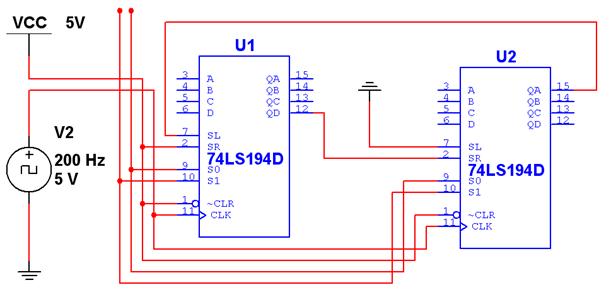

2.3.1 移位寄存器电路

因为仿真软件中没有最初设计的八位双向移位寄存器74LS198器件,故采用两片双向移位寄存器74LS194级联来代替。

寄存器电路是控制彩灯各种状态的核心部件,由前面的器件原理介绍可知,当S1S0为11时,则在时钟脉冲作用下置入预先设置的2分频脉冲,实现彩灯的同时亮、同时灭的状态;S1S0为01时,将依次实现彩灯的右移具有正向流水循环效果;S1S0为10时,将依次实现彩灯的左移状态具有逆向流水循环效果。移位寄存器电路如下图10所示:

图10 移位寄存器电路图

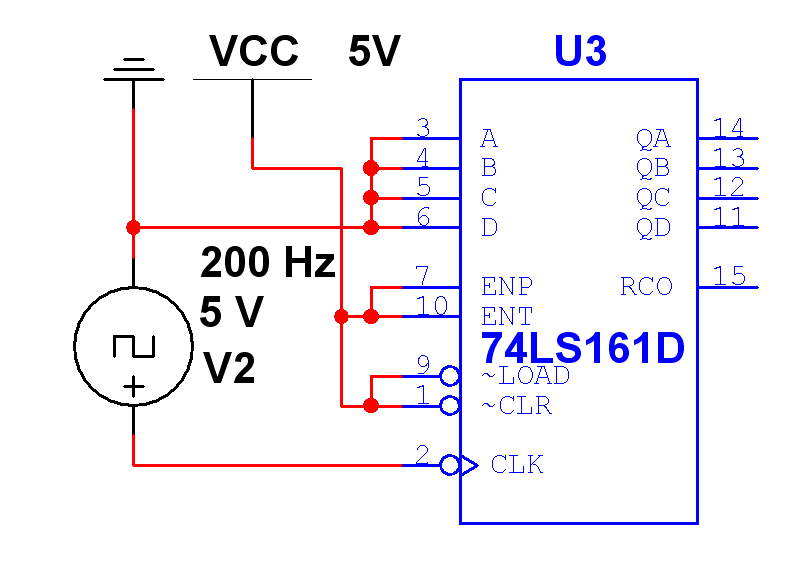

2.3.2分频器电路

分频器电路由74LS161搭接而成,其原理已在前面的元器件原理介绍中做了说明。在本设计中,使用2、8分频输出端,故只需接出QA、QC即可,而EP、ET及清零端CLR接逻辑高电平,输入端A、B、C、D均接逻辑0,设计中直接与参考地相接,时钟脉冲信号选用5V电压脉冲,为了保证高电平的有效性,本设计中直接与+5V电源相接。电路图如下图11所示:

图11 频器电路图

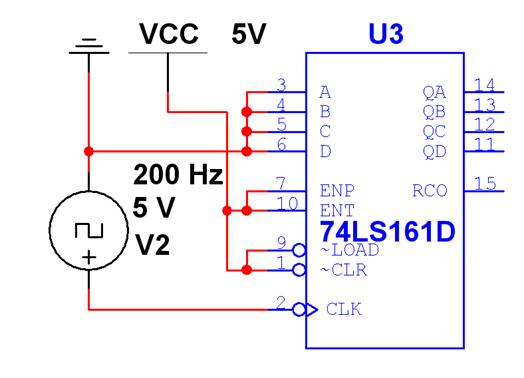

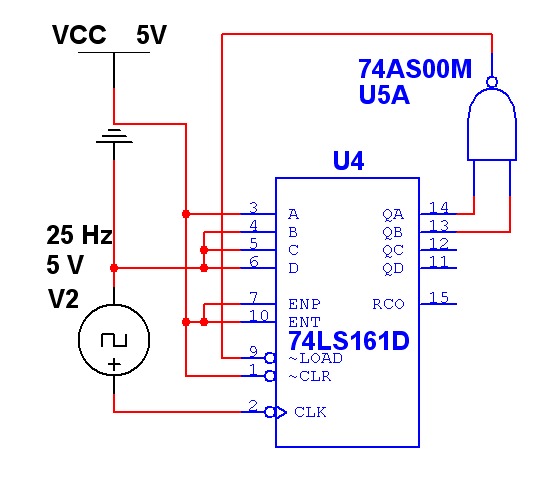

2.3.3 计数器电路

本设计的的巧妙之处在于用计数器QA、QB的3个输出状态01、10、11分别控制移位寄存器的左移、右移以及输出所置脉冲,故将74LS161采用置数法接成模为3的计数器。根据设计思路,八路彩灯每循环一个节拍需要原时钟信号的1/8分频,故计数器电路的时钟信号是经过分频器分频后的8分频信号,输入端A、B、C、D分别接逻辑“1、0、0、0”,而输出端只采用QA、QB,共计3个状态01、10、11,并且当QA、QB为11

时,经过与非门接入置数端进行置数,一直循环下去。QA、QB的01、10、11状态分别与移位寄存器74LS194的控制端S0、S1相接以控制移位寄存器的工作状态,实现左移、右移以及同时亮、同时灭的效果。电路图如下图12所示:

图12 计数电路图

2.3.4 系统总体电路

经过以上分析和各部分电路的设计,将系统整体电路图搭接起来,得到系统整体电路图如下图13所示:

图13 系统整体电路图

2.4电路仿真测试

2.4.1信号发生电路的测试

按图搭接好信号发生电路,将输出端Out接示波器,进行仿真观察。测试过程中观察到示波器显示输出为稳定的脉冲信号,由此可知信号发生电路工作正常,可以进行后续测试。

2.4.1 分频电路的测试

将分频电路搭接好,输出端接四综示波器,对应接入分频器的输出端QA、QB、QC、QD,进行仿真测试,查看输出波形图,有图形可知,各输出端口的时钟脉冲信号的周期一次是原时钟信号的2、4、8、16倍,即实现了2、4、8、16分频,说明分频电路是正确的,可以进行后续测试。

2.4.1 计数电路的测试

将计数电路搭接好,与非门的输出端以及输出端QA、QB各接一个2.5V的指示灯,进行仿真测试。仿真测试时,观察到QA、QB共01、10、11三个状态,并且当QA、QB为11时,与非门指示灯立刻熄灭,即变为逻辑0,然后进行置数,循环重新开始。由以上仿真结果可知,计数器电路工作正常,可以进行后续测试。

2.4.1 移位电路的测试

将移位电路及彩灯搭接完成,接入时钟信号脉冲源,SL接地,SR接+5V电源,分别改变S0、S1为01、10、11观察仿真结果。仿真的现象为,当S0、S1为01时,8路彩灯从左至右依次点亮,当S0、S1为10时,8路彩灯从右至左依次点亮,当S0、S1为11时,8路彩灯同时亮、同时灭。由以上结果可知,移位电路正常工作,可以进行后续测试。

2.4.1 整体电路的测试

采用系统整体电路进行仿真试验,观察是否与设计相符。仿真进行时,彩灯状态有正向流水循环点亮、逆向流水逐次熄灭以及彩灯同时亮、同时灭的状态,并且改变分频器的输出端口可以实现彩灯状态的变化。此外还可以通过改变时钟信号发生电路的个别引线实现彩灯状态的变化。

由以上仿真测试可知,整体电路工作正常,达到了设计要求。

三 总 结

3.1结论

经过以上仿真试验,发现移位寄存器电路、分频器电路和计数器电路以及系统整体电路均正常工作,彩灯状态有正向流水循环点亮、逆向流水逐次熄灭以及彩灯同时亮、同时灭的状态,并且改变分频器的输出端口可以实现彩灯状态的变化。此外还可以通过改变时钟信号发生电路的个别引线实现彩灯状态的变化。

结论:所设计的七彩装饰灯控制电路符合设计要求。

3.2优点与不足

本设计的优点与创新点:

第一,本次设计尝试了移位寄存器74LS194的级联使用,掌握了级联方法,并且级联的数目不受限制,因此,可以增加彩灯的数目,作为真正的装饰产品。

第二,此次彩灯控制电路的设计功能比较齐全,可以实现正向循环、逆向循环以及同时亮、同时灭多种状态。

第三,彩灯进行状态改变的全过程所用时间可调,彩灯状态可改变,每个节拍的时间,每个节拍的循环次数均可进行设置,只需选择不同的分频接口输出端即可。

不足之处:

此次设计中,彩灯的状态比较少,如不能控制彩灯的奇偶数亮灭及单个彩灯的延时等。

3.3 心得与体会

第一,通过此课题的设计训练,让我亲身经历了从无到有,从不可能到可能的电路设计仿真的整个过程,经历了很多困难和挫折。在设计过程中,经常会遇到不同的问题,理论上分析可行,但进行电路仿真时却得不到预期效果。在设计的过程中发现自己对以前所学过的知识理解得不够深刻,掌握得不够牢固,需要查阅相关关资料,通过这个过程使我懂得了许多东西,也培养了我独立工作的能力,树立了对自己工作能力的信心,相信会对今后的学习工作生活有非常重要的影响。

第二,通过这样的经历,我懂得了学习的重要性,了解到理论知识与实践相结合的重要意义,锻炼了能力,综合素质得到较大提高,尤其是观察、分析和解决问题的实际工作能力,另外加强了我们动手能力的锻炼,培养了我们发现问题,思考问题,解决问题的能力。在以后的学习生活中,我们将更加积极主动的参加各次动手能力锻炼,为将来自身的发展奠定坚实的基础。

第三,通过此次课程设计,让我们找出自身状况与实际需要的差距,并在以后的学习期间及时补充相关知识,为求职与正式工作做好充分的知识、能力准备,从而缩短从校园走向社会的心理转型期。课程设计使我们普遍感到不仅实际动手能力有所提高,更重要的是通过对数字电子技术有了更深入的了解,进一步激发了我们对专业知识的兴趣,并能够结合实际存在的问题在专业领域内进行更深入的学习。

第四,挫折是一份财富,经历是一份拥有。知识上的收获重要,精神上的丰收更加可喜。其实生活就是这样,汗水预示着结果也见证着收获。劳动是人类生存生活永恒不变的话题。设计确实有些辛苦,确实很累,但当我们看到自己所做的成果时,心中也不免产生兴奋,沿着自己的路,执着的走下去,必将成为我人生旅途上一个非常美好的回忆!

参考文献

[1] 阎石.数字电子技术基础.第五版.高等教育出版社出版.

[2] 宋涛.通用集成电路速查手册.第二版.山东科学技术出版社.

[3] 康华光.电子技术基础(数字部分)第五版.高等教育出版社.

[4] 韩广兴.电子元器件与实用电路基础.修订版.电子工业出版社.

[5] 路勇.电子电路实验及仿真.清华大学出版社