EDA技术及应用实验

实验指导书

汕头大学电子工程系

20##年9月

实验一 EDA软件的熟悉与使用

一、实验目的

1. 学习并熟悉ALTERA公司CPLD/FPGA设计开发系统MAX+PLUS II 10.2的使用。

2. 认识并熟悉ZY11EDA13BE型EDA技术实验开发系统。

3. 了解实验系统核心芯片EP1K30QC208的性能和特点。

4. 掌握采用MAX+PLUS II 10.2进行设计项目开发的整个流程。

5. 初步掌握基于CPLD/FPGA的VDHL设计。

二、硬件要求

1、 拨位开关。

2、 FPGA主芯片:EP1K30QC208。

3、 LED显示模块。

三、实验原理

四,实验内容与步骤

1. 根据电脑桌面“ZY11EDA13BE实验箱简介课件”的内容介绍,熟悉实验箱的结构与组成。

2. 根据电脑桌面“MAX+PLUS II 10.2学习课件”的内容介绍,熟悉CPLD/FPGA设计开发系统MAX+PLUS II 10.2的使用。

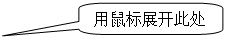

3. 掌握MAX+PLUS II 10.2的设计开发流程。

4. 实验VHDL语言设计编写8位全加器。

5.在实验箱上验证自己所设计全加器的逻辑功能。

五、实验报告要求

1、本实验的目的和实验内容。

2、实验中用到的主要仪器设备。

3、绘制出MAX+PLUS II 10.2进行一个设计项目的详细流程图。

实验二 组合逻辑电路的VHDL模型实验

一、实验目的:

1、 掌握组合逻辑和时序逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

3、 了解通用同步计数器,异步计数器的使用方法。

4、 理解积分分频器的原理。

二、硬件要求

1、拨位开关。

2、FPGA主芯片:EP1K30QC208。

3、LED显示模块。

三、实验原理

译码器是输入数码和输出数码之间的对应关系,也就是说,“输入码和输出码之间的对应表”这应该算是设计译码器的必须条件。

译码器常用来做码和码之间的转换器,也常被用于地址总线或用作电路的控制线。

例如下面为常见的3×8译码器的真值表:

实验中可根据需要,为3×8译码器加入使能控制脚。

一般的分频器可获得的分频频率种类分布不均匀,积分分频,能比较好的解决这个问题。

1、分频结果=来源频率×N/(2?-1);

2、频率波形不均匀。

四、实验内容及步骤

本实验内容是完成38译码器和5/8分频器的设计,然后将3×8译码器的结果在实验箱上实现,5/8分频器则能正确仿真、显示,实验步骤如下:

1、编写3×8译码器的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在开关输入键值,观看实验结果。

7、编写5/8分频器的VHDL代码。

8、用MaxPlusII对其进行编译仿真。

9、使用WaveForm进行波形仿真。

五、实验报告要求

1. 写明实验目的和内容。

2. MaxPlusII仿真波形图。

3. 实验中用到的主要仪器设备。

4. 记录实验内容的实验观察结果。

5. 请学生思考:如果要设计7/8分频器,需要如果进行改动?总结设计方法。

实验三 时序逻辑电路的VHDL模型实验

一、实验目的

1、 了解普通4×4键盘扫描的原理。

2、 掌握组合逻辑电路和时序逻辑电路的混和设计。

3、 进一步加深七段码管显示过程的理解。

二、硬件要求

1、4×4键盘阵列。

2、FPGA主芯片。

3、可变时钟源。

4、七段码显示区。

5、LED显示模块。

三、实验原理

本实验主要完成的实验是完成4×4键盘扫描的,然后获取其键值,并对其进行编码,从而进行按键的识别,并将相应的按键值进行显示。

键盘扫描的实现过程如下:对于4×4键盘,通常连接为4行、4列,因此要识别按键,只需要知道是哪一行和哪一列即可,为了完成这一识别过程,我们的思想是,首先固定输出4行为高电平,然后输出4列为低电平,在读入输出的4行的值,通常高电平会被低电平拉低,如果读入的4行均为高电平,那么肯定没有按键按下,否则,如果读入的4行有一位为低电平,那么对应的该行肯定有一个按键按下,这样便可以获取到按键的行值。同理,获取列值也是如此,先输出4列为高电平,然后在输出4行为低电平,再读入列值,如果其中有哪一位为低电平,那么肯定对应的那一列有按键按下。

获取到行值和列值以后,组合成一个8位的数据,根据实现不同的编码在对每个按键进行匹配,找到键值后在7段码管和LED显示。

四、实验内容及步骤

本实验内容是完成4×4键盘的扫描,然后将正确的键值进行显示,实验步骤如下:

1、编写键盘扫描和显示的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在4×4键盘输入键值,观看实验结果。

五、实验报告要求

1、 写明实验目的。

2、 总结FPGA是如何识别按键的?与单片机读取键值有何不同?

3、 在深入理解了4×4键盘实现的原理基础上,试试利用VHDL在目标器件FPGA/CPLD上实现PS/2键盘接口。

4、 比较4×4键盘与PS/2键盘接口用FPGA实现方法的异同点。

实验四 有限状态机的设计——0809 A/D转换实验

一、实验目的

1、 了解ADC0809的工作原理。

2、 了解用扫描方式驱动七段码管显示的工作原理。

3、 了解时序电路FPGA的实现。

4、 学习用VHDL语言来描述时序电路的过程。

二、硬件要求

1、 可变时钟源。

2、 七段码显示。

3、 A/D转换芯片ADC0809

4、  主芯片ACEX1K EP1K30QC208。

主芯片ACEX1K EP1K30QC208。

5、 三个拨动开关,进行地址选择。

三、实验原理

该实验是利用FPGA控制ADC0809的时序,进行AD转换,然后将ADC0809转换后的数据以十六进制的数据显示出来。

ADC0809是8位8通道的逐次比较式AD转换芯片。该芯片管脚如右图所示。芯片引脚及其说明如下:

D0-D7(2-8-2-1):8位双先三态数据线。

ADDA、ADDB、ADDC:通道选择地址。

OUTPUT ENABLE:输出允许控制。

Clock:ADC转换时钟。

Vref+、Vref-:正负参考电压。

IN0-IN7:8个模拟信号输入通道。

START:AD转换启动信号。

EOC:AD转换结束信号。

ALE:通道地址锁存信号。

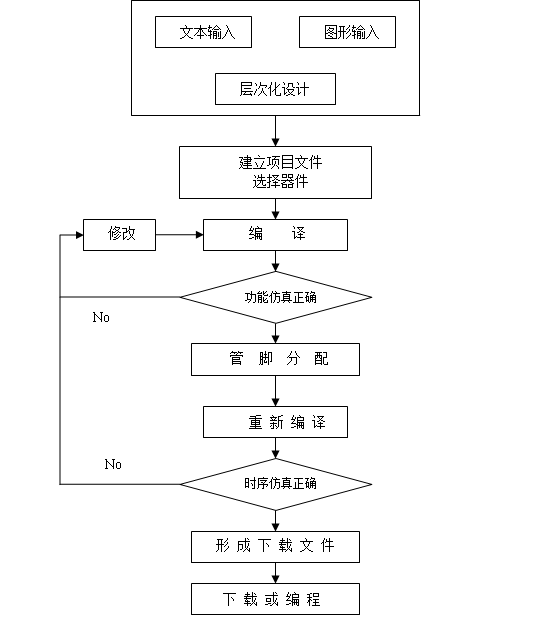

ADC0809的工作时序如下图所示。其详细工作过程可查阅其他资料。

本实验FPGA实现时必须严格遵守ADC0809的工作时序,在编写其驱动代码时尤其要注意。ADC0809的时钟信号从FPGA获取,FPGA的时钟在500KHz至800KHz都可以选择。现具体介绍代码编写思想:

首先将要转换的ADC0809的地址输出,然后产生ALE信号的,在该信号的上升沿,地址被打入ADC0809的地址锁存器,这样就选中了对应的通道。地址产生结束后,便可产生START信号,使ADC0809开始进行AD转换,需要注意的是,在ADC0809转换期间,输入的模拟信号必须稳定,否则可能出现比较大的误差。在地址锁存并且启动转换后,EOC便会呈现低电平,知道AD转换结束,所以FPGA在EOC从低电平变成高电平之前,不能读取ADC的转换数据。在EOC变成高电平之后,FPGA便可将OUTPUT INPUT信号拉高,这样ADC转换的数据就会呈现在数据线上,FPGA读入该数据后,在8位七段码管上显示出来,这就是整个实验过程的工作流程。

四、实验内容及步骤

本实验的内容就是用FPGA模拟产生ADC0809的时序,使其正常工作,对ADC0809输入一个模拟量,进行A/D转换,然后将读入后的数据进行显示,实验步骤如下:

1、 编写ADC0809时序的VHDL代码。

2、 用MaxPlusII对其进行编译仿真。

3、 在时序确定无误后,选择芯片ACEX1K EP1K30QC208。

4、 给芯片进行管脚绑定,在此进行编译。

5、 根据自己绑定的管脚,在实验箱上对ADC0809、显示七段码和FPGA之间进行正确连线。

6、 对选定的通道输入一个模拟量,给目标板下载代码,调节电位器改变输入的模拟量,观看实验结果。

五、实验报告要求

1、 写明实验目的。

2、 MaxPlusII仿真波形图。

3、 对于外部模拟信号Vtest范围超出0~5V的情况下,应如何修改设计和显示模块?

4、 请学生思考:为什么引入CLK信号?用与不用CLK信号对显示可能产生什么影响?

实验五 具有音乐报点的数字钟实验

一、实验目的:

1、 掌握多位计数器相连的设计方法。

2、 掌握十进制、六十进制、二十四进制计数器的设计方法。

3、 继续巩固多位共阴极扫描显示数码管的驱动及编码。

4、 了解和掌握分频电路实现的方法。

5、 掌握扬声器的驱动。

6、 使用FPGA产生不同的音乐频率。

7、 LED 灯的花样显示。

8、 掌握CPLD技术的层次化设计方法。

二、设计要求

1、具有时、分、秒计数显示功能,以24小时循环计时。

2、具有清零,调节小时、分钟功能。

3、具有整点报时功能,整点报时的同时LED灯花样显示。

三、硬件要求:

1、 主芯片ACEX1K EP1K30QC208。

2、 8个LED灯。

3、 扬声器。

4、 8位七段扫描共阴极数码显示管。

5、 三个按键开关(清零,调小时,调分钟)。

四、实验原理:

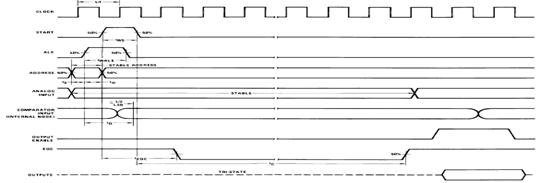

在同一块CPLD芯片EP1K10TC100—3上集成了如下电路模块:

1、 时钟计数:

秒——60进制BCD码计数;

分——60进制BCD码计数;

时——24进制BCD码计数;

同时整个计数器有清零,调分,调时功能。在接近整点时能提供报时信号。

2、 有驱动8位七段共阴极扫描数码管的片选驱动信号输出和七段字行译码输出。编码和扫描可参照“实验四”。

3、 扬声器在整点时有报时乐曲驱动信号产生。

音符的产生:音符的产生是利用计数器对输入的时钟信号进行分频,然后输出不同的频率来控制扬声器发不同的声音。计数器必须是模可变的计数器,也就是其初始计数值可变,这样便可以对其进行初始化,使其从不同的初始值开始计数,实现对输入时钟信号的不同分频。

节拍的产生:节拍也是利用计数器来实现,如果某一个音符需要维持的时间比较长,那么就可以在此计数器从计数值A到计数值B之间都维持该音符,很显然,A和B之间的间隔越大,那么该音符维持的时间也就越长。

乐谱的存储:乐谱是一个固定的组合电路,根据不同的输入值,然后输出一个固定的值,该值就是音符产生计数器的分频的初始值。

适当的选择这些计数器和组合电路,便可完成不同的乐曲和不同节奏。

4、 LED灯按个人要求在整点时有花样显示信号产生。

五、实验内容及步骤:

1、 根据电路特点,可在教师指导下用层次设计概念,将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口。让几个学生分做和调试其中之一,然后再将各模块合起来联试。以培养学生间的合作精神,同时加深层次化设计概念。

2、 了解软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合。

3、用MaxPlusII对其进行编译仿真。

4、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

5、给芯片进行管脚绑定,在此进行编译。

6、根据自己绑定的管脚,在实验箱上对扬声器接口和FPGA之间进行正确连线。

7、给目标板下载代码,观看实验结果。

原理图示

模块说明:

各种进制的计数及时钟控制模块;

扫描分时显示,译码,分频模块;

彩灯,扬声器编码模块;

各模块都是由VHDL语言编写。

六、实验报告

1、 了解乐曲节拍产生的过程,注意每一音符的节拍长短的变化是由什么控制的?

2、 改变时钟频率,看乐曲有什么改变?

3、 熟悉音乐编程的过程,填入新的乐曲。

4、 将两个或多个乐曲演奏电路合二为一,以一开关控制,可选择演奏不同的乐曲。

5、让学生自己体会CPLD整个设计的优点,以及用扫描电路实现显示功能的潜在好处。然后集体讨论,相互加深对CPLD芯片的特点和CPLD设计心得的交流

第二篇:eda实验指导书(选修)

EDA实验指导书

计算机科学与技术学院

计算机系应用教研室

20##-8

目 录

目 录. 2

使用本实验指导书的缺省约定. 3

实验用到的资源和原理. 3

实验1 二输入与门原理图输入设计. 5

实验2 基于VHDL二输入与门设计. 8

实验3 2选1多路选择器VHDL设计. 10

实验4 数控分频器的设计. 11

实验5 5人表决器的设计. 12

实验6 红绿灯控制器设计. 13

实验报告内容. 15

使用本实验指导书的缺省约定

本实验指导书的所有实验均采用软件为Quartus II 5.0,硬件芯片为ALTERA 的Cyclone 系列FPGA芯片EP1C6Q240C8。

实验用到的资源和原理

实验用到的资源包括1:逻辑开关2:发光二极管指示灯3:单脉冲/1M-8M方波时钟

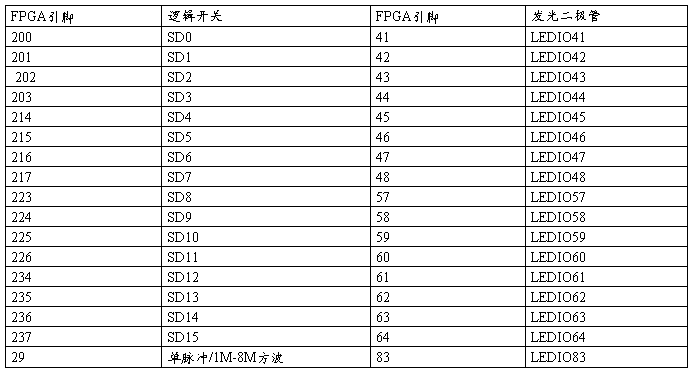

数字逻辑实验需要用到的输入为逻辑0、1,由逻辑开关提供,实验台提供了16个逻辑开关,为SD0、SD1……SD15,和FPGA的连接关系如下表1。输出的逻辑0、1接到发光二极管,实验台提供了很多发光二极管,具体只列了部分于表1-1中。

表1

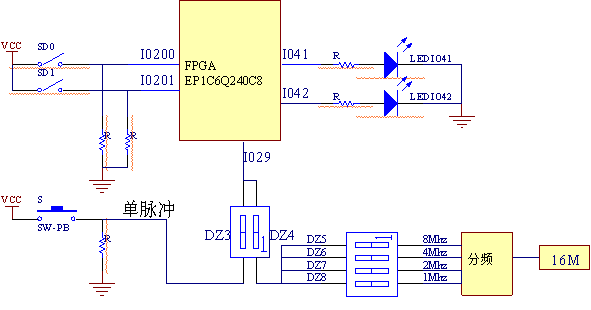

从表中可以看出,SD0连接于200脚,SD1连接于200脚,41脚到83脚分别接有一个发光二极管指示灯。具体原理如下图1所示(只列处了两个逻辑开关和两个发光二极管,其余同理)。通过拨动逻辑开关实现逻辑0、1的输入,输出的逻辑0、1通过发光二极管指示,1亮0灭。

时序电路的实验要用到脉冲和1M-8M方波,由29脚的提供,原理如下图所示。当短路子DZ3短接时,DZ4断开时,29脚和单脉冲(按一下出一个高电平的单脉冲)连接,当DZ4短接时,DZ3断开时,29脚接方波,此时频率由DZ5、DZ65、DZ75、DZ85的短接情况决定。DZ5短接时为8M, DZ6短接时为4M,DZ7短接时为2M,DZ8短接时为1M。

图1

实验1 二输入与门原理图输入设计

1、实验目的

l 通过本实验,理解Quartus II软件工具的使用方法和流程。

l 了解基于原理图设计的方法。

2、实验原理

本实验通过在二输入与门的两个输入加入信号(来自逻辑开关),控制加在二输入与门输出端的LED指示灯的亮和灭,对二输入与门的原理进行验证,从而熟悉和理解Quartus II软件工具的使用方法和流程。LED指示灯和逻辑开关的原理见“实验用到的资源和原理”部分。

3、实验步骤:

1)创建新的Quartus II工程(在创建新工程前,需要创建一个工作目录)

打开File—New Project Wizard菜单,创建工程,并指定芯片为EP1C6Q240C8.

2) 建立顶层模块设计文件(.bdf),选择File->New,选择Block Diagram/Schematic File,按OK。注意:此文件必须与上一步骤的顶层文件名称相同,Save时自动出现顶层文件名称,保持不变。

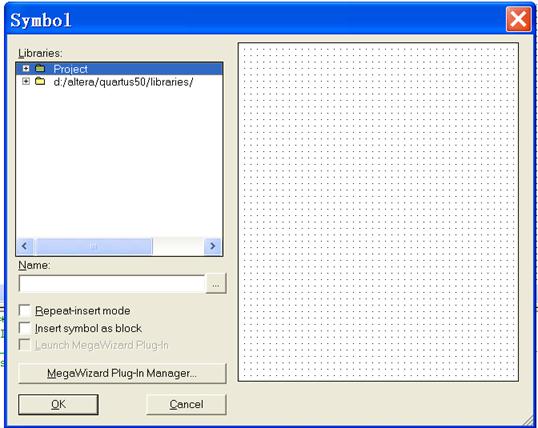

在BDF文件设计窗口内的空白处双击,Symbol对话框出现,选择原件and2,如下图所示:

重新打开Symbol对话框,在Name栏输入input,在BDF设计窗口中放入2个input,将其分别连接到AND2的两个输入端。用同样方法放入一个output,连接到输出端。

3)编译系统。

打开Processing-Start Compilation进行编译。

4)建立向量波形文件(Vector Waveform File):选择File->New,在出现的New窗口中选择Other Files属性页,选中Vector Waveform File,按OK结束,编辑文件,然后保存Vector Waveform File,文件名称必须与顶层文件名相同。

5)仿真。

打开菜单Tools-Simulator Tool进行相应的仿真。

6)引脚锁定

打开Assignments-Pins进行相应的引脚锁定。锁定时参考“实验用到的资源和原理”部分,把输入锁定到逻辑开关,输出锁定到LED发光二极管指示灯。

7)编译系统

8)下载验证

打开Tools-Programmer,Mode选则JTAG,Hareware Setup选择ByteBlaster II,编程文件选择*.sof的文件,即可开始下载。

下载完成后,拨动相应的两个开关,观察LED显示,验证系统工作的正确性。

实验2 基于VHDL二输入与门设计

1、实验目的:通过本实验,理解基于VHDL的硬件设计的基本思想和流程,近一步熟悉Quartus II软件工具的使用方法和流程。

2、实验原理:本实验依然采用逻辑开关、LED指示灯作为输入和输出,具体原理参考实验1的原理部分。

3、实验要求:

1)本实验首先用VHDL语言实现二输入与门,并用仿真和逻辑开关、LED指示灯验证其正确性。

2)把VHDL语言设计出的二输入与门,生成模块图,基于次模块,用原理图设计四输入与门并用并用仿真和逻辑开关、LED指示灯验证其正确性。

4、实验步骤:

参考实验一的步骤,在步骤2)时,采用VHDL file作为输入。其余相同。

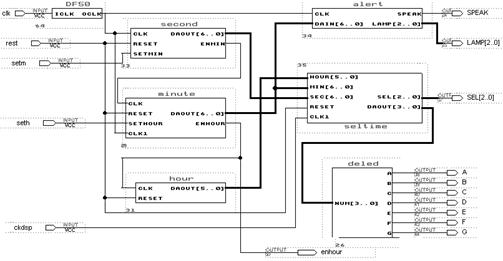

在完成基于VHDL语言实现二输入与门设计和仿真验证之后,打开File—Creat Update—Creat Symbol Files for Current File,从而创建一个自己设计的二输入与门。此后重复和实验1一样的设计步骤,在不关闭当前工程的前提下,首先选择File->New,选择Block Diagram/Schematic File,按OK。出现如下窗口,用鼠标展开Project(如下图标识所示),选中其中的我们设计的二输入与门。此后的设计和实验1步骤完全一致。

实验3 2选1多路选择器VHDL设计

1、实验目的:通过本实验,进一步理解基于VHDL的硬件设计的基本思想和流程,熟悉Quartus II软件工具的使用方法和流程。为接下来的设计打好基础。

2、实验原理:本实验依然采用逻辑开关、LED指示灯作为输入和输出,具体原理参考“实验用到的资源和原理”部分。

3、实验要求:

1)本实验首先用VHDL语言实现2选1多路选择器的设计并仿真;

2)采用三个逻辑开关,其中两个作为数据输入(一个置“1”,一个置“0”)、一个作为选择输入端,输出接到LED指示灯。通过拨动选择输入端,分别选择两路输入(一路为“0”,一路为“1”)到输出,从而实现LED的亮灭控制

4、实验步骤:

参考实验2的VHDL设计部分。

实验4 数控分频器的设计

1、实验目的:学习基于VHDL的数控分频器的设计、分析和测试方法。

2、实验原理:数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比。

3、实验要求:

1)采用实验台提供的8M晶阵作为时钟源(29脚);

2)可以实现2到256分频;

3)具体的VHDL设计程序并仿真 。

4、具体实验步骤和方法自行设计

实验5 5人表决器的设计

1、实验目的:通过5人表决器电路的设计,熟悉和理解基于VHDL的硬件设计,进一步掌握普通组合逻辑电路的设计。

2、实验原理:本实验依然采用逻辑开关、LED指示灯作为输入和输出,具体原理参考“实验用到的资源和原理”部分。

3、实验要求:

1)5人中,有一特权者,只要他否决,即一票否决,在特权者赞成的前提下,多数通过原则,即赞成者>=3即通过

2)采用逻辑开关作为输入,输出接到LED指示灯。

4、具体实验步骤和方法自行设计

实验6 红绿灯控制器设计

1、实验目的:通过一个实际的红绿灯控制系统设计,近一步理解和掌握基于VHDL的硬件设计的方法和优点,从而掌握用VHDL语言设计实际应用系统的能力。

2、实验原理:

本实验需要采用LED指示灯模拟红黄绿交通灯,同时,还要进行倒计时时间的显示,因为本实验台无7段码显示器,故用5个LED指示灯显示倒计时时间的二进制数。

3、实验要求:

1) 系统的整体设计

设计系统的整体模块图,分别说明每个模块的功能。

2)各个模块的设计

给出各个模块的接口和具体的VHDL设计程序并仿真 。

3)整体仿真

4)本实验的具体实现功能要求

南北方向和东西方向的共六个颜色灯(红、黄、绿)按给定延迟时间循环点亮。东西方向通行30妙,南北方向通行20妙。选用5个LED指示灯显示时间(以二进制),进行倒计时。当时间到后,进行红黄绿灯显示切换。

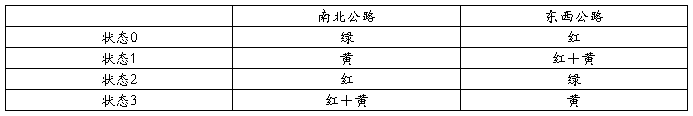

交通灯控制器用一个有限状态机来实现上述功能,它定义了4个状态,见下表:

交通灯控制器的4个状态

交通灯控制器的状态转换图

4、具体实验步骤和方法自行设计

实验报告内容

一般实验(实验1――5)

项目名称

1、 实验目的及要求

2、 实验仪器设备

3、 实验内容

4、 实验实施步骤

5、 仿真结果

6、 设计的VHDL源程序

7、 实验总结

包括实验中遇到的问题,如何解决遇到的问题;实验后的认识和感悟等。

综合性实验(实验6)

项目名称

一、实验内容

二、实验目的及要求

三、实验仪器设备

四、实验实施步骤

五、实验总结