计算机组成原理 预做实验报告

实验四 数据通路的组成

1实验目的和要求

在JYS-4实验装置上模拟计算机最基本的工作过程,打通“键盘”、“CPU”、“RAM”之间的数据通路,掌握计算机的数据通路组成及其工作原理。

2 实验设备

JYS-4计算机组成原理教学实验装置及导线若干。

3实验内容及步骤

1)实验原理

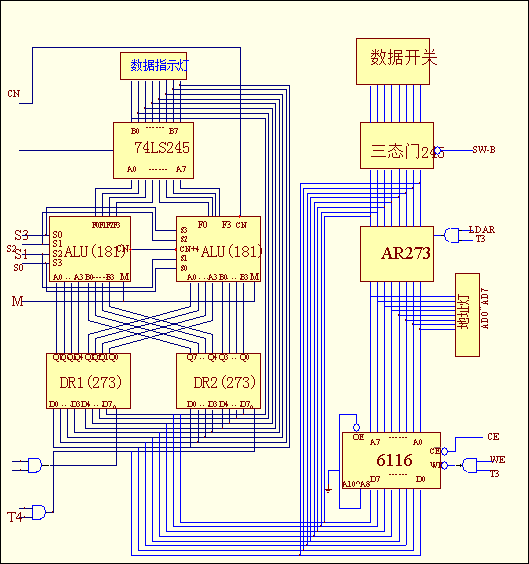

该实验实际是前三个实验的综合,就是把JYS-4实验装置上的INPUT DEVICE(输入设备—键盘)、SWITCH UNIT(开关单元—控制器)、SIGNAL UNIT(信号单元—时钟)、STATE UNIT(时序单元)、ALU UNIT(算术逻辑单元—运算器)、MAIN MEM(主存储器—内存)、ADDRESS UNIT(地址单元)、BUS UNIT(总线单元)、W/R UNIT(写/读单元)、OUTPUT DEVICE(输出设备)等单元电路连接起来,构成一个最基本的计算机系统,以模拟计算机的实际工作过程。电路构成也是运算器实验和存储器实验电路的综合,如实验指导书图4-1。

2)实验步骤

①接线前的准备、实验电路的接线程序参见实验一和实验三。

②从输入单元电路输入四个八位二进制数据,并存入存储器单元(四个数据及四个存放数据的内存单元地址由各组定义,但要求不能 与其它组定义的数据相同)。

③从内存单元取出两组八位二进制分别送入DR1和DR2,并进行四种不同的算术运算,并把不同的算术运算的结果保存在存储器单元里(四种不同的算术运算及其结果的存放地址由各组自行规定)。

④再从内存单元里取出剩下的两个原始数据分别送入DR1和DR2,并进行四种不同的逻辑运算,并把不同的逻辑运算结果存入存储器单元里(要求同3)。

⑤分别从存储器单元读出算术运算和逻辑运算的结果,并进行理论分析其正确性。

图4-1 JYS-4装置的数据通路组成原理

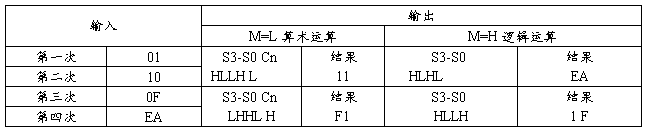

数据通路实验数据记录表

4 实验数据记录与分析

数据通路实验数据记录表

验证分析:实验结果与理论分析相符;

5注意事项

实验中, LDDR1与CE、LDDR2与WE分别共用一个控制开关,在上述两个实验分别做的时候,这两个开关要么用于产生LDDR1和LDDR2(做运算器实验时)这两个控制信号,要么用于产生CE和WE(做存储器实验时)这两个控制信号,所以是不矛盾的。但在本实验里,这四个控制信号都要用到,因而产生了矛盾,为了解决这个问题,在本实验接线时,保持图2-2的接线不变,而将图4-2中存储器单元的片选信号(CE)输入端连接至开关单元里的AR(PC-B)控制端,同时将写存储器控制信号(WE)输入端连接至开关单元里的SWA(LDPC)控制断。如有其他信号冲突,可用类似办法解决。操作时要注意这些接线上的变化。

第二篇:实验四 实验报告表

实验四实验报告表

实验名称:一条指令的执行过程

学号 1120130377 姓名:王旭东 班级: 02031301实验时间: 2013年12月2日

实验报告表4-1 一条指令执行过程记录表