泸州职业技术学院实验报告

第二篇:微电子综合实验报告

微电子综合实验报告

实验题目: 27题spice与非门仿真

班级:电子科学与技术1201

姓名:

学号:

时间: 2015.5—2015.6

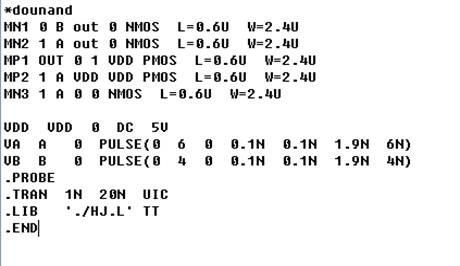

原理图网表如下:

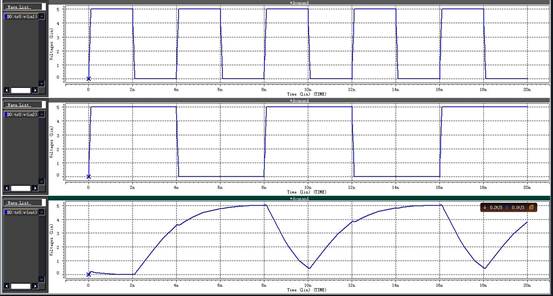

仿真波形图如下:

输出端外加0.01p时,仿真网表为

*dounand

NM1 0 B OUT 0 NMOS L=0.4U W=1.6U

NM2 1 A OUT 0 NMOS L=0.4U W=1.6U

MP1 OUT 0 1 VDD PMOS L=0.4U W=1.6U

MP2 1 A VDD VDD PMOS L=0.4U W=1.6U

MP3 1 A 0 0 NMOS L=0.4U W=1.6U

cloadf OUT 0 0.01p

VDD VDD 0 DC 5V

VA A 0 PULSE(0 6 0 0.1N 1.9N 6N)

VB B 0 PULSE(0 4 0 0.1N 1.9N 4N)

-PROBE

-TRAN 1N 20N UIC

-LIB ‘-/HJ.L’ TI

END

仿真波形图如下:

由波形图可以看出,只要输入有一个低电平,输出就为高电平,满足要求。

输出端外加0.1p时,仿真网表为:

*dounand

NM1 0 B OUT 0 NMOS L=0.2U W=0.8U

NM2 1 A OUT 0 NMOS L=0.2U W=0.8U

MP1 OUT 0 1 VDD PMOS L=0.2U W=0.8U

MP2 1 A VDD VDD PMOS L=0.2U W=0.8U

MP3 1 A 0 0 NMOS L=0.2U W=0.8U

cloadf OUT 0 0.1p

VDD VDD 0 DC 5V

VA A 0 PULSE(0 6 0 0.1N 1.9N 6N)

VB B 0 PULSE(0 4 0 0.1N 1.9N 4N)

-PROBE

-TRAN 1N 20N UIC

-LIB ‘-/HJ.L’ TI

END

电路逻辑表达式Y=AB

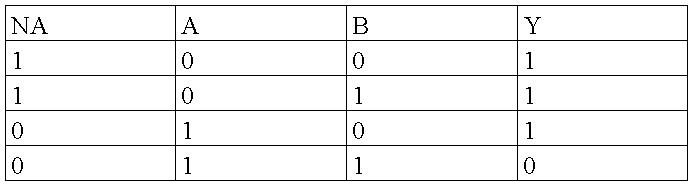

真值表如下:

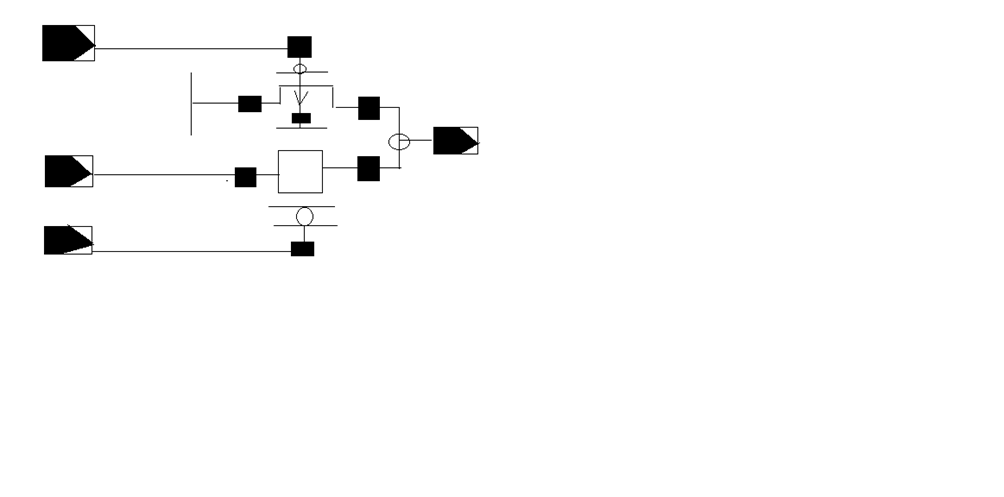

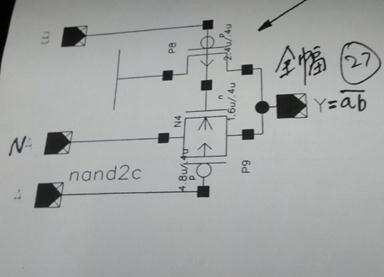

原理图:

综合上述仿真给输入的与非门加5V激励电压, 由上述spice仿真波形图知道,当输入都为1时输出为零,当输入有一个为零时输出为1,实现了与非门的基本逻辑功能.

如下实验原理图:

实验总结

通过这次试验令我初步了解了spice软件的基本的用法,对电路的仿真过程加深了对电路的理解,而通过波形仿真的结果可以知道仿真网表是否正确,从而通过修改网表达到网表与原理图逻辑一致。而通过输出端外加电容可以延迟输出端信号变化。

物理与电子信息学院-微电子综合实验-成绩评定表

专业:电子科学与技术班级:12电子 学号: 姓名: