20##年数字电路本科课程任务书

专业: 班级:

学生:

设计时间:

指导教师: (签名)教研室主任: (签名)

设计题目:

设计任务及条件:

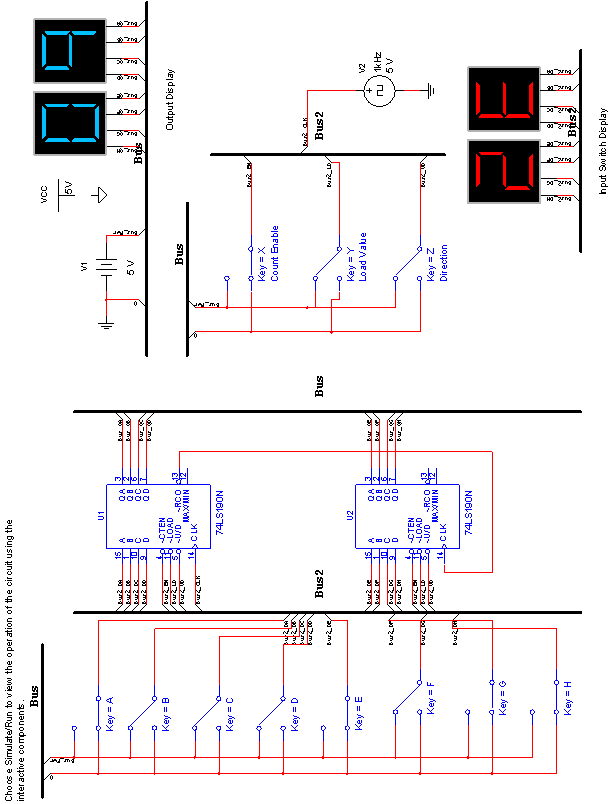

设计一可以预设计数数值的计数器,计数的范围为0~99。要求:1、用四个数码管完成显示,其中两个显示计数,另两个显示预置数;2、计数值可以加法计数,也可以减法计数;3、用两种方法设计。

要求:

使用两种设计方法设计,其中一种计数部分不能使用计数芯片(该方案不制版),使用D触发器进行设计;时钟部分采用555设计;显示采用7448驱动显示。另一种方案要求使用计数芯片(该方案不制版)。

设计内容:

1.编写两种方案硬件设计框图;

2.设计两种方案硬件电路图

3.硬件的制作和调试。

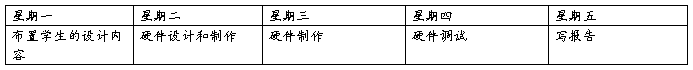

进度:

时间安排:

生物医学081、082

1、十七周六上午 布置设计内容 ,下午和周日查阅资料,进行设计(分组,3人一组)

2、十八周一上午 9:00由各班班长和学习委员到实验楼516领取器件发给每组同学(3人一组)并将分组名单交给该班指导老师。安排调试教室。

3、十八周一下午——周四上午,硬件制作

4、十八周四下午3:00实验楼420开始硬件调试+验收交作品

5、十八周五写报告

6、十九周一上午9:00交报告(每人一份)实验楼427

电科081、082

1、十七周六上午 布置设计内容 ,下午和周日查阅资料,进行设计(分组,3人一组)

2、十八周一上午 9:00由各班班长和学习委员到实验楼516领取器件发给每组同学(3人一组)并将分组名单交给该班指导老师。安排调试教室。

3、十八周一下午——周二上午3:00,硬件制作

4、十八周三下午3:00实验楼522开始硬件调试

5、十八周五上午9:00实验楼516硬件调试+验收交作品

6、十九周一上午9:00交报告(每人一份)实验楼427

指导教师:

医工081 王贤秋/张锋 医工082 冯雪/朱文渝

电科081 姜平/彭昭 电科082曾翔/师彦荣

设计成果:

1.设计说明书一份

2.硬件电路板

课程设计报告格式

? 封面

? 前言

? 目录

? 正文

设计任务与要求

第一章 使用D触发器进行设计

1.1方案设计

1.2电路设计

1.3总电路及工作原理

第二章 使用计数芯片进行设计

2.1方案设计

2.2电路设计

2.3总电路及工作原理

第三章 制作与调试

3.1电路板设计

3.2电路制作

3.3系统调试

第四章 总结

主要对自己做的设计做总结,少量讲心得体会。

? 参考文献

? 封底

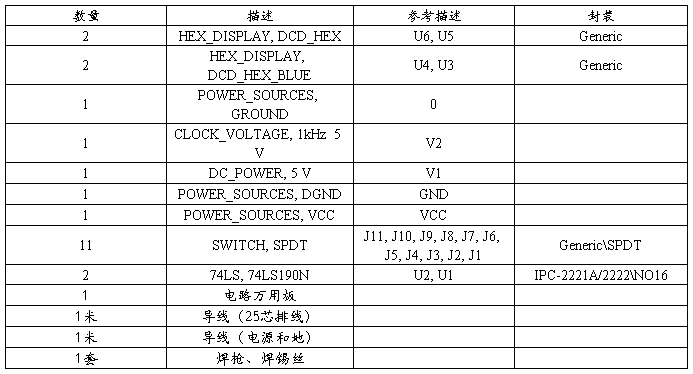

74LS190 中文资料

十进制同步加/减计数器54190/74190

190 为可预置的十进制同步加/ 减计数器, 共有54190/74190,54LS190/74LS190 两种线路结构形式。其主要电特性的典型值如下:

型号 fc PD

54190/74190 25MHz 325mW

54LS190/74LS190 25MHz 100mW

190 的预置是异步的。当置入控制端( LD )为低电平时,不管时钟CP 的状态如何,输出端(Q0~Q3)即可预置成与数据输入端(D0~D3)相一致的状态。

190 的计数是同步的,靠CP 加在4 个触发器上而实现。当计数控制端(CT )为低电平时,在CP 上升沿作用下Q0~Q3同时变化,从而消除了异步计数器中出现的计数尖峰。当计数方式控制(U /D)为低电平时进行加计数,当计数方式控制(U /D)为高电平时进行减计数。只有在CP 为高电平时CT 和U /D 才可以跳变

190 有超前进位功能。当计数溢出时,进位/错位输出端(CO/BO)输出一个低电平脉冲,其宽度为CP 脉冲周期的高电平脉冲;行波时钟输出端( RC )输出一个宽度等于CP 低电平部分的低电平脉冲。

利用 RC 端,可级联成N 位同步计数器。当采用并行CP控制时,则将RC 接到后一级CT ;当采用并行CT 控制时,则将RC 接到后一级CP。

引出端符号

CO/BO 进位输出/错位输出端

CP 时钟输入端(上升沿有效)

CT 计数控制端(低电平有效)

D0~D3 并行数据输入端

LD 异步并行置入控制端(低电平有效)

Q0~Q3 输出端

RC 行波时钟输出端(低电平有效)

U /D 加/减计数方式控制端

第二篇:数电课程设计

一、数字电子钟

1.设计目的

(1)培养数字电路的设计能力。

(2)掌握数字电子钟的设计、组装和调试方法。

2.设计内容及要求

(1)设计一个数字电子钟电路。要求:

①按24小时制直接显示“时”、“分”、“秒”。

②当电路发生走时误差时具有校时功能。

③具有整点报时功能,报时音响为4低1高,即在59分51秒、53秒、55秒、57秒输出500Hz信号,在59分59秒时输出1000 Hz信号,音响持续时间为1秒,最后一响结束时刻正好为整点。

(2)用中小规模集成电路组成电子钟,并在实验仪上进行组装、调试。

(3)画出各单元电路图、整机逻辑框图和逻辑电路图,写出设计、实验总结报告。

(4)选作部分:①闹钟系统。②日历系统。

3.数字电子钟基本原理及设计方法

数字电子钟的逻辑框图如图14-1-1所示。它由振荡器、分频器、计数器、译码器、显示器、校时电路和整点报时电路组成。振荡器产生的脉冲信号经过分频器作为秒脉冲,秒脉冲送入计数器计数,计数结果通过“时”、“分”、“秒”译码器显示时间。有的数字电子钟还加有定时响铃、日历显示等其它功能,需增加相应的辅助电路。

图14-1-1 数字电子钟的基本逻辑框图

(1)振荡分频电路

振荡器是数字电子钟内部用来产生时间标准“秒”信号的电路。构成振荡器的电路很多,图14-1-2(a)是RC环形多谐振荡器,其振荡周期T≈2.2RC。作为时钟,最主要的是走时准确,这就要求振荡器的频率稳定。要得到频率稳定的信号,需要采用石英晶体振荡器。石英晶体振荡器电路如图14-1-2(b)所示,这种电路的振荡频率只取决于石英晶体本身的固有频率。

图14-1-2 振荡器

(a)RC环形多谐振荡器 (b)石英晶体多谐振荡器

由于石英晶体振荡器产生的频率很高,要得到秒信号,需采用分频电路。例如,振荡器输出4 MHz信号,先经过4分频变成1 MHz,再经过6次10分频计数器,便可得到1Hz的方波信号作为秒脉冲。

(2)计数器

把秒脉冲信号送入秒计数器个位的CP输入端,经过6级计数器,分别得到“秒”个位、十位,“分”个位、十位,以及“时”个位、十位的计时。“秒”、“分”计数器为60进制,“时”计数器为24进制。

24进制计数器如图14-1-3所示。当“时”个位计数器输入端CP来到第10个触发脉冲时,该计数器归零,进位端QD5向“时”十位计数器输出进位信号。当第24个“时”脉冲(来自“分”计数器输出的进位信号)到来时,十位计数器的状态为0010,个位计数器的状态位0100,此时“时”十位计数器的QB6和“时”个位计数器的QC5输出为1。两者相与后送到两计数器的清零端R0A和R0B,通过74LS90内部的R0A和R0B与非后清零,完成24进制计数。同理可构成60进制计数器。

图14-1-3 24进制计数器

(3)译码显示电路

译码驱动器采用8421 BCD码七段译码驱动器74LS48,显示器采用共阴极数七段数码显示器,有关74LS48和七段显示器的使用方法前面已经作了介绍,这里不再赘述。

(4)校时电路

当数字电子钟出现走时误差时,需要对时间进行校准。实现校时电路的方法很多,如图14-1-4所示电路即可作为时计数器或分计数器的校时电路。

图14-1-4 校时电路

现设用该电路作为分计数器的校时电路,图中采用RS触发器作为无抖动开关。通过开关K的接入位置,可以选择是将“1 Hz信号”还是将“来自秒计数器的进位信号”送至分计数器的CP端。当开关K置于B端时,RS触发器的输出 、

、 ,“来自秒计数器的进位信号”被送至分计数器的CP端,分计数器正常工作;需要校正分计数器时,将开关K置于A端,这时RS触发器的输出

,“来自秒计数器的进位信号”被送至分计数器的CP端,分计数器正常工作;需要校正分计数器时,将开关K置于A端,这时RS触发器的输出 、

、 ,“1 Hz信号”被送至分计数器的CP端,分计数器在“1Hz信号”的作用下快速计数,直至正确的时间,再将开关K置于B端,达到了校准时间的目的。

,“1 Hz信号”被送至分计数器的CP端,分计数器在“1Hz信号”的作用下快速计数,直至正确的时间,再将开关K置于B端,达到了校准时间的目的。

(5)整点报时电路

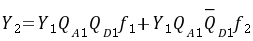

电路的设计要求在差10 s为整点时开始每隔1 s鸣叫一次,每次持续时间为1 s,共鸣叫5次,前4次为低音500 Hz,最后一次为高音1 kHz。因为分计数器和秒计数器从59分51秒计数到59分59秒的过程中,只有秒个位计数器计数,分十位、分个位、秒十位计数器的状态不变,分别为QD4QC4QB4QA4=0101,QD3QC3QB3QA3=1001,QD2QC2QB2QA2=0101,所以QC4=QA4=QD3=QA3=QC2=QA2=1不变。设Y1= QC4QA4QD3QA3QC2QA2,又因为在51、53、55、57秒时QA1=1,QD1=0,输出500Hz信号f2;59秒时QA1=1,QD1=1,输出1kHz信号f1,由此可写出整点报时电路的逻辑表达式为:

用与非门实现,则整点报时电路如图14-1-5所示。

用与非门实现,则整点报时电路如图14-1-5所示。

图中音响电路采用射极输出器,推动8Ω的喇叭。三极管基极串接1 kΩ限流电阻,是为了防止电流过大损坏喇叭,在集电极也串接51Ω限流电阻。三极管选用高频小功率管即可。

4.组装和调试要点

在实验箱上组装电子钟,组装时应严格按图连接引脚,注意走线整齐,布局合理,器件的悬空端、清0端、置1端要正确处理。调试步骤和方法如下:

(1)用数字频率计测量晶体振荡器输出频率,用示波器观察波形。晶体振荡器输出频率应为4 MHz,同时波形为矩形波。

(2)将频率为4 MHz的信号送入分频器各输入端,并用示波器检查各级分频器的输出频率是否符合设计要求。

(3)将1 s信号分别送入“时”、“分”、“秒”计数器,检查各级计数器的工作情况。若不正常,则可依次检查显示器、译码驱动器、计数器及计数器的反馈归零电路。

(4)观察校时电路的功能是否满足校时要求。

(5)将时间调整到59分50秒,观察报时电路能否准确报时。

(6)整机联调,使数字电子钟正常工作。

图14-1-5 整点报时电路

5.供参考选择的元器件

(1)集成电路:74LS90 12片,74LS48 6片,74LS00 6片,74LS20 2片。

(2)电阻:1 kΩ 3个,10 kΩ 4个,51 Ω 1个。

(3)电容:0.01μF 2个。

(4)三极管:3DG12 1个。

(5)其它:共阴极显示器 6个,4 MHz石英晶振 1片,8Ω扬声器 1个。

二、 交通信号灯

1.设计目的

(1)培养数字电路的设计能力。

(2)掌握交通信号灯控制电路的设计、组装和调试方法。

2.设计内容及要求

(1)设计一个交通信号灯控制电路。要求:

①主干道和支干道交替放行,主干道每次放行30 s,支干道每次放行20 s。

②每次绿灯变红灯时,黄灯先亮5 s钟,此时原红灯不变。

③用十进制数字显示放行及等待时间。

(2)用中、小规模集成电路组成交通信号灯电路,并在实验仪上进行组装、调试。

(3)画出各单元电路图、整机逻辑框图和逻辑电路图,写出设计、实验总结报告。

(4)选作部分:采用倒计时的方式显示放行及等待时间。

3.交通信号灯基本原理及设计方法

十字路口的红绿灯指挥着行人和各种车辆的安全通行。有一个主干道和一个支干道的十字路口如图14-2-1所示。每边都设置了红、绿、黄色信号灯。红灯亮表示禁止通行,绿灯亮表示可以通行,在绿灯变红灯时先要求黄灯亮几秒钟,以便让停车线以外的车辆停止运行。因为主干道上的车辆多,所以主干道放行的时间要长。

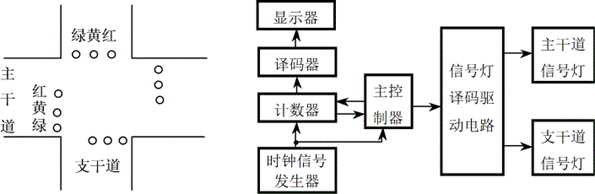

要实现上述交通信号灯的自动控制,则要求控制电路由时钟信号发生器、计数器、主控制器、信号灯译码驱动电路和数字显示译码驱动电路几部分组成,整机电路的原理框图如图14-2-2所示。

图14-2-1 十字路口图 图14-2-2 交通信号灯控制电路框图

(1)主控制器

十字路口车辆运行情况只有4种可能:①设开始时主干道通行,支干道不通行,这种情况下主绿灯和支红灯亮,持续时间为30 s。②30 s后,主干道停车,支干道仍不通行,这种情况下主黄灯和支红灯亮,持续时间为5 s。③5 s后,主干道不通行,支干道通行,这种情况下主红灯和支绿灯亮,持续时间为20 s。④20 s后,主干道仍不通行,支干道停车,这种情况下主红灯和支黄灯亮,持续时间为5 s。5 s后又回到第一种情况,如此循环反复。因此,要求主控制器电路也有4种状态,设这4种状态依次为:S0、S1、S2、S3。状态转换图如图14-2-3所示。

图14-2-3 主控制器的状态图 图14-2-4 主控制器的逻辑图

设S0=00,S1=01,S2=10,S3=11。实现这4个状态的电路,可用两个触发器构成,也可用一个二-十进制计数器或二进制计数器构成。如用二-十进制计数器74LS90实现,采用反馈归零法构成4进制计数器,即可从输出端QBQA得到所要求的4个状态。逻辑图如图14-2-4所示。为以后叙述方便,设X1=QB,X0=QA。

(2)计数器

计数器的作用有二:一是根据主干道和支干道车辆运行时间以及黄灯切换时间的要求,进行30 s、20 s、5 s3种方式的计数;二是向主控制器发出状态转换信号,主控制器根据状态转换信号进行状态转换。计数器除需要秒脉冲作时钟信号外,还应受主控制器的状态控制。计数器的工作情况为:计数器在主控制器进入状态S0时开始30 s计数;30 s后产生归零脉冲,并向主控制器发出状态转换信号,使计数器归零,主控制器进入状态S1,计数器开始5 s计数;5 s后又产生归零脉冲,并向主控制器发出状态转换信号,使计数器归零,主控制器进入状态S2,计数器开始20 s计数;20 s后也产生归零脉冲,并向主控制器发出状态转换信号,使计数器归零,主控制器进入状态S3,计数器又开始5 s计数;5 s后同样产生归零脉冲,并向主控制器发出状态转换信号,使计数器归零,主控制器回到状态S0,开始新一轮循环。

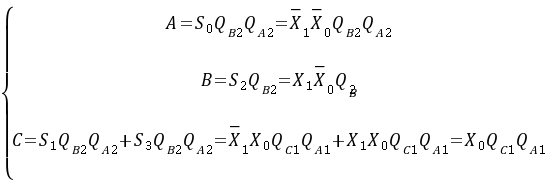

根据以上分析,设30 s、20 s、5 s计数的归零信号分别为A、B、C,则计数器的归零信号L为:

其中:

其中:

考虑到主控制器的状态转换为下降沿触发,将L取反后送到主控制器的CP端作为主控制器的状态转换信号。计数器的逻辑图如图14-2-5所示。

图14-2-5 计数器

(3)控制信号灯的译码电路

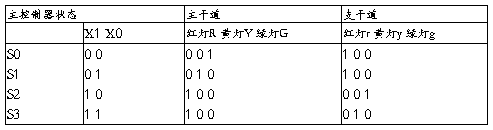

主控制器的4种状态分别要控制主、支干道红、黄、绿灯的亮与灭。设灯亮为1,灯灭为0,则控制信号灯的译码电路的真值表如表14-2-1所示。

表14-2-1 控制信号灯的译码电路的真值表

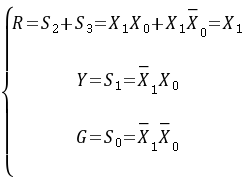

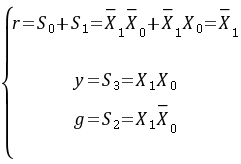

由真值表可分别写出各个灯的逻辑表达式:

译码电路的逻辑图如图14-2-6所示。

图14-2-6 控制信号灯的译码电路

4.组装和调试要点

在实验箱上按各单元电路分别搭接主控制器、计数器、信号灯译码器、数字显示译码器和秒脉冲信号发生器。然后按照以下步骤进行调试:

(1)秒脉冲信号发生器的调试,可按照数字电子钟的方法逐级调试振荡电路和分频电路,使输出频率符合设计要求。

(2)将秒脉冲信号送入主控制器的CP端,观察主控制器的状态是否按照00→01→10→11→00→…的规律变化。

(3)将秒脉冲信号送入计数器的CP端,接入主控制器的状态信号X1、X0,并把主控制器的状态转换信号送入主控制器的CP端,观察计数器是否按30 s、5 s、20 s、5 s、 30 s……循环计数。

(4)把主控制器的状态转换信号X1、X0接至信号灯译码电路,观察6个发光二极管是否按设计要求发光。

(5)整机联调,使交通信号灯控制电路正常工作。

5.供参考选择的元器件

(1)集成电路:74LS90 9片,74LS48 2片,74LS00 6片,74LS20 2片。

(2)电阻:1 kΩ 2个。

(3)电容:0.01 μF 2个。

(4)其它:发光二极管6个(红、黄、绿各2个),共阴极显示器2片,4 MHz石英晶振1片。