武汉纺织大学

数字逻辑 实验报告

数计 系 计算机 专业 102 班 1004681083

姓名 鲍旭良 指导老师 曾西洋 实验日期 2012年6月

实验名称 三人表决器

…… …… 余下全文

[技能实训]三人表决器的逻辑电路设计与制作

姓名: 班级: 日期: 课时: 成绩:

一、实训目标

1、增强专业意识,培养良好的职业道德和职业习惯;

2、能借助资料读懂集成电路的型号,明确引脚与引脚功能;

3、了解数字集成电路的检测。

二、实训设备

1、数字实验箱;

2、万用表(MF47型 1块);

3、通用面包板1块;

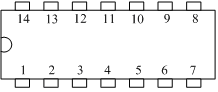

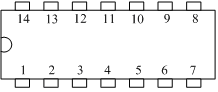

4、集成电路74LS00 2个。

三、实训内容与步骤

1、三人表决器的逻辑电路的设计。

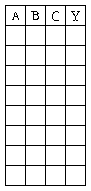

(1)完成真值表6-2-8。

表6-2-8真值表

(2)由真值表写出表达式并化简。

Y=

(3)由表达式作出电路图。

(4)根据三人表决器的逻辑电路图画出安装图。

Y

Y

A B C

(5)根据安装图完成电路的安装。

(6)验证表决器的逻辑功能(与表6-2-8比较)。

2、若手头只有74LS00集成电路,试用该芯片完成三人表决器功能。

(1)将表达式转换成与非式。

Y=

(2)由表达式作出电路图。

(3)根据三人表决器的逻辑电路图画出安装图。

Y

Y

…… …… 余下全文

电子技术与仿真

项目报告

项目名称: 三人表决器的制作

专业班级: 电气1 2 1

姓 名: 刘斌

学 号: 2 4

指导教师: 张琴

江西工业工程职业技术学院电工电子实训中心

一、项目目的

正确理解数字电路的要求,能知道与门、或门、非门的含义;做到了解要用到的每个芯片的引脚是什么门电路,可以去图书馆查阅书籍也可上网去阅读相关的网页资料。做到能真正了解电路的构造原理,这样才可以更好学好这门电路的元器件的应用。

二、项目要求

1) 判断正确的引脚位置;

2) 理解数字电路的原理,掌握操作步骤,能正确安装所选定的电路;

3) 掌握测试仪表仪器检测原件的使用及调整;

4) 会根据测试结果分析故障产生的原因;

5) 会利用原理图纸,判断具体故障的原因;

6) 必须得出实验的仿真结果;

7) 根据自己所仿真的电路原理图画出实物装配图。

…… …… 余下全文

项目一:三人表决器的设计与装配

实 验 报 告

电子信息工程系

20##-2012学年第一学期

设计题目]

项目一:三人表决权器的设计与装配

一、[设计要求]

1.对电路图的原理进行分析,并对原理图进行改良。用Mutisim软件中进行仿真调试,弄清楚电路的工作原理。

2.熟悉各元件的性能和设置元件的参数。

3. 对元件的性能进行评估和替换、用性能和使用范围更好,更常用的元件进行替换,使自己实际的元件更接近实际使用。

4. 元件安装符合工艺要求,既考虑其性能又应美观整齐。焊接元件要注意焊点的圆润。

5.学习数字逻辑电路的设计方法。

6.培养自己的分析故障和解决问题的能力。

二、元件清单:

2、元件的检测

Ø 电阻的检测:先用色环法对电阻进行读数,然后再用万用表打到相应的电阻档对电阻进行进一步的检测。

Ø 发光二极管的检测:将万用表打至欧姆档×10K,万用表的表笔对发光二极管进行反接,如果发光二极管会发光,那么说明该发光二极管是好的。

Ø 按钮的检测:将万用表打至欧姆档×1K,用万用表的表笔接在按钮的两端,如果万用表打到无穷大,按下按钮万用表的指针达到零,那么说明该按钮接通了,也是好的;反之是坏的。

…… …… 余下全文

学生实验报告

实验课名称:VHDL硬件描述语言 实验项目名称:五人表决器 专业名称:电子科学与技术 班

学级:32050801 号:05 学生姓名:孙小喃 教师姓名:程鸿亮

20xx年11月06日

组别 第二组 同组同学 钞田田

实验日期20xx年11月06日 实验室名称______________成绩_____

一. 实验名称

五人表决器

二. 实验目的与要求

目的:

设计一个五人表决器,掌握异步清零以及锁存器的工作机制,掌握QuartusII软件的使用方法以及GW48型SOPC开发平台中的输入输出模式配置方法。

要求:

通过VHDL编程,实现一个五人表决器,要求有5个表决输入端、1个清零端、1个锁存端、表决结果显示端。首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。

三. 实验内容

1、打开QuartusII软件,建立一个新的工程:

1)单击菜单File\New Project Wizard?

2)输入工程的路径、工程名以及顶层实体名。

3)单击Next>按钮,进入下一个界面。由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。

4) 设置我们的器件信息:设置为cyclone∏,选择FBGA,484,8,在available devices中选择EP2C35F484C8 33216 483840 70 4, 然后单击Next>,指定第三方工具。这里我们不指定第三方EDA工具,单击Next>后结束工程建立。

2、建立VHDL文件:

1) 单击File\New菜单项,选择弹出窗口中的VHDL File项,单击OK按钮以建立打开空的VHDL文件,注意此文件并没有在硬盘中保存。

2) 在编辑窗口中输入VHDL源文件并保存,注意实体名、文件名必须和建立工程时所设定的顶层实体名相同。

…… …… 余下全文

实验报告

一. 实验名称

三人投票表决器的实现

二. 实验目的

1) 熟练掌握QUARTUSII的操作方法

2) 了解VHDL程序书写基本语法规则

3) 熟悉原理图绘制的方法

4) 学会波形仿真验证结果

三. 实验原理

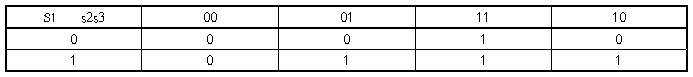

设开关状态0,1代表三人投票情况s1,s2,s3,二极管的亮灭代表投票结果win,lose。画卡诺图(表1):

表格 1

化简卡诺图得:win=s1s2+s2s3+s1s3

则:lose=~win

四. 实验过程

1) 创建工程

2) 新建VHDL文件,输入程序,结果见图表1:

图表 1

3) 编译工程,查看RTL,见图表2

图表 2

4) 创建波形仿真文件,设置s1,s2,s3的波形,进行仿真,查看结果见图表3:

图表 3

5)投票表决器除了可以用VHDL语言实现外还可以用原理图进行实现,见图表4:

图表 4

5) 用原理图法的实现接下来步骤同3)、4)

…… …… 余下全文

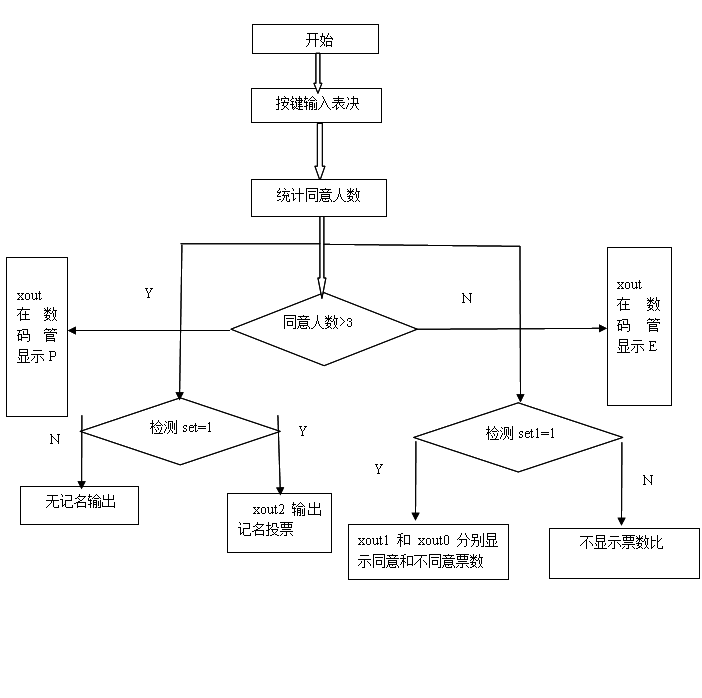

七人表决器设计

1. 能够完成七人表决的功能,并且直观的显示结果:决议通过显示字母P,否则显示 字母E;

2.能够选择显示表决双方的人数,有控制开关与显示指示灯,并且能够实时的显示反对与赞成的人数;

3.能够选择是否记名,并有指示灯显示。当选择记名时,与表决参与者相对应的指示灯亮起;

4.不设置弃权的状况,超过三人同意则表示决议通过。

1.使用Altera的Cyclone II器件,FPGA型号为EP2C35F672C6N;开发平台为Quartus II 8.0

2.使用6个拨动开关用以进行表决,开关闭合时表示同意,断开时表示不同意;

3.使用6个LED用以显示表决的个人结果,用以显示记名时的情况。LED亮起表示表决人同意,否则表示不同意;

4.使用一个七段数码管用以显示表决结果,通过显示P,否则显示E;另外使用两个数码管用以分别显示同意与不同意的人数;

5.使用两个拨动开关控制是否记名,是否显示表决的人数结果;

6.其他电路按需要搭建。

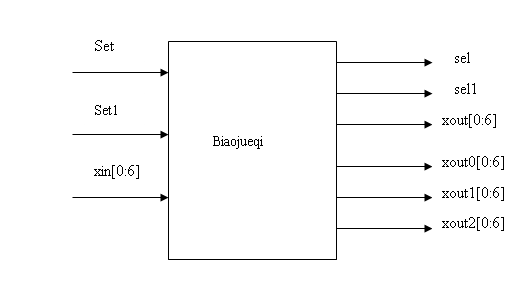

注释:set:选择是否记名

set1:选择是否显示投票人数及比例

xin[0:6]:表决输入,分别是七个拨动开关

sel:输出指示是否记名投票

sel1:输出指示是否显示投票人数及比例

xout[0:6]:译码用数码管输出表决是否通过

…… …… 余下全文

河 北 科 技 大 学

实 验 报 告

20##级 电信专业 122 班 学号38 15年5月20日

姓名 郑振兴 同组人 指导教师 于国庆

实验名称 实验一 七人表决器 成绩

实验类型 设计型 批阅教师

一、实验目的

(1)掌握MUXPLUS II语言输入的设计过程。

(2)初步了解VHDL语言。

(3)熟悉FPGA项目设计的基本流程。

二、实验原理:

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”; 输入变量为逻辑“0”时表示表决者“不赞同”;输出逻辑“1”时,表示表决“通过”; 输出逻辑“0”时,表示表决“不通过”;当表决器的七个输入变量中有4个及以上为“1”时,则表决器输出为“1”,否则为“0”。

…… …… 余下全文