《数字逻辑电路设计》课程设计

总 结 报 告

题目: 汽车尾灯控制器设计

指导教师: 莫琳

设计人员(学号): 李海沧 1107200125

班级: 电信111

日期:20##年5月

一、设计任务书

一、题目 汽车尾灯控制器设计

要求在实验箱上独立做出具体电路

二、设计要求

1. 设计系统应具有以下功能

汽车尾灯两侧各有3个指示灯汽车运行时具有如下模式:

1)汽车正向行使时,左右两侧的指示灯全部处于熄灭状态。

2)汽车右转弯行驶时,右侧的3个指示灯按右循环顺序点亮,

3)汽车左转弯行驶时,左侧的3个指示灯按左循环顺序点亮

4)汽车临时刹车时,左右两侧的指示灯同时处于闪烁状态。

三、给定条件

1.只能采用实验室提供的中小规模电路进行设计;

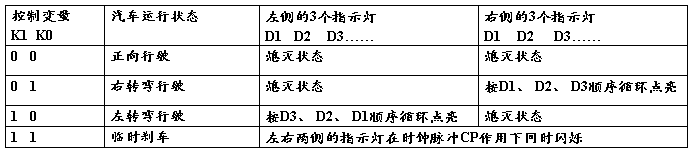

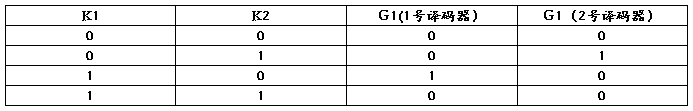

为了区分4种不同的显示模式,设置2个状态控制变量,K1、K0。

汽车尾灯显示状态与汽车运行状态的关系

K1

K1

K0

K0

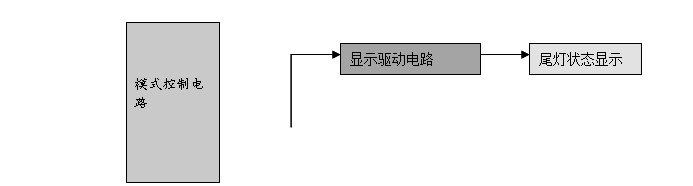

汽车尾灯控制器的结构框图

三、给定条件

1.只能采用实验室提供的中小规模电路进行设计;

二、设计框图及整机概述

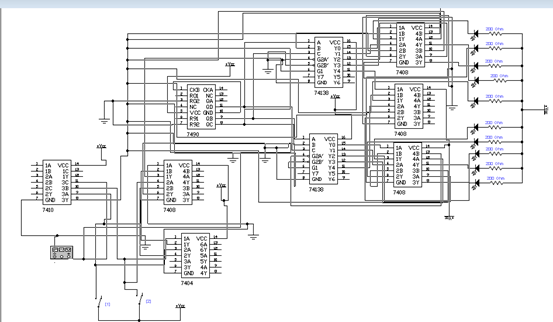

1.本设计电路为左右各5个灯的汽车尾灯设计电路,共由6大部分组成。

(1)K1,K2开关(2)控制电路(3)五进制计数器(4)3-8线译码器(5)驱动电路

(6)尾灯状态显示

2.整机概述

本电路旨在模拟汽车尾灯工作状态。当不做操作时,10个尾灯均处于熄灭状态;当只闭合K1开关时,左侧5个尾灯按从右到左顺序循环点亮;当只闭合K2开关时,右侧5个尾灯按从左到右顺序循环点亮;当同时闭合K1,K2两个开关时,10个尾灯同时处于闪烁状态。

3.设计框图如下图所示

三、各单元电路的设计方案及原理说明

1.计数器电路

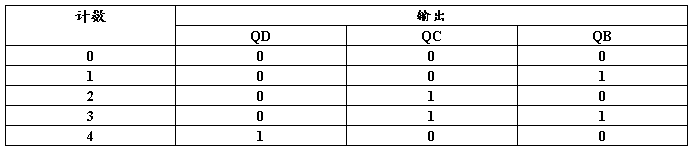

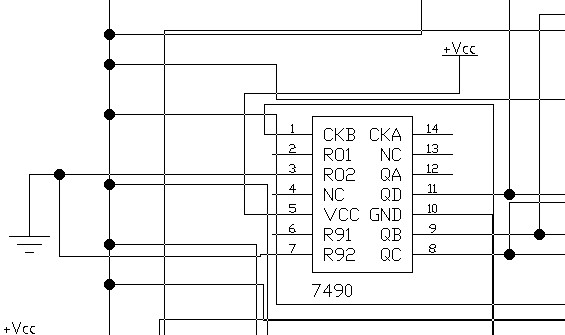

五进制计数器由异步计数器74LS90实现,当R0,R9输入端都为低电平时,时钟脉冲从B端输入,从QD,QC,QB端输出,形成异步五进制加法计数器。计数状态表及计数器电路图如下图所示:

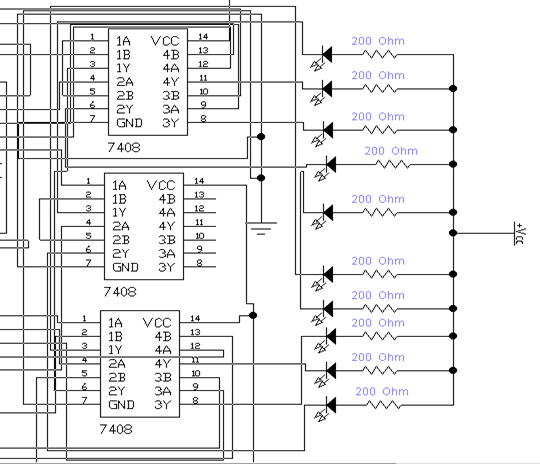

2.尾灯状态显示

由于使用发光二极管做尾灯,所以正向方向接Vcc(1),反向方向接由74LS138译码器及74LS08与门接出的逻辑0,再加入保护电阻,则发光二极管可正常工作,电路如下图所示:

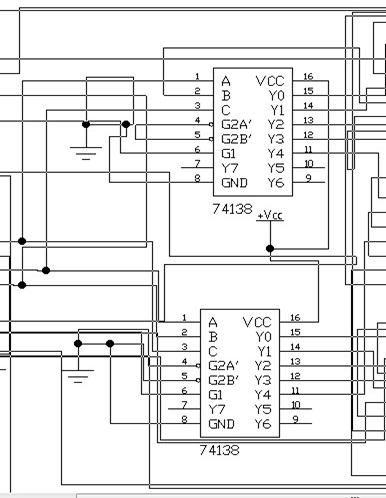

3.3-8译码器电路

由于共由10个汽车尾灯,所以需要两片74LS138译码器,本设计电路中左侧5个尾灯使用1号译码器,右侧5个尾灯使用2号译码器,电路图如图所示:

4.控制电路

(1)汽车正向行驶时,K1,K2均等于0,74LS138译码器G1端输入低电平,译码器不工作;

(2)汽车刹车时,K1,K2均等于1,74LS138译码器G1端输入低电平,译码器不工作,左右两侧汽车尾灯均处于闪烁状态;

(3)汽车左转弯时,K1=1,K2=0,1号74LS138译码器G1端输入高电平,工作。2号74LS138译码器G1端输入低电平,不工作。左侧5个尾灯按从右到左顺序循环点亮;

(4)汽车右转弯时,K1=0,K2=1,2号74LS138译码器G1端输入高电平,工作。1号74LS138译码器G1端输入低电平,不工作。右侧5个尾灯按从左到右顺序循环点亮。

根据上述描述可绘制出控制电路状态表:

控制电路电路图如下图所示:

四、调试过程及结果分析

本设计电路通过EWB仿真软件进行仿真

根据设计思路摆放各部分元器件和整体布线

仿真结果:当不做操作时,10个尾灯均处于熄灭状态;

当只闭合K1开关时,左侧5个尾灯按从右到左顺序循环点亮;

当只闭合K2开关时,右侧5个尾灯按从左到右顺序循环点亮;

当同时闭合K1,K2两个开关时,10个尾灯同时处于闪烁状态。

五、设计、安装及调试中的体会

1.设计电路应分部完成,在对整体电路有一定了解的情况下,把庞大的电路分解成若干部分,分别设计出每一小部分的电路再组合连接。

2.仿真电路时应注意各个元器件摆放的地方,要方便布线,尽量减少不必要的元器件及导线,否则电路图整体看起来会很杂乱,不便于对照电路图进行焊板及调试。

3.刚刚连接完电路但仿真失败时一定不要惊慌失措,找到问题所在,顺着电路图一点一点寻找可能出错的原因。

4.要特别注意细节问题,比如芯片的Vcc和地线,尾灯的连接顺序等等。

5.焊接技术非常重要,又是一个点的虚焊可能会导致整个电路的测试失败。

6.整个设计、安装及调试过程需要极大的耐心,不要畏惧一次两次的失败,静下心来坚持住就离会成功越来越近。

六、对本次课程设计的意见及建议

1.对于芯片及各种元器件应该找专人管理和记录,否则出现的乱拿乱放现象会导致其他同学找不到所需元器件等。

2.提醒大家爱护实验室器材,节约实验原件及消耗品。

七、附录

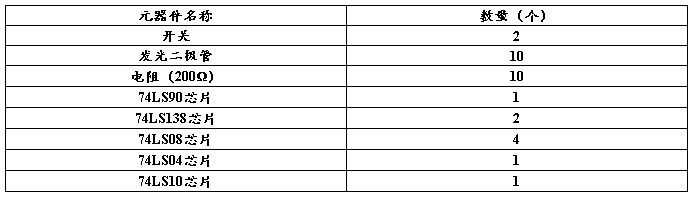

1.整机电路图

2.元器件清单

第二篇:电子数字时钟课程设计报告(数电)

数字电子钟的设计

1. 设计目的

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,我们此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。且由于数字钟包括组合逻辑电路和时叙电路。通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

1.1设计指标

1. 时间以12小时为一个周期;

2. 显示时、分、秒;

3. 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;

1.2 设计要求

1、电路设计原理说明

2、硬件电路设计(要求画出电路原理图及说明)

3、实物制作:完成的系统能达到题目的要求。

4、完成3000字的课程设计报告

2. 功能原理

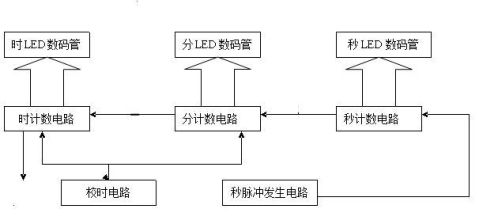

2.1 数字钟的基本原理

数字电子钟由信号发生器、“时、分、秒”计数器、LED数码管、校时电路、整点报时电路等组成。工作原理为时钟源用以产生稳定的脉冲信号,作为数字种的时间基准,要求震荡频率为1HZ,为标准秒脉冲。将标准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每

累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计数器,可以实现24小时的累计。LED数码管将“时、分、秒”计数器的输出状态显示。校时电路是来对“时、分、秒”显示数字进行校对调整。

2.2 原理框图

3. 功能模块

3.1 振荡电路

多谐振荡器也称无稳态触发器,它没有稳定状态,同时无需外加触发脉冲,就能输出一定频率的矩形波形(自激振荡)。用555实现多谐振荡,需要R1,R2和电容,并接+5V的直流电源。

振荡周期:T=0.69(R1+2R2)C

其中当R1=5K,R2=4.7K,C=100uF时,T=0.9936s

2

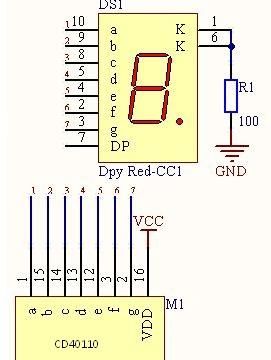

3.2 CD40110工作原理

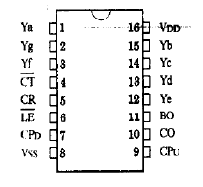

CD40110为十进制可逆计数器/锁存器/驱动器,具有加减计数,计数器状态锁存,七段译码输出等共能。这次设计用到CD40110的加计数、七段译码输出功能。

CD40110有2个计数时钟输入端CPu和CPd分别用作加计数时钟输入和减计数时钟输入。由于电力内部有一个时钟信号预处理逻辑,以此当一个时钟输入端计数工作是,另一个时钟输入端可以是任意状态,所以我们采用CPu接脉冲信号,CPd悬空。

CD40110的进位输出CO和借位输出BO一般为高电平,当计数器从9~0时,BO输出脉冲,当计数器从0~9时,CO输出脉冲,以此利用CO端可以实现大于10进制的计数功能。

BO 进位输出端

CO 借位输出端

CPd 减计数器时钟输入端

CPu 加计数器时钟输入端

CR 清除端

/CT 计数允许端

/LE 锁存器预置端

VDD 正电源

VSS 地

Ya~Yg 锁存译码输出端 封装图

功能表

3

3.2 秒计数电路

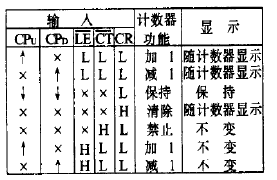

秒的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。当计数到59时清零并重新开始计数。秒的个位部分的设计:利用十进制计数器CD40110设计10进制计数器显示秒的个位 。个位计数器由0增加到9时产生进位,连在十位部计数器脉冲输入端CP,从而实现10进制计数和进位功能。利用74LS161和74LS11设计6进制计数器显示秒的十位 ,当十位计数器由0增加到5时利用74LS11与门产生一个高电平接到个位、十位的CD40110的清零端,同时产生一个脉冲给分的个位。

60进制--秒计数电路

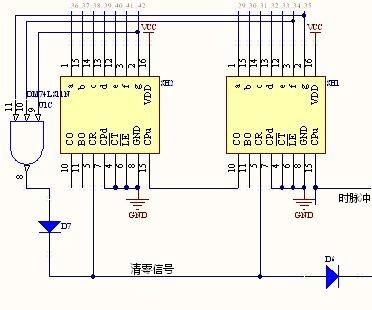

3.3 分计数电路

分的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。当计数到59时清零并重新开始计数。秒的个位部分的设计:来自秒计数电路的进位脉冲使分的个位加1,利用十进制计数器CD40110设计10进制计数器显示秒的个位 。个位计数器由0增加到9时产生进位,连在十位部计数器脉冲输入端CP,从而实现10进制计数和进位功能。利用74LS161和74LS11设计6进制计数器显示秒的十位 ,当十位计数器由0增加到5时利用74LS11与门产生一个高电平接到个位、十位的CD40110的清零端,同时产生一个脉冲给时的个位。

4

60进制--分计数电路

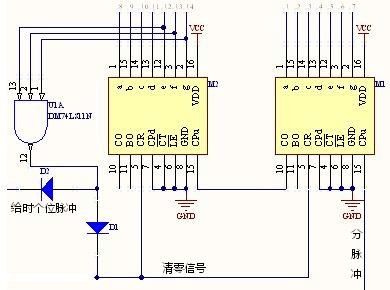

3.4 时计数电路

来自分计数电路的进位脉冲使时的个位加,个位计数器由0增加到9是产生进位,连在十位计数器脉冲输入端CP,当十位计到2且个位计到3是经过74LS11与门产生一个清零信号,将所有CD40110清零。

24进制--时计数电路

3.5 显示电路

由CD40110产生十进制数字,再由数码管显示出来。这里的LED数码管是采用共阴的方法连接的。

5

3.6 校时电路

数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计 数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。这里利用轻触开关来实现校时功能,轻触开关的一端接高电平,另一端接时或分的个位CD40110的CP,当按下轻触开关时,时或分的个位就会加1,这样就能实现校时功能。

4. 系统电路总图

将设计的各个单元电路进行级联,得到数字电子钟系统电路原理图见附录1。

5. 实物图(见附录2)

6.经验体会

通过这次对数字电子钟的设计作,让我了解了电路设计的基本步骤,也让我了解了关于数字钟的原理与设计理念,要设计一个电路先进行软件模拟仿真再进行实际的电路制作。但是最后的成品却不一定与仿真时完全一样,因为,再实际接线中有着各种各样的条件制约着。而且,在仿真中无法成功的电路接法,在实际中因为芯片本身的特性而能够成功。所以,在设计时应考虑两者的差异,从中找出最适合的设计方法。通过这次学习,让我对各种电路都有了大概的了解,所以说,坐而言不如立而行,对于这些电路还是应该自己动手实际操作才会有深刻理解。

6

7

8