南华大学

船山学院

实验报告

( 20## ~2010 学年度 第二学期 )

姓名 学号 200994401

一、实验目的:

熟悉MAX+plus 10.2的VHDL文本设计流程全过程

二、实验原理图:

三、实验代码:

(1)LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f : STD_LOGIC;

BEGIN

u1 : h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e);

u2 : h_adder PORT MAP(a=>e, b=>cin, co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);

END ARCHITECTURE fd1;

(2)LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ;

BEGIN

abc <= a & b ;

PROCESS(abc)

BEGIN

CASE abc IS

WHEN "00" => so<='0'; co<='0' ;

WHEN "01" => so<='1'; co<='0' ;

WHEN "10" => so<='1'; co<='0' ;

WHEN "11" => so<='0'; co<='1' ;

WHEN OTHERS => NULL ;

END CASE;

END PROCESS;

END ARCHITECTURE fh1 ;

(3)LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one ;

四、实验结果:

五、实验心得:

一位全加器设计可以由两个半加器组合而成,那么八位全加器的VHDL设计应该也可以由八个一位全加器来完成,效果应该和原理图输入一样呢?

第二篇:EDA 1位全加器

课程名称: EDA技术与FPGA应用设计

实验项目: 1位全加器

20##年 6 月 22 日

一、实验目的

① 熟悉ispDesignEXPERT System、Quartus II原理图设计流程的全过程。

② 学习简单组合电路的设计方法、输入步骤。

③ 学习层次化设计步骤。

④ 学习EDA设计的仿真和硬件测试方法。

二、实验原理

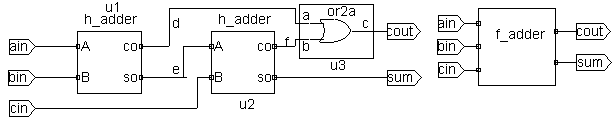

1位全加器可以由2个半加器及1个或门连接而成,因此首先完成如图的半加器设计。

使用原理图输入的方法先进行底层半加器设计,在建立上层全加器设计文件,调用半加器和或门符号,连线完成原理设计。

半加器原理图

全加器原理图

三、主要仪器设备

Isp Design EXPERT软件,FPGA配置存储芯片,硬件电路板。

四、 实验步骤

(1)启动Isp Design EXPERT软件,并创立半加器设计项目和选择器件ispLSI 1016E。

(2)添加原理图输入源文件

(3)根据上图添加半加器中的元件符号和输入输出符号,然后连线,画好半加器。

(4)将图形中半加器的添加输入输出端口并锁定引脚。

(5)画出半加器的仿真波形。

(6)删掉半加器的输入输出端口链接和引脚,将半加器变成模块的形式并保存。

(7)再把半加器当作元件,按照原理图链接。

(8)根据图形标记输入输出和锁定引脚

(9)保存所完成的全加器图

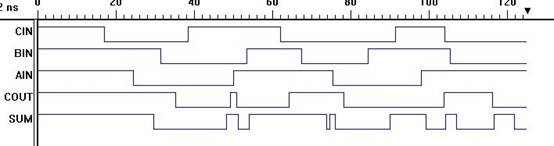

(10)建立波形仿真源文件,分别进行功能和时序仿真

(11)接好编程电缆,选择Scan Board命令。完成一个包含菊花链中所有器件的基本结构文件。

(12)添加JEDEC文件和器件编程。

(13)根据锁定的引脚观察实验板上相应的LED灯的变化。

五、实验结果及分析

设计校验过程:

功能仿真:在设计输入阶段,进行逻辑功能验证,称为功能仿真或前仿真。

时序仿真:在选择了具体器件并完成布局布线方案后进行的时序仿真称为后仿真或延时仿真。由于不同器件的内部延时不一样,不同的布局、布线方案也给延迟造成了很大的影响,因此在设计处理以后,分析时序关系,估计设计的性能以及检查和消除竞争冒险等是必要的。

全加器真值表

半加器电路图

全加器电路图

全加器功能仿真图:

全加器时序仿真图:

根据真值表实验板验证结果正确。由波形图观察得证正确,时序仿真有一定的延时。

六、实验心得

这个实验是我第一次接触isp Design EXPERT System这个软件。开始时按照步骤一步一步做,但因为对该软件不熟悉,所以做得比较慢。此次实验加深了对这个软件的功能的认识与操作流程的熟悉程度,以及设计一位全加器的基本思想与设计方案。