EDA 技术基础实验报告

实验项目名称: 用原理图输入法设计4位加法器

学院专业 : 信息学院电子专业

姓名 :

学号 :

实验日期: 20 实验成绩:

实验评定标准:

一、 实验目的

熟悉利用Quartus Ⅱ的原理图输入方法设计简单组合电路,掌握层次化设计的方法。并通过一个4位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二、 实验器材

电脑一台

Quartus Ⅱ软件

三、 实验内容与步骤

1. 在Quartus Ⅱ软件中建立工程,画图生成一个半加器的.bdf文件。

2. 将此半加器文件设置成可调用的元件,使之成为一个元件符号存盘。

3. 设计全加器顶层文件,以.bdf存盘。

4. 将设计项目(.bdf文件)设置成工程和时序仿真。

5. 截图保存波形文件图,及仿真结果。

6. 将全加器原理图文件设置成符号元件,以供4位加法器的更高层设计。

7. 按实验要求画出4位加法器原理图,建立其波形并仿真,截下仿真结果图。

四、 实验电路图(程序)

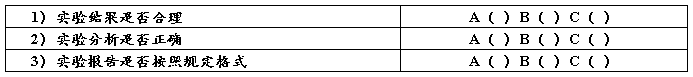

1. 半加器电路原理图如下:

半加器h_adder.bdf电路原理图(1)

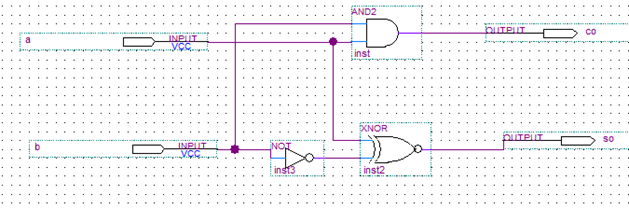

2. 全加器电路原理图如下:

全加器f_adder.bdf电路原理图(2)

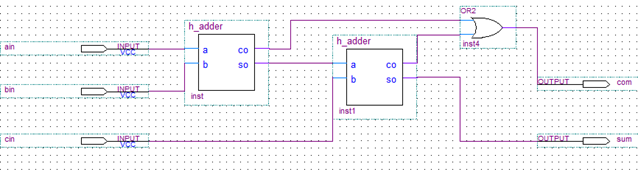

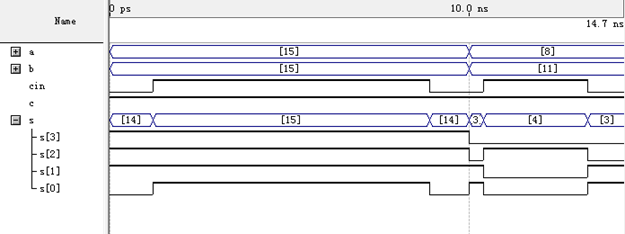

3. 4位加法器four_adder.bdf电路原理图如下:

4位加法器four_adder.bdf电路原理图(3)

五、实验仿真结果及分析

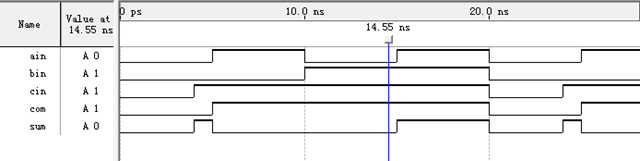

1. 全加器的仿真波形图如下:

全加器波形仿真图(3)

分析:

ain, bin, cin三段为输入,sum为和,com为进位,满足相关的逻辑表达式

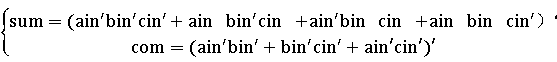

2. 4位全加器仿真波形图如下:

分析:

4位a[3..0]输入与4位b[3..0]输入以及来自cin输入的数码相加得到4位输出s[3..0]和进位输出c,由图可见满足加法原理。

第二篇:数电实验报告1.2-一位减法器、一位加法器

<熟悉QuartusII和Verilog HDL数字逻辑电路设计基础环境>实验报告

学生姓名: 李旭 文超周

班级学号: 11自动化 1138033 1138019

指导老师: 潘秀琴

<实验报告内容>

一、实验名称: 学习QurtusII基本功能和使用方法,完成一位减法器、一位加法器的原理图输入和文本输入、编译校验及功能仿真。

二、实验学时:4学时

三、实验目的:熟悉Quartus II基本功能和使用方法,掌握原理图输入、文本输入的步骤。

四、实验内容:完成一位加法器、一位减法器的设计输入并进行仿真输出。

五、实验原理:数字逻辑电路中各种门电路的功能和使用方法

六、实验步骤:

1. 了解quartusII的基本功能使用;

2.设计输入:首先设计出逻辑电路,然后将所设计的数字逻辑电路以某种方式输入到计算机中,QuartusII有原理图输入和文本(代码)输入两种输入模式。

3.设计编译校验:编译连接好的输入图形。

七、实验结果:

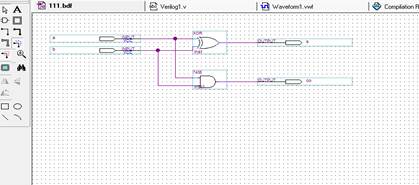

1.加法器:A.半加器

原理图:

文本:

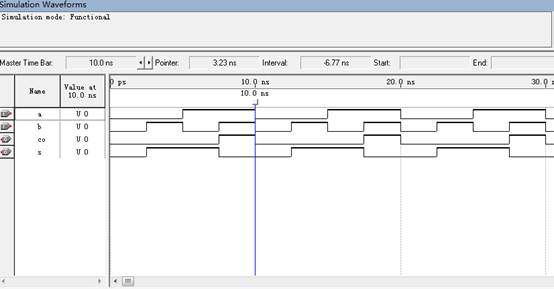

波形图:

B.一位全加器

全加器:

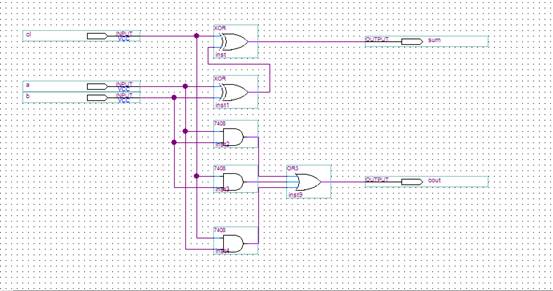

原理图:

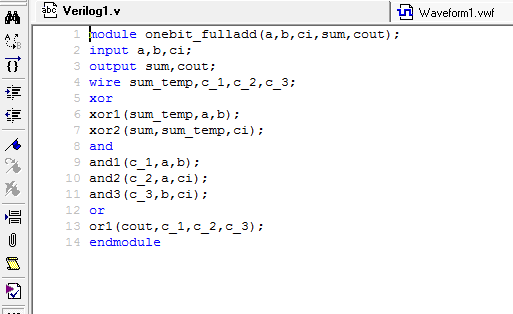

文本输入:

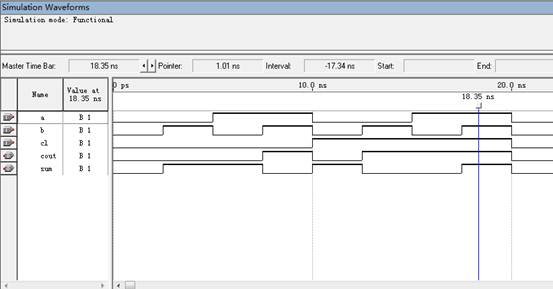

波形图:

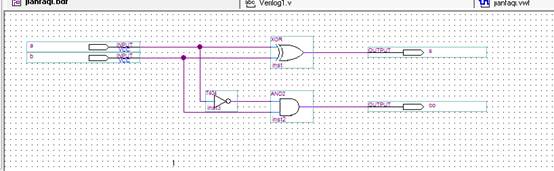

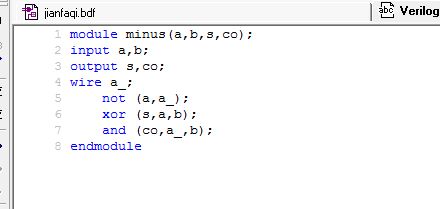

2.减法器:

原理图:

文本输入:

波形图:

八、心得体会:这是使用这个软件的第二次实验对于软件的使用已经比较熟练能够很快连接好电路进行试验

九、附录:<程序代码>

1.加法器:

A.半加器

module adder(a,b,s,co);

input a,b;

output s,co;

and X1(a,b);

xor Y1(a,b);

endmodule

B.一位全加器

module onebit_fulladd(a,b,ci,sum,cout);

input a,b,ci;

output sum,cout;

wire sum_temp,c_1,c_2,c_3;

xor

xor1(sum_temp,a,b);

xor2(sum,sum_temp,ci);

and

and1(c_1,a,b);

and2(c_2,a,ci);

and3(c_3,b,ci);

or

or1(cout,c_1,c_2,c_3);

endmodule

2.减法器

module minus(a,b,s,co);

input a,b;

output s,co;

wire a_;

not (a,a_);

xor (s,a,b);

and (co,a_,b);

endmodule