CPLD/FPGA设计实验报告

实验一 半加器

一、 创建工程

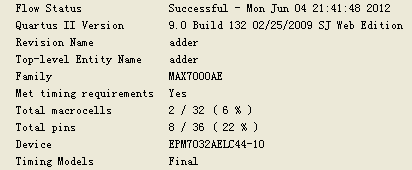

工程名称:adder 顶层实体文件名:adder

器件: EP1C12Q240C8 (要求:Cyclone系列任意器件)

二、 创建文件

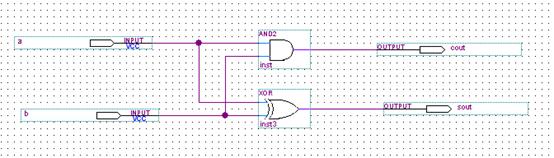

创建Block Diagram/Schematic File文件,实现一个半加器功能电路。

三、 编译工程

报告中下列数据是多少

四、仿真电路

1、创建VWF文件

2、设定“End Time”为20us

3、在VWF文件中添加Node OR Bus

4、编辑波形

5、仿真

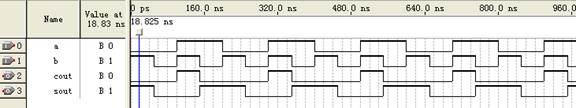

6、画出仿真结果

第二篇:Quartus仿真实验报告

实验报告

学生姓名:

指导教师:

日 期:

实验项目名称:编写相关芯片的Verilog程序并仿真

实验目的:

1.掌握基本的Verilog语法及编程思想

2.用Verilog语句编写相关芯片以及门电路程序,并调用之以实现四位二进制加法器功能

实验任务:用Verilog语句编写相关芯片以及门电路程序,并调用之以实现四位二进制加法器功能

实验原理:

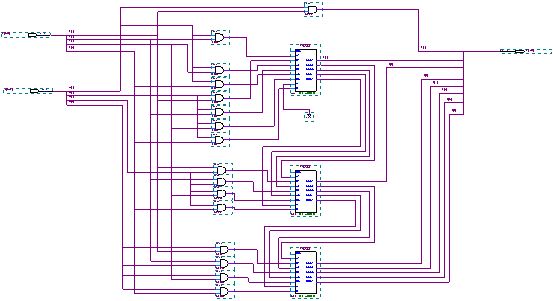

根据之前编写的Verilog HDL程序来进行Verilog语句的编写。

根据上面的电路图可得到Verilog语句如下:

主程序

module mutiply(a,b,f);

input[3:0] a,b;

output[7:0] f;

wire[7:0] f;

wire[4:1] iA,iB,iSUM,i1A,i1B,i1SUM,i2A,i2B,i2SUM;

wire iCIN,iCOUT,i1CIN,i1COUT,i2CIN,i2COUT;

and inst6(iA[1],a[1],b[0]),

inst3(iA[2],b[0],a[2]),

inst4(iA[3],a[3],b[0]),

inst5(iB[1],a[0],b[1]),

inst7(iB[2],b[1],a[1]),

inst8(iB[3],a[2],b[1]),

inst9(iB[4],a[3],b[1]),

inst10(i1B[1],b[2],a[0]),

inst11(i1B[2],a[1],b[2]),

inst18(i1B[3],a[2],b[2]),

inst19(i1B[4],a[3],b[2]),

inst24(i2B[1],a[0],b[3]),

inst16(i2B[2],b[3],a[1]),

inst23(i2B[3],a[2],b[3]),

inst25(i2B[4],a[3],b[3]),

inst20(f[0],a[0],b[0]);

assign iA[4]=0;

ADD74283 inst(iA,iB,0,iCOUT,iSUM);

assign i1A[1]=iSUM[2];

assign i1A[2]=iSUM[3];

assign i1A[3]=iSUM[4];

assign i1A[4]=iCOUT;

ADD74283 inst1(i1A,i1B,0,i1COUT,i1SUM);

assign i2A[1]=i1SUM[2];

assign i2A[2]=i1SUM[3];

assign i2A[3]=i1SUM[4];

assign i2A[4]=i1COUT;

ADD74283 inst2(i2A,i2B,0,i2COUT,i2SUM);

assign f[1]=iSUM[1];

assign f[2]=i1SUM[1];

assign f[3]=i2SUM[1];

assign f[4]=i2SUM[2];

assign f[5]=i2SUM[3];

assign f[6]=i2SUM[4];

assign f[7]=i2COUT;

endmodule

芯片程序

module ADD74283(A,B,CIN,COUT,SUM[3:0]);

input [3:0] A,B;

input CIN;

output[3:0] SUM;

output COUT;

wire [4:0] DATA;

assign DATA = A + B + CIN;

assign COUT = DATA[4];

assign SUM = DATA[3:0];

endmodule

实验步骤:

1. 根据之前编好的电路图进行Verilog语句编写。我们首先根据芯片的功能表将芯片的程序编写出来,之后就是主程序的编写。我们只用表示出各个门电路和芯片的连接关系并调用编写好的芯片程序就可以完成整个程序的编写。

2. 编好程序之后是要对其进行编译和波形仿真。

3. 仿真完成之后就进行测试。

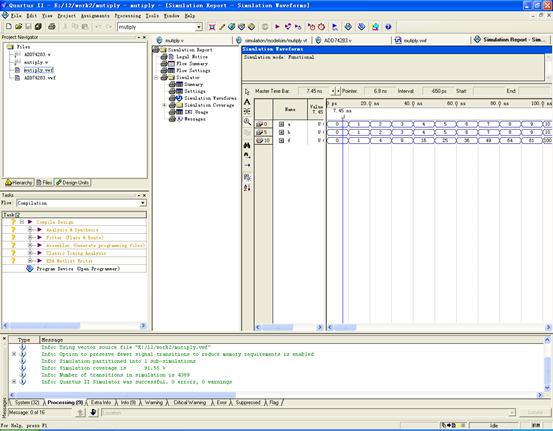

主程序仿真波形图

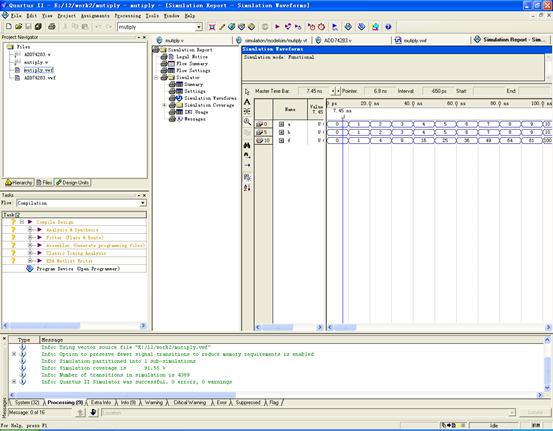

芯片ADD74283波形仿真图

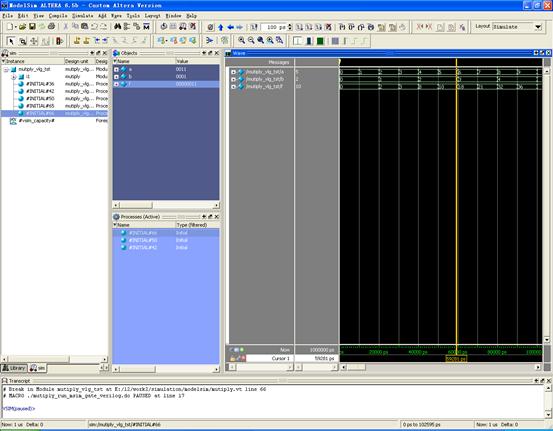

测试程序:

仿真 测试程序

Mutiply.vt

`timescale 1 ns/ 1 ns

`include "mutiply.v"

`include "ADD74283.v"

module mutiply_vlg_tst;

reg[3:0] a;

reg[3:0] b;

wire[7:0] f;

initial

begin

a = 4'd0;

b = 4'd0;

end

initial

begin

while(1)

begin

#10 a = a + 1;

end

end

initial

begin

while(1)

begin

#20 b = b + 1;

end

end

mutiply i1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.f(f)

);

initial $monitor($time,,,"f=%d",f);

initial #1000 $finish;

endmodule

实验结论:

实验总结与心得:

通过本次实验我们初步掌握了Verilog的语法及编程思想,并通过分工协作完成了程序的编写,测试及仿真的任务。由于之前对Verilog这种编程形式并不了解,加之硬件描述语言与我们以往接触过的程序语言有一定的差别,我们开始的进展并不顺利。但在阅读了一些实例程序、查阅相关资料并积极咨询老师、同学之后,我们对这种语言及其应用方式的认识逐渐明朗。在之后的编程过程中就游刃有余了。同时通过这次实验,我们也熟练掌握了Modelsim与Quartus仿真软件的使用方法。

更重要的是,这次实验加强了我们独立思考的能力,刚开始时,我们都倾向于向别人请教问题,现在慢慢改变为遇到问题首先自己思考,自己查找资料,最后再大家一起进行讨论,发现自己的不足并改正,结合大家的观点一起完成我们的实验。更让我们领会到了团队合作的重要性,再难的问题经过团队的协作最终都是可以解决的。与此同时,这次实验也让我们领会到了理论联系实践的真正意义,加深了我们对理论知识的认识,让我们得到的锻炼。