一、实验目的

1、学习和掌握半加器全加器的工作原理和设计方法。

2、熟悉EDA工具Quartus II的使用,能够熟练运用Vrilog HDL语言在

Quartus II下进行工程开发、调试和仿真。

3、掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法,

掌握层次化设计方法。

4、掌握半加器、全加器采用不同的描述方法。

二、实验内容

1、完成半加器全加器的设计,包括原理图输入,编译、综合、适配、仿真等。并将半加器电路设

置成一个硬件符号入库

2、建立更高层次的原理图设计,利用1位半加器构成1位全加器,并完成编译、综合、适配、仿真并硬件测试

3、采用图形输入法设计1位加法器分别采用图形输入和文本输入方法,设计全加器

4、实验报告:详细叙述1位全加法器的设计流程,给出各层次的原理图及其对应的仿真波形图,给出加法器的上时序分析情况,最后给出硬件测试流程和结果。

三、实验步骤

1、建立一个Project。

2、编辑一个VHDL程序,要求用VHDL结构描述的方法设计一个半加器

3、对该VHDL程序进行编译,修改错误。

4、建立一个波形文件。(根据真值表)

5、对该VHDL程序进行功能仿真和时序仿真

四、实验现象

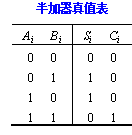

任务1:半加器真值表描述方法

代码如下:

半加器是只考虑两个加数本身,而不考虑来自低位进位的逻辑电路

S=B+A CO=AB

代码如下:

LIBRARY IEEE; --行为描述半加器

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT(a,b:IN STD_LOGIC;

so,co:OUT STD_LOGIC);

END h_adder;

Architecture FH1 OF h_adder IS

Signal abc:STD_LOGIC_vector(1 downto 0);

Begin

abc<=a&b; --并

Process(abc) --进程

begin

case abc is

WHEN "00"=>SO<='0';CO<='0';

WHEN "01"=>SO<='1';CO<='0';

WHEN "10"=>SO<='1';CO<='0';

WHEN "11"=>SO<='0';CO<='1';

WHEN OTHERS =>NULL;

END CASE;

END PROCESS;

END ARCHITECTURE FH1;

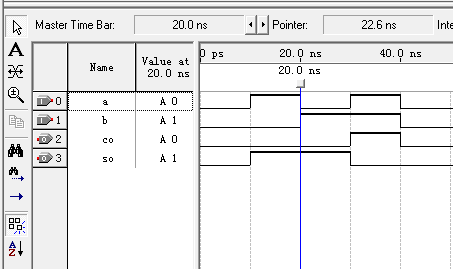

结果如下:

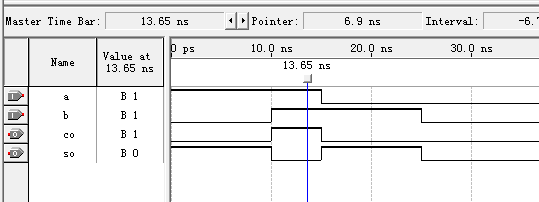

任务2:二进制加法运算规则描述

代码如下:

LIBRARY IEEE;--行为描述(抽象描述结构体的功能)

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder2 is --半加器

PORT(A,B:IN STD_LOGIC;

S,C0:OUT STD_LOGIC);

END h_adder2;

ARCHITECTURE be_half_adder OF h_adder2 IS

BEGIN

PROCESS(A,B)

BEGIN

IF(A='0' AND B='0') THEN S<='0';C0<='0';

ELSIF(A='0' AND B='1') THEN

S<='1';C0<='0';

ELSIF(A='1' AND B='0') THEN S<='1';C0<='0';

ELSE

S<='0';C0<='1';

END IF;

END PROCESS;

END be_half_adder;

结果如下:

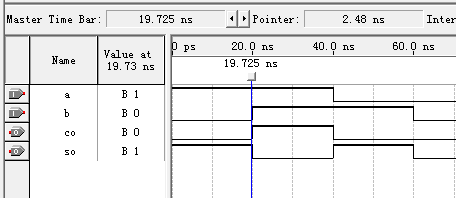

任务3:按逻辑表达式设计

代码如下:

LIBRARY IEEE; --行为描述半加器(按逻辑表达式)

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder3 IS

PORT(a,b:IN STD_LOGIC;

so,co:OUT STD_LOGIC);

END h_adder3;

Architecture FH1 OF h_adder3 IS

Begin

so<=a XOR b ;

co<=a AND b;

END ARCHITECTURE FH1;

结果如下:

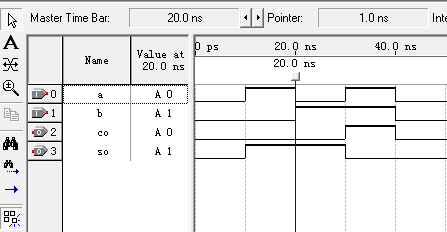

任务4:用基本单元电路与或非描述半加器

代码如下:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity h_adder4 is

port(a:in STD_LOGIC;

b:in STD_LOGIC;

sum:out STD_LOGIC;

co:out STD_LOGIC );

end h_adder4;

architecture ch4 of h_adder4 is

signal c,d:std_logic;

begin

c<=a or b;

d<=a nand b;

co<=not d;

sum<=c and d;

end architecture ch4;

结果如下:

任务5 :结构描述

代码如下:

--h_adder5

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder5 IS

PORT(A,B:IN STD_LOGIC;

co,s: OUT STD_LOGIC);

END ENTITY h_adder5;

ARCHITECTURE mix OF h_adder5 IS

COMPONENT xor21 IS

PORT(i0,i1:IN STD_LOGIC;

q:OUT STD_LOGIC);

END COMPONENT;

BEGIN

co<=A AND B;

u1: xor21 PORT MAP(i0=>A,i1=>B,q=>s); --例化

END ARCHITECTURE mix;

--xor21

--half_adder半加器,结构描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY xor21 IS

PORT(i0,i1:IN STD_LOGIC;

q: OUT STD_LOGIC);

END ENTITY xor21;

ARCHITECTURE behav OF xor21 IS

BEGIN

q<=i0 XOR i1;

END ARCHITECTURE behav;

结果如下:

五、实验体会

通过这次实验,复习了VHDL语言的应用,通过五种不同的方式,进行半加器的设计,加深了对半加器的理解,及对五种方法的运用,真值表描述方法、二进制加法运算规则描述、按逻辑表达式设计、用基本单元电路与或非描述半加器、结构描述。尤其在结构描述,元件例化部分,有了更好的理解和掌握。

第二篇:8位二进制全加器设计实验报告

EDA技术

8位二进制全加器设计实验报告

班 级:

学 号:

姓 名:

时 间:20##-12-06

目录

方法一:自己写程序........................................................................................................ 2

一、设计原理............................................................................................................ 2

二、实验程序............................................................................................................ 3

程序1:半加器描述........................................................................................... 3

程序2:一位二进制全加器设计顶层描述............................................................ 3

程序3:D触发器描述........................................................................................ 4

程序4:8位二进制加法器顶层描述.................................................................... 4

三、编译及仿真结果................................................................................................. 9

方法二:使用LPM创立元件........................................................................................... 10

一、打开MegaWizard Plug-In Manager...................................................................... 10

二、按照提示,一步步完成全加器/全减器的创建..................................................... 10

三、创建成功,生成CMP文件................................................................................ 10

四、调用CMP文件,例化元件,生成可以使用的元件。......................................... 10

实验总结:..................................................................................................................... 12

摘要

我在本实验中用顶层设计思想,用半加器、全加器、D触发器例化出八位全加器,完成了八路加法器、寄存器/锁存器的设计,上升沿触发,使用了6个数码管,分别用于显示输入A,输入B和输出,输出结果也用红灯进行了显示,溢出用绿灯表示。输入A用0~7号开关完成,输入B用10~17号开关完成,进位C用8号开关完成。

实验要求

完成八路全加器的设计,十六进制输出,上升沿触发,低电平复位,输入输出用数码管显示,用红灯显示输出,绿灯显示溢出。

方法一:自己写程序

一、设计原理

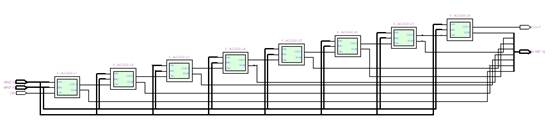

先写一个半加器,然后用两个半加器例化出一个全加器,再用八个全加器例化出一个八位全加器。原理如图。

关于上升沿触发,使用D触发器和八位全加器进行例化,D触发器接同一个时钟。最终完成上升沿触发的八位全加器的设计。

二、实验程序

程序1:半加器描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (A, B : IN STD_LOGIC;

CO, SO : OUT STD_LOGIC );

END ENTITY h_adder;

ARCHITECTURE FH1 OF h_adder IS

BEGIN

SO <= NOT (A XOR (NOT B));

CO <= A AND B;

END ARCHITECTURE FH1;

程序2:一位二进制全加器设计顶层描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (AIN, BIN, CIN : IN STD_LOGIC;

COUT, SUM : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE FD1 OF f_adder IS

COMPONENT h_adder IS

PORT (A, B : IN STD_LOGIC;

CO, SO : OUT STD_LOGIC );

END COMPONENT;

SIGNAL D, E, F : STD_LOGIC;

BEGIN

U1 : h_adder PORT MAP(A => AIN, B => BIN, CO => D, SO => E);

U2 : h_adder PORT MAP(A => E, B => CIN, CO => F, SO => SUM);

COUT <= D OR F;

END ARCHITECTURE FD1;

程序3:D触发器描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DEF1 IS

PORT (CLK : IN STD_LOGIC;

D : IN STD_LOGIC;

Q : OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF DEF1 IS

SIGNAL Q1 :STD_LOGIC;

BEGIN

PROCESS (CLK)

BEGIN

IF CLK'EVENT AND CLK = '1'

THEN Q1<=D;

END IF;

Q<=Q1;

END PROCESS;

END bhv;

程序4:8位二进制加法器顶层描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY f_adder8 IS

PORT ( AIN, BIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

ASEGIN1,ASEGIN2, BSEGIN1,BSEGIN2 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);

CIN : IN STD_LOGIC;

CLK : IN STD_LOGIC;

SUM : BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0);

SEG1 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);

SEG2 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);

COUT : OUT STD_LOGIC );

END f_adder8;

ARCHITECTURE ONE OF f_adder8 IS

COMPONENT f_adder IS

PORT (AIN, BIN, CIN : IN STD_LOGIC;

COUT, SUM : OUT STD_LOGIC );

END COMPONENT;

COMPONENT DEF1 IS

PORT (CLK : IN STD_LOGIC;

D : IN STD_LOGIC;

Q : OUT STD_LOGIC);

END COMPONENT;

SIGNAL C,C1, C2, C3,C4,C5,C6,C7: STD_LOGIC;

SIGNAL a : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL b : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL s : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL ss : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL sss : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

U1 : f_adder PORT MAP(AIN => a(0), BIN => b(0), CIN => CIN, SUM => s(0),COUT => C1);

U2 : f_adder PORT MAP(AIN => a(1), BIN => b(1), CIN => C1, SUM => s(1),COUT => C2);

U3 : f_adder PORT MAP(AIN => a(2), BIN => b(2), CIN => C2, SUM => s(2),COUT => C3);

U4 : f_adder PORT MAP(AIN => a(3), BIN => b(3), CIN => C3, SUM => s(3),COUT => C4);

U5 : f_adder PORT MAP(AIN => a(4), BIN => b(4), CIN => C4, SUM => s(4),COUT => C5);

U6 : f_adder PORT MAP(AIN => a(5), BIN => b(5), CIN => C5, SUM => s(5),COUT => C6);

U7 : f_adder PORT MAP(AIN => a(6), BIN => b(6), CIN => C6, SUM => s(6),COUT => C7);

U8 : f_adder PORT MAP(AIN => a(7), BIN => b(7), CIN => C7, SUM => s(7),COUT => C);

U9 : DEF1 PORT MAP(Q=>a(0),D=>AIN(0),CLK=>CLK);

U10 : DEF1 PORT MAP(Q=>a(1),D=>AIN(1),CLK=>CLK);

U11 : DEF1 PORT MAP(Q=>a(2),D=>AIN(2),CLK=>CLK);

U12 : DEF1 PORT MAP(Q=>a(3),D=>AIN(3),CLK=>CLK);

U13 : DEF1 PORT MAP(Q=>a(4),D=>AIN(4),CLK=>CLK);

U14 : DEF1 PORT MAP(Q=>a(5),D=>AIN(5),CLK=>CLK);

U15 : DEF1 PORT MAP(Q=>a(6),D=>AIN(6),CLK=>CLK);

U16 : DEF1 PORT MAP(Q=>a(7),D=>AIN(7),CLK=>CLK);

U17 : DEF1 PORT MAP(Q=>b(0),D=>BIN(0),CLK=>CLK);

U18 : DEF1 PORT MAP(Q=>b(1),D=>BIN(1),CLK=>CLK);

U19 : DEF1 PORT MAP(Q=>b(2),D=>BIN(2),CLK=>CLK);

U20 : DEF1 PORT MAP(Q=>b(3),D=>BIN(3),CLK=>CLK);

U21 : DEF1 PORT MAP(Q=>b(4),D=>BIN(4),CLK=>CLK);

U22 : DEF1 PORT MAP(Q=>b(5),D=>BIN(5),CLK=>CLK);

U23 : DEF1 PORT MAP(Q=>b(6),D=>BIN(6),CLK=>CLK);

U24 : DEF1 PORT MAP(Q=>b(7),D=>BIN(7),CLK=>CLK);

U25 : DEF1 PORT MAP(Q=>SUM(0),D=>s(0),CLK=>CLK);

U26 : DEF1 PORT MAP(Q=>SUM(1),D=>s(1),CLK=>CLK);

U27 : DEF1 PORT MAP(Q=>SUM(2),D=>s(2),CLK=>CLK);

U28 : DEF1 PORT MAP(Q=>SUM(3),D=>s(3),CLK=>CLK);

U29 : DEF1 PORT MAP(Q=>SUM(4),D=>s(4),CLK=>CLK);

U30 : DEF1 PORT MAP(Q=>SUM(5),D=>s(5),CLK=>CLK);

U31 : DEF1 PORT MAP(Q=>SUM(6),D=>s(6),CLK=>CLK);

U32 : DEF1 PORT MAP(Q=>SUM(7),D=>s(7),CLK=>CLK);

U33 : DEF1 PORT MAP(Q=>COUT,D=>C,CLK=>CLK);

PROCESS(CLK,AIN,BIN)

VARIABLE sSeg1 : STD_LOGIC_VECTOR(7 DOWNTO 0);

VARIABLE sSeg2 : STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

ss(3 DOWNTO 0)<=SUM(3 DOWNTO 0);

sss(3 DOWNTO 0)<=SUM(7 DOWNTO 4);

sSeg1(7 DOWNTO 0):= AIN(7 DOWNTO 0);

sSeg2(7 DOWNTO 0):= BIN(7 DOWNTO 0);

CASE ss IS

WHEN "0000" => SEG1 <= "1000000";--0

WHEN "0001" => SEG1 <= "1111001";

WHEN "0010" => SEG1 <="0100100";

WHEN "0011" => SEG1 <="0110000";

WHEN "0100" => SEG1 <="0011001";

WHEN "0101" => SEG1 <="0010010";

WHEN "0110" => SEG1 <="0000010";

WHEN "0111" => SEG1 <="1111000";

WHEN "1000" => SEG1 <="0000000";

WHEN "1001" => SEG1 <="0011000"; --9

WHEN "1010" => SEG1 <="0001000";

WHEN "1011" => SEG1 <="0000011";

WHEN "1100" => SEG1 <="1001110";

WHEN "1101" => SEG1 <="0100001";

WHEN "1110" => SEG1 <="0000110";

WHEN "1111" => SEG1 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

CASE sss IS

WHEN "0000" => SEG2 <= "1000000";--0

WHEN "0001" => SEG2 <= "1111001";

WHEN "0010" => SEG2 <="0100100";

WHEN "0011" => SEG2 <="0110000";

WHEN "0100" => SEG2 <="0011001";

WHEN "0101" => SEG2 <="0010010";

WHEN "0110" => SEG2 <="0000010";

WHEN "0111" => SEG2 <="1111000";

WHEN "1000" => SEG2 <="0000000";

WHEN "1001" => SEG2 <="0011000"; --9

WHEN "1010" => SEG2 <="0001000";

WHEN "1011" => SEG2 <="0000011";

WHEN "1100" => SEG2 <="1001010";

WHEN "1101" => SEG2 <="0100001";

WHEN "1110" => SEG2 <="0000110";

WHEN "1111" => SEG2 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

CASE sSeg1(3 DOWNTO 0) IS

WHEN "0000" => ASEGIN1 <= "1000000";--0

WHEN "0001" => ASEGIN1 <= "1111001";

WHEN "0010" => ASEGIN1 <="0100100";

WHEN "0011" => ASEGIN1 <="0110000";

WHEN "0100" => ASEGIN1 <="0011001";

WHEN "0101" => ASEGIN1 <="0010010";

WHEN "0110" => ASEGIN1 <="0000010";

WHEN "0111" => ASEGIN1<="1111000";

WHEN "1000" => ASEGIN1 <="0000000";

WHEN "1001" => ASEGIN1 <="0011000"; --9

WHEN "1010" => ASEGIN1 <="0001000";

WHEN "1011" => ASEGIN1 <="0000011";

WHEN "1100" => ASEGIN1 <="1001010";

WHEN "1101" => ASEGIN1 <="0100001";

WHEN "1110" => ASEGIN1 <="0000110";

WHEN "1111" => ASEGIN1 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

CASE sSeg1(7 DOWNTO 4) IS

WHEN "0000" => ASEGIN2 <= "1000000";--0

WHEN "0001" => ASEGIN2 <= "1111001";

WHEN "0010" => ASEGIN2 <="0100100";

WHEN "0011" => ASEGIN2 <="0110000";

WHEN "0100" => ASEGIN2 <="0011001";

WHEN "0101" => ASEGIN2 <="0010010";

WHEN "0110" => ASEGIN2 <="0000010";

WHEN "0111" => ASEGIN2<="1111000";

WHEN "1000" => ASEGIN2 <="0000000";

WHEN "1001" => ASEGIN2 <="0011000"; --9

WHEN "1010" => ASEGIN2 <="0001000";

WHEN "1011" => ASEGIN2 <="0000011";

WHEN "1100" => ASEGIN2 <="1001010";

WHEN "1101" => ASEGIN2 <="0100001";

WHEN "1110" => ASEGIN2 <="0000110";

WHEN "1111" => ASEGIN2 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

CASE sSeg2(3 DOWNTO 0) IS

WHEN "0000" => BSEGIN1 <= "1000000";--0

WHEN "0001" => BSEGIN1 <= "1111001";

WHEN "0010" => BSEGIN1 <="0100100";

WHEN "0011" => BSEGIN1 <="0110000";

WHEN "0100" => BSEGIN1 <="0011001";

WHEN "0101" => BSEGIN1 <="0010010";

WHEN "0110" => BSEGIN1 <="0000010";

WHEN "0111" => BSEGIN1<="1111000";

WHEN "1000" => BSEGIN1 <="0000000";

WHEN "1001" => BSEGIN1 <="0011000"; --9

WHEN "1010" => BSEGIN1 <="0001000";

WHEN "1011" => BSEGIN1 <="0000011";

WHEN "1100" => BSEGIN1 <="1001010";

WHEN "1101" => BSEGIN1 <="0100001";

WHEN "1110" => BSEGIN1 <="0000110";

WHEN "1111" => BSEGIN1 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

CASE sSeg2(7 DOWNTO 4) IS

WHEN "0000" => BSEGIN2 <= "1000000";--0

WHEN "0001" => BSEGIN2 <= "1111001";

WHEN "0010" => BSEGIN2 <="0100100";

WHEN "0011" => BSEGIN2 <="0110000";

WHEN "0100" => BSEGIN2 <="0011001";

WHEN "0101" => BSEGIN2 <="0010010";

WHEN "0110" => BSEGIN2 <="0000010";

WHEN "0111" => BSEGIN2<="1111000";

WHEN "1000" => BSEGIN2 <="0000000";

WHEN "1001" => BSEGIN2 <="0011000"; --9

WHEN "1010" => BSEGIN2 <="0001000";

WHEN "1011" => BSEGIN2 <="0000011";

WHEN "1100" => BSEGIN2 <="1001110";

WHEN "1101" => BSEGIN2 <="0100001";

WHEN "1110" => BSEGIN2 <="0000110";

WHEN "1111" => BSEGIN2 <="0001110";

WHEN OTHERS =>NULL;

END CASE;

END PROCESS;

--U1 : f_adder PORT MAP(AIN => AIN(0), BIN => BIN(0), CIN => CIN, SUM => SUM(0), COUT => C1);

--U2 : f_adder PORT MAP(AIN => AI N(1), BIN => BIN(1), CIN => C1, SUM => SUM(1), COUT => C2);

--U3 : f_adder PORT MAP(AIN => AIN(2), BIN => BIN(2), CIN => C2, SUM => SUM(2), COUT => C3);

--U4 : f_adder PORT MAP(AIN => AIN(3), BIN => BIN(3), CIN => C3, SUM => SUM(3), COUT => C4);

--U5 : f_adder PORT MAP(AIN => AIN(4), BIN => BIN(4), CIN => C4, SUM => SUM(4), COUT => C5);

--U6 : f_adder PORT MAP(AIN => AIN(5), BIN => BIN(5), CIN => C5, SUM => SUM(5), COUT => C6);

--U7 : f_adder PORT MAP(AIN => AIN(6), BIN => BIN(6), CIN => C6, SUM => SUM(6), COUT => C7);

--U8 : f_adder PORT MAP(AIN => AIN(7), BIN => BIN(7), CIN => C7, SUM => SUM(7), COUT => COUT);

END ONE;

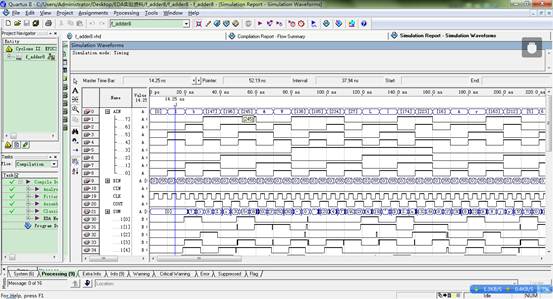

三、编译及仿真结果

程序波形仿真图

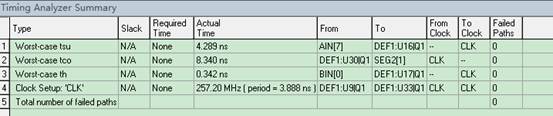

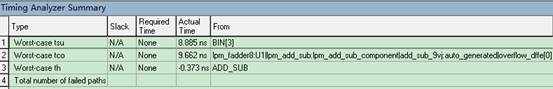

时间分析

方法二:使用LPM创立元件

一、打开MegaWizard Plug-In Manager

二、按照提示,一步步完成全加器/全减器的创建

三、创建成功,生成CMP文件

四、调用CMP文件,例化元件,生成可以使用的元件。

元件例化程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY lpm_fadder1 IS

PORT(ADD_SUB,CIN,CLK: IN std_logic;

AIN,BIN: IN std_logic_vector(7 DOWNTO 0);

SUM : OUT std_logic_vector(7 DOWNTO 0);

OVERFLOW,COUT : OUT std_logic

);

END ENTITY lpm_fadder1;

ARCHITECTURE add_sub OF lpm_fadder1 IS

component lpm_fadder8

PORT

(

add_sub : IN STD_LOGIC ;

cin : IN STD_LOGIC ;

clock : IN STD_LOGIC ;

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

cout : OUT STD_LOGIC ;

overflow : OUT STD_LOGIC ;

result : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

end component;

BEGIN

U1: lpm_fadder8 PORT MAP(add_sub=>ADD_SUB,cin=>CIN,clock=>CLK,dataa=>AIN,datab=>BIN,cout=>COUT,overflow=>OVERFLOW,result=>SUM);

END ARCHITECTURE add_sub;

最后生成的加法器如图:

时间分析

实验总结:

本次试验让我熟悉了VHDL语句的综合运用,提高了我的逻辑思维能力。虽然写了三个晚上,但十六进制转十进制输出显示依然未能完成。此次我的程序非常长,分析其原因,是元件的底层例化没有写好,应该把D触发器首先例化到一位全加器上,然后用一位全加器例化八位全加器。这样就可节省近二十行代码。

经过时间分析发现,自己写的代码用时12.5ns,使用元件向导用时18ns,所以自己写的代码运行起来比较省时!