实验题目

实验报告正文一律使用A4打印纸打印或手写,页眉上标明“《XXXX》课程实验”字样。页面设置上边距2.5cm,下边距2 cm,右边距2 cm(左装订),多倍行距1.25倍。正文用宋体5号字,页眉和页脚同宋体小5号字并居中。

1、 实验内容

用MAX+plus II 10.1设计一位全加器

2、 实验目的与要求

设计一位全加器,并且熟悉MAX+plus II 10.1使用环境。

3、 实验环境

MAX+plus II 10.1

4、 设计思路分析(包括需求分析、整体设计思路、概要设计)

用两个半加器和一个或门,设计一位全加器。

5、 详细设计

一位全加器可以用两个半加器和一个或门连接而成,半加器由一个与门,一个非门,同或门来实现。

在MAX+plus II 10.1环境操作步骤如下:

1、半加器的设计 2、全加器的设计 3、分配管脚 4、编译

5、仿真 6、下载 7、观察结果

6、 实验结果与分析

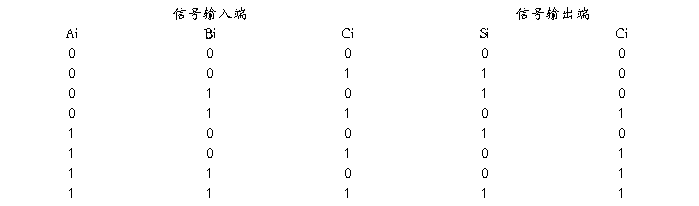

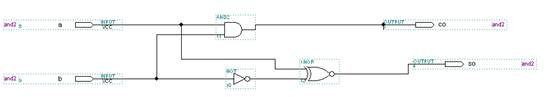

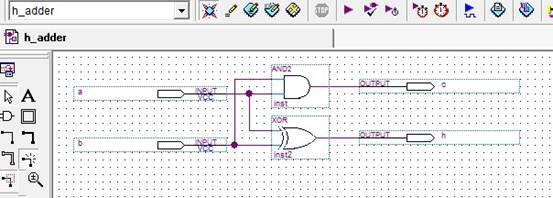

半加器原理图

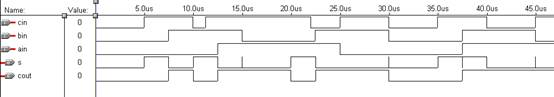

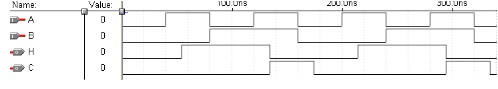

半加器波形图

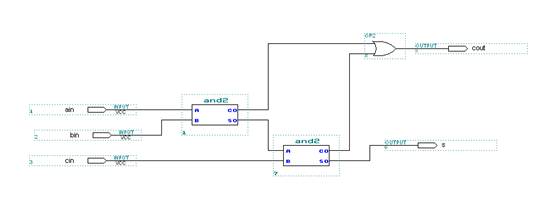

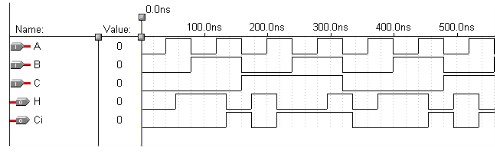

全加器原理图

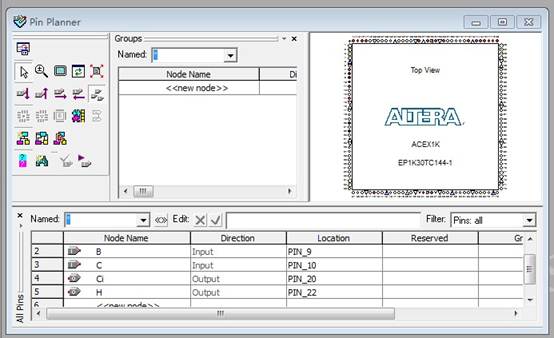

全加器波形图

7、 实验体会与建议

通过这次实验课的学习,我学会了MAX+plus 的使用。了解了半加器和全加器的设计原理和在MAX+plus中的实现方法。在操作过程中虽然遇到了很多的困难,但在同学的帮助下都克服了。同学的帮助在学习的过程中是很重要的。

第二篇:一位全加器的实验报告

专业班级: 2010级电子2班

学号: 10200207 姓名:周 娟

EDA 技术实验报告

实验项目名称:在QuartusII中用原理图输入法设计1位加法器

实验日期: 20##-5-10 实验成绩:

实验评定标准:

一、 实验目的

熟悉利用QuartusII的原理图输入方法设计简单组合电路,掌握层次化设 计的方法。

二、 实验器材

电脑一台 ,试验箱一个

三、 实验内容(实验过程)

1.按照附录四介绍的方法与流程,完成半加器的设计

,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此半加器电路设置成一个硬件符号入库。

1)半加器的设计原理图入下图所示:

2)半加器的仿真图如下:

2.重复步骤1的操作,利用步骤1得到的半加器硬件元件,完成全加器的电路图设计,编译,仿真:

1)全加器的设计原理图如下:

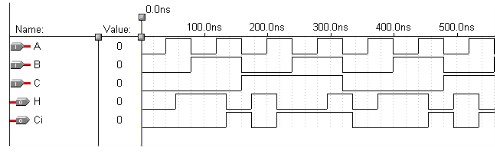

2)全加器的仿真结果如下:

3.对照试验箱上所用芯片,在电脑上选择好目标芯片,绑定引脚。

4.最后把试验箱接好电源盒计算机接口,把程序下载到目标芯片上,接着就可以在试验箱上通过按键和发光二极管来验证实验的正确性。

四、 实验程序

1.或门逻辑描述:

library ieee;

use ieee.std_logic_1164.all;

entity or2 is

port(a,b :in std_logic ;

o:out std_logic );

end entity or2

architecture fhl of or2 is

begin

o<=a or b;

end architecture fh1;

1.半加器的描述:

library ieee;

use ieee.std_logic_1164.all;

entity h_adder is

port(a,b :in std_logic ;

h,c:out std_logic );

end entity h-dder

architecture fhl of h_adder is

begin

h<=(a or b)AND(a nand b);

c<=not(a nand b);

end architecture fh1;

2.一位全加器的设计描述:

library ieee;

use ieee.std_logic_1164.all;

entity f_adder is

port(A,B,C :in std_logic ;

H,Ci:out std_logic );

end entity f-dder

architecture fdl of f_adder is

component h_adder

port(a,b:in std_logic;

c,h:out std_logic);

end component

component or2

port(a,b:in std_logic;

o,out std_logic);

end component

signal d e f: std_logic;

port map

begin

u1:h-adder port map(a=>A b=>B c=>d h=>e)

u2:h_adder port map(a=>e b=>C c=>f h=>Ci)

u3:or port map(a=>d b=>f o=>H)

end architecture fd1;

五、 实验仿真、结果及分析

1.仿真结果如图:

2.结果及分析:

该一位加法器是由两个半加器组成,在半加器的基础上,采用元件的调用和例化语句,将元件连接起来,而实现全加器的VHDL编程和整体功能。全加器包含两个半加器和一或门,1位半加器的端口a和b分别是两位相加的二进制输入信号,h是相加和输出信号,c是进位输出信号。构成的全加器中,A,B,C分别是该一位全加器的三个二进制输入端,H是进位端,Ci是相加和输出信号的和,上图是根据试验箱上得出的结果写出的真值表: