4位全加器的设计实验报告

班级:通信12-2班 学号:12090216 姓名:韦建萍

一、实验目的

熟悉利用Quartus II 的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个4位全加器的设计,掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二、 实验原理

一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出 cout 与相邻的高位加法器的最低进位输入信号 cin 相接。

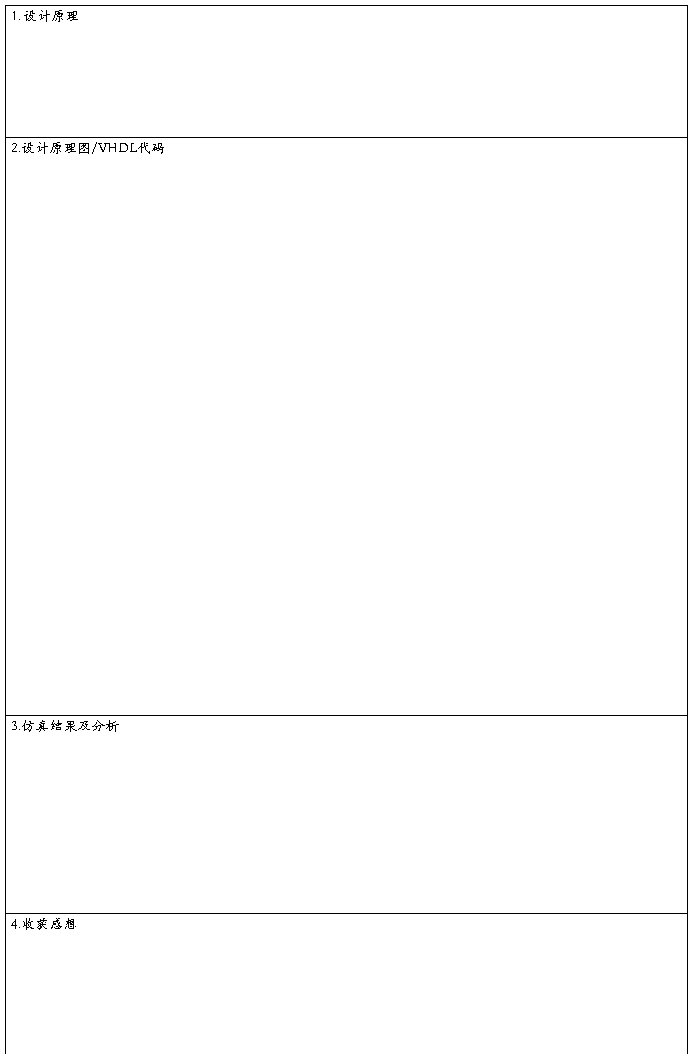

加法器举例说明:设M = 1101 ,N = 1110,CIN=0, 则

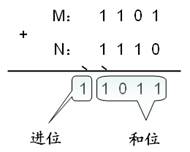

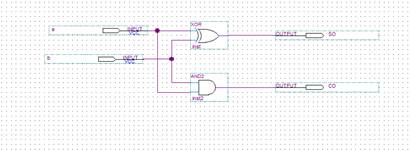

1、 半加器(设其名为h_adder)的电路:

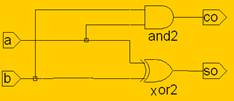

2、 全加器(设其名为f_adder)的电路:

三、实验内容和步骤

1、完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真;

半加器电路原理设计图如图:

半加器电路仿真图如图:

全加器电路原理设计图如图:

全加器电路仿真图如图:

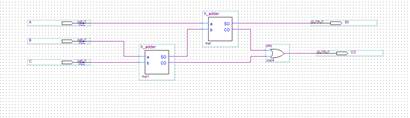

2、建立一个更高层次的原理图设计,利用以上获得的1位全加器构成4位全加器,并完成编译、综合、适配、仿真。

4位全加器电路原理图如图:

4位全加器仿真图如图:

四、仿真分析及心得体会

仿真分析:

四位全加器S0为和位,C0为进位,当a0=1,b0=1时,S0=0,C0=1,就是和位为零,进位进1。以此类推,当a1=1,b1=0,C0=1时,和位S0=0,进位C0=1。

实验体会:

通过这次实验让我学会了如何掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程,利用Quartus II 的原理图输入方法设计简单组合电路,掌握层次化设计的方法。

第二篇:实验一 《八位全加器设计》实验报告纸

学生实验报告

学生实验报告