《四位全加器》

实验报告

题目:___ ____

学号:___ _____

姓名:____ _______

教师:____ ____

1、 实验内容

四位全加器的设计与实现。

2、 实验目的与要求

利用MAX+plusII实现四位全加器并且验证实验内容。

3、 实验环境

MAX+plus II 10.1

4、 设计思路分析(包括需求分析、整体设计思路、概要设计)

一个4位全加器可以由4个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

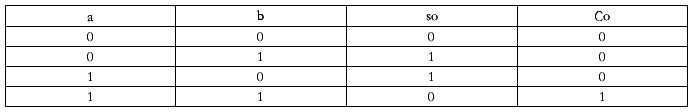

半加器描述:

根据半加器真值表可以画出半加器的电路图。

5、 详细设计

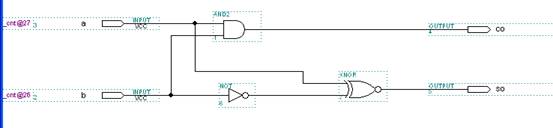

A) 半加器设计:

1)新建一个设计文件,使用原理图设计方法设计。

2)将所需元件全部调入原理图编辑窗,所需元件依次为:input 2个;output 2个;and2 1个;xnor 1个;not 1个。

3)依照下图连接好各元件

4)保存为h-adder将当前设计文件设置成工程文件。

5)编译

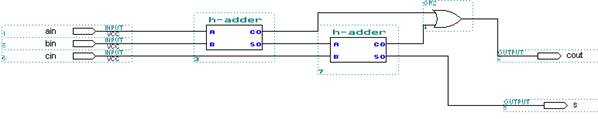

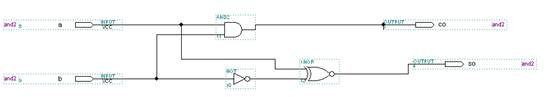

B) 一位全加器的实现:

1) 一位全加器可以由两个半加器和一个或门连接而成,因而可以根据半加器的电路原理图或真值表写出1位全加器的VHDL描述。.

2) 依照以下原理图连接好全加器:

其中有两个原件(h-adder)为刚刚设计好的半加器.其他原件为:input 3个, output 2个, or2 1个.

3) 保存为f-adder设置成工程文件并选择目标器件为 EPF10K20TC144.4

4) 编译

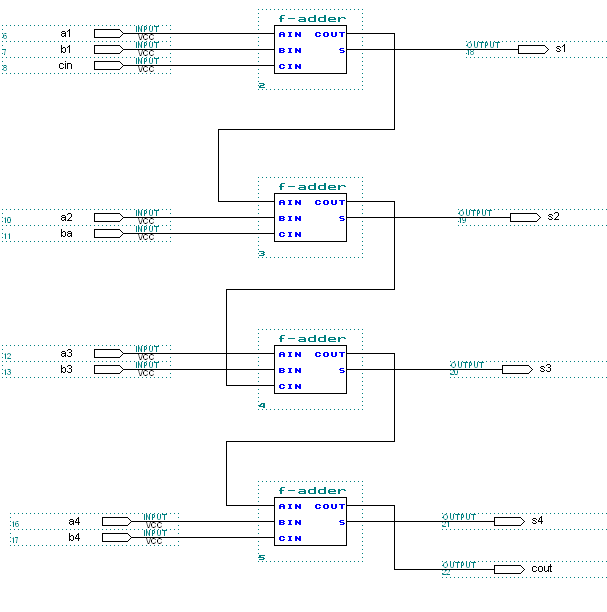

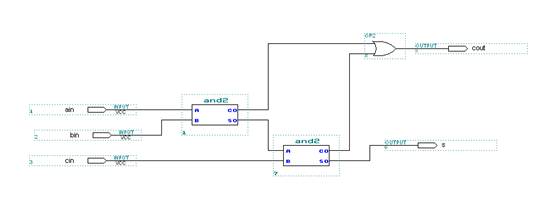

C) 四位全加器的实现

1) 4位全加器可以看做四个1位全加器级联而成,首先采用基本逻辑门设计一位全加器,而后通过多个1位全加器级联实现4位全加器。

2) 依照以下原理图连接好全加器。、

其中有四个元件为一位全加器(f-adder),其余为九个input元件;五个output元件。、

4)编译通过。

6、 实验结果与分析

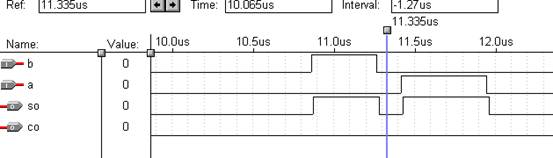

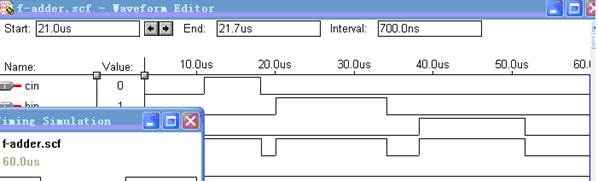

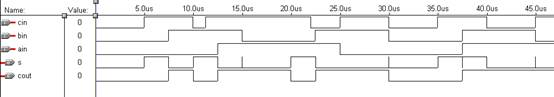

1)建立波形图进行半加器、一位全加器和四位全加器的波形观察,

2)设定仿真时间为60.0us。

3)运行仿真器得到下面波形图:

半加器:

一位全加器:

四位全加器:

4)测量全加器的输入输出延时量是得到下图:

5)进行引脚锁定后再编译一次,再将编程下载.

7、 实验体会与建议

通过此次实验熟悉运用掌握了MAX+plusII的操作环境。这次设计的四位全加器也可以称作四位串行进位加法器,这种加法器的最大缺点就是运行速度慢,在最不利的情况下,做一次加法运算需要经过四个全加器的传输延迟时间(从输入加数到输出稳定状态建立起来所需要的时间)才能得到稳定可靠的运算结果。

第二篇:一位全加器实验报告

实验题目

实验报告正文一律使用A4打印纸打印或手写,页眉上标明“《XXXX》课程实验”字样。页面设置上边距2.5cm,下边距2 cm,右边距2 cm(左装订),多倍行距1.25倍。正文用宋体5号字,页眉和页脚同宋体小5号字并居中。

1、 实验内容

用MAX+plus II 10.1设计一位全加器

2、 实验目的与要求

设计一位全加器,并且熟悉MAX+plus II 10.1使用环境。

3、 实验环境

MAX+plus II 10.1

4、 设计思路分析(包括需求分析、整体设计思路、概要设计)

用两个半加器和一个或门,设计一位全加器。

5、 详细设计

一位全加器可以用两个半加器和一个或门连接而成,半加器由一个与门,一个非门,同或门来实现。

在MAX+plus II 10.1环境操作步骤如下:

1、半加器的设计 2、全加器的设计 3、分配管脚 4、编译

5、仿真 6、下载 7、观察结果

6、 实验结果与分析

半加器原理图

半加器波形图

全加器原理图

全加器波形图

7、 实验体会与建议

通过这次实验课的学习,我学会了MAX+plus 的使用。了解了半加器和全加器的设计原理和在MAX+plus中的实现方法。在操作过程中虽然遇到了很多的困难,但在同学的帮助下都克服了。同学的帮助在学习的过程中是很重要的。