实验一:四位全加器实验报告

实验日期:2014.4.15 学生姓名:陆小辉(学号:1228402025)指导老师:黄秋萍

加法器是数字系统中的基本逻辑器件,是构成算数运算电路的基本单元。1位加法器有全加器和半加器两种。多位加法器构成方式有并行进位方式和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度较快;串行进位加法器是将全加器级联构成多位加法器。并行进位加法器通常比串行进位加法器占用更多的资源,随着位数的增多,相同位数的并行进位加法器比串行进位加法器的资源占用差距快速增大。因此,在工程中使用加法器时,要在速度与容量之间寻求平衡。

一、设计要求:

设计

四位全加器,完成相应的功能。可采用并行进位方式和串行进位方式,可采用三种常用建模方式中的任意一种。

设计

四位全加器,完成相应的功能。可采用并行进位方式和串行进位方式,可采用三种常用建模方式中的任意一种。

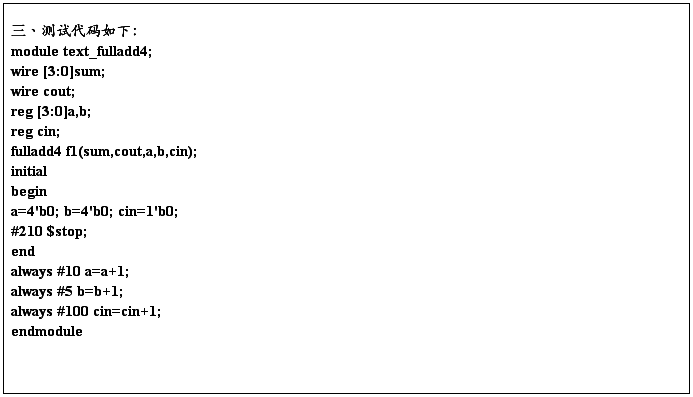

二、设计代码如下:(此处采用数据流建模)

module fulladd4(sum,cout,a,b,cin);

output [3:0]sum;

output cout;

input [3:0]a,b;

input cin;

assign {cout,sum}=a+b+cin;

endmodule

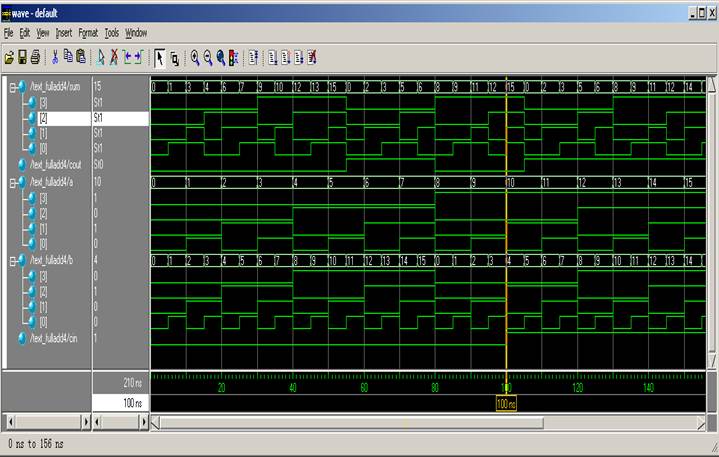

四、仿真波形如下:

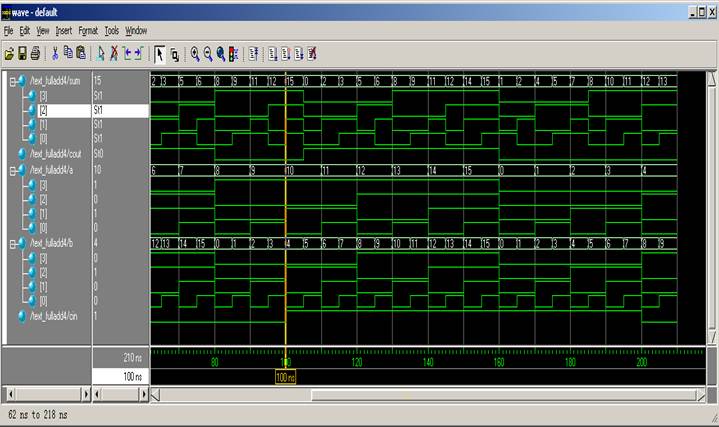

续图

第二篇:一位全加器实验报告

实验题目

实验报告正文一律使用A4打印纸打印或手写,页眉上标明“《XXXX》课程实验”字样。页面设置上边距2.5cm,下边距2 cm,右边距2 cm(左装订),多倍行距1.25倍。正文用宋体5号字,页眉和页脚同宋体小5号字并居中。

1、 实验内容

用MAX+plus II 10.1设计一位全加器

2、 实验目的与要求

设计一位全加器,并且熟悉MAX+plus II 10.1使用环境。

3、 实验环境

MAX+plus II 10.1

4、 设计思路分析(包括需求分析、整体设计思路、概要设计)

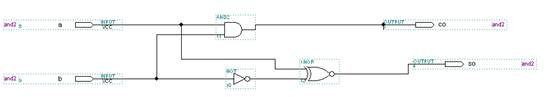

用两个半加器和一个或门,设计一位全加器。

5、 详细设计

一位全加器可以用两个半加器和一个或门连接而成,半加器由一个与门,一个非门,同或门来实现。

在MAX+plus II 10.1环境操作步骤如下:

1、半加器的设计 2、全加器的设计 3、分配管脚 4、编译

5、仿真 6、下载 7、观察结果

6、 实验结果与分析

半加器原理图

半加器波形图

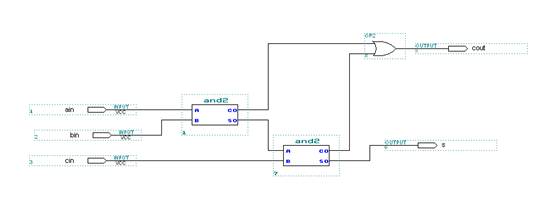

全加器原理图

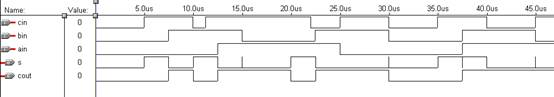

全加器波形图

7、 实验体会与建议

通过这次实验课的学习,我学会了MAX+plus 的使用。了解了半加器和全加器的设计原理和在MAX+plus中的实现方法。在操作过程中虽然遇到了很多的困难,但在同学的帮助下都克服了。同学的帮助在学习的过程中是很重要的。