《集成电路版图设计》

课内实验

学 院: 信息学院

专业班级:

学 号:

学生姓名:

指导教师:

模拟集成电路版图设计

集成电路版图是电路系统与集成电路工艺之间的中间环节,是一个不可少的重要环节。通过集成电路的版图设计,可以将立体的电路系统变为一个二维的平面图形,再经过工艺加工还原于基于硅材料的立体结构。因此,版图设计是一个上承的电路系统,下接集成电路芯片制造的中间桥梁,其重要性可见一斑。但是,集成电路版图设计是一个令设计者感到困惑的一个环节,我们常常感到版图设计似乎没有什么规矩,设计的经验性往往掩盖了设计的科学性,即使是许多多年版设计经验的人有时候也说不清楚为何要这样或者那样设计。在此,集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。但它更需要设计者的创造性,空间想象力和耐性,需要设计者长期工作的经验和知识的积累,需要设计者对日异月新的集成电路发展密切关注和探索。一个优秀的版图设计者对于开发超性能的集成电路是极其关键的。在版图的设计和学习中,我们一直会面临

匹配技术

降低寄生参数技术

熟悉电路作用(功能,频率)

电流密度的计算(大电流和小电流的电流路径以及电流流向)

等这些基本,它们也是最重要的问题。

版图的设计,从半导体制造工艺,到最后的后模拟过程都是非常关键的,里面所涉及的规则有1500——2000条,一些基本问题的解决方法和设计的调理化都将在下面提及。

模拟集成电路版图设计流程:

阅读研究报告

理解电路原理图

了解电路的作用

熟悉电流路径晶大小

知道匹配器件

明白电路中寄生,匹配,噪声的产生及解决方案

对版图模块进行平面布局

对整个版图进行平面布局

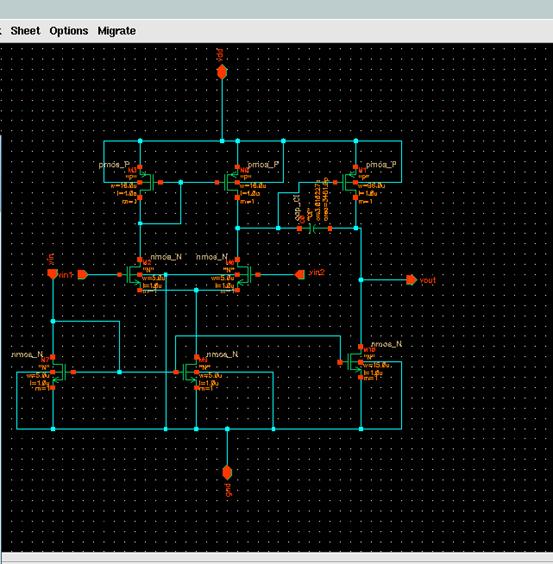

熟练运用cadence软件进行版图绘制

Esd的保护设计

进行drc与lvs检查

整理整个过程中的信息时刻做记录

注意在设计过程中的交流

集成电路制造工艺

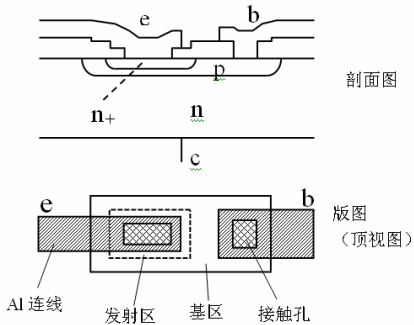

双极工艺:

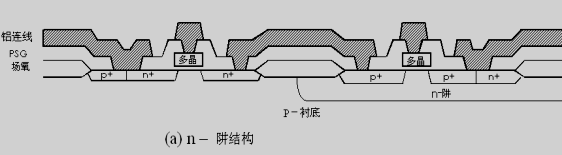

Cmos(p阱)工艺:

版图设计经验总结:

1 查看捕捉点设置是否正确.08工艺为0.1,06工艺为0.05,05工艺为0.025.

2 Cell名称不能以数字开头.否则无法做DRACULA检查.

3 布局前考虑好出PIN的方向和位置

4 布局前分析电路,完成同一功能的MOS管画在一起

5 对两层金属走向预先订好。一个图中栅的走向尽量一致,不要有横有竖。

6 对pin分类,vdd,vddx注意不要混淆,不同电位(衬底接不同电压)的n井分开.混合信号的

路尤其注意这点.

7 在正确的路径下(一般是进到~/opus)打开icfb.

8 更改cell时查看路径,一定要在正确的library下更改,以防copy过来的cell是在其他

library下,被改错.

9 将不同电位的N井找出来.

10更改原理图后一定记得check and save

11完成每个cell后要归原点

12 DEVICE的 个数 是否和原理图一至(有并联的管子时注意);各DEVICE的尺寸是否和原理图一至。一般在拿到原理图之后,会对布局有大概的规划,先画DEVICE,(DIVECE之间不必用最小间距,根据经验考虑连线空间留出空隙)再连线。画DEVICE后从EXTRACTED中看参数检验对错。对每个device器件的各端从什么方向,什么位置与其他物体连线 必须 先有考虑(与经验及floorplan的水平有关).

13如果一个cell调用其它cell,被调用的cell的vssx,vddx,vssb,vddb如果没有和外层cell连起来,要打上PIN,否则通不过diva检查.尽量在布局低层cell时就连起来

14尽量用最上层金属接出PIN。

15接出去的线拉到cell边缘,布局时记得留出走线空间.

16金属连线不宜过长;

17电容一般最后画,在空档处拼凑。

18小尺寸的mos管孔可以少打一点.

19 LABEL标识元件时不要用y0层,mapfile不认。

20管子的沟道上尽量不要走线;M2的影响比M1小.

21电容上下级板的电压注意要均匀分布;电容的长宽不宜相差过大。可以多个电阻并联.

22多晶硅栅不能两端都打孔连接金属。

23栅上的孔最好打在栅的中间位置.

24U形的mos管用整片方形的栅覆盖diff层,不要用layer generation的方法生成U形栅.

25一般打孔最少打两个

26Contact面积允许的情况下,能打越多越好,尤其是input/output部分,因为电流较大.但如果contact阻值远大于diffusion则不适用.传导线越宽越好,因为可以减少电阻值,但也增加了电容值.

27薄氧化层是否有对应的植入层

28金属连接孔可以嵌在diffusion的孔中间.

29两段金属连接处重叠的地方注意金属线最小宽度

30连线接头处一定要重叠,画的时候将该区域放大可避免此错误。

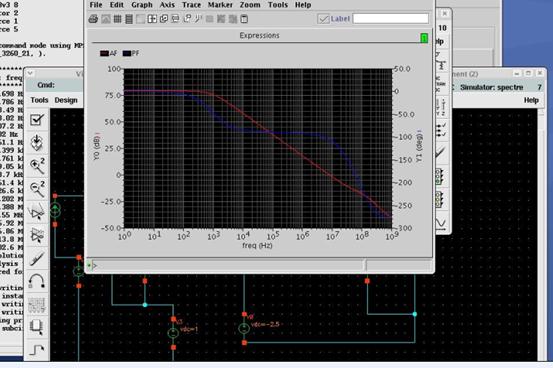

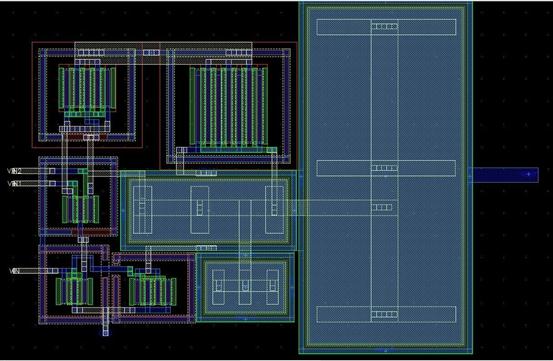

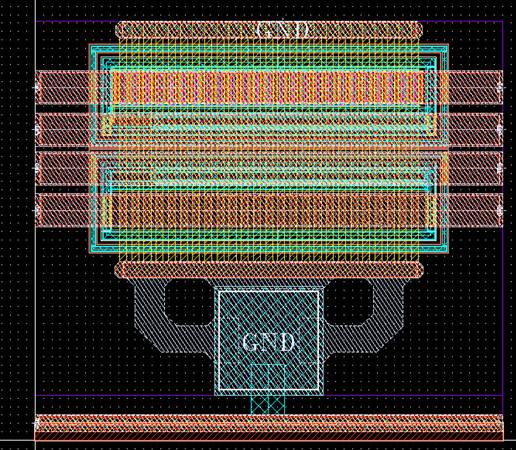

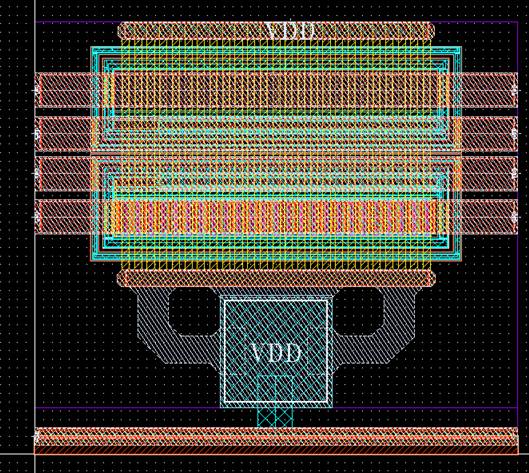

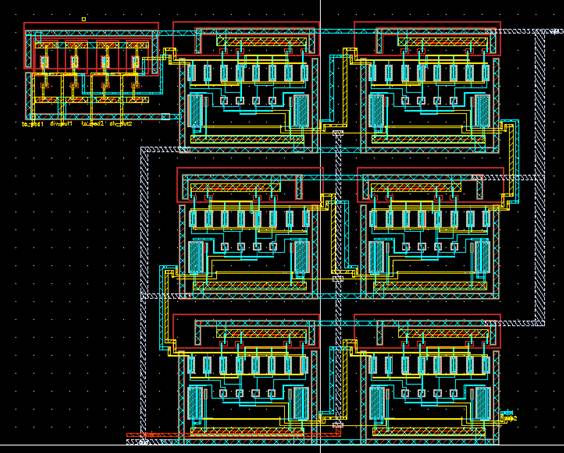

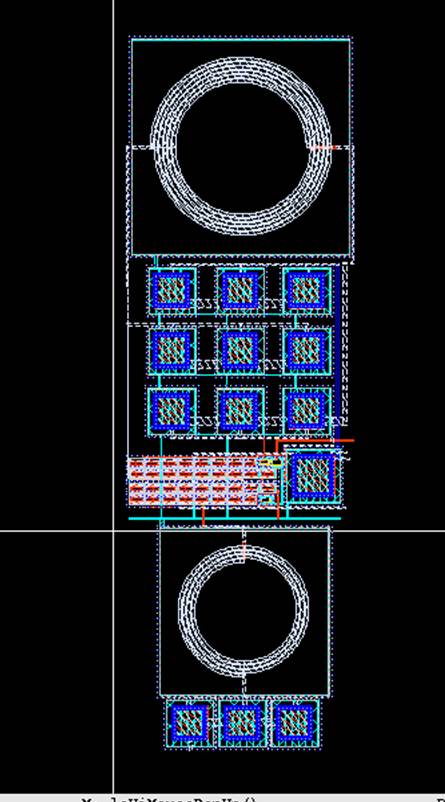

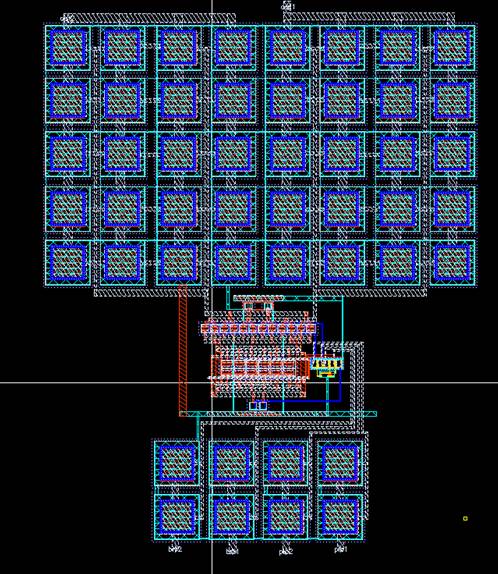

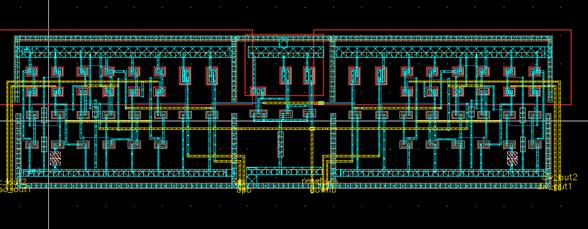

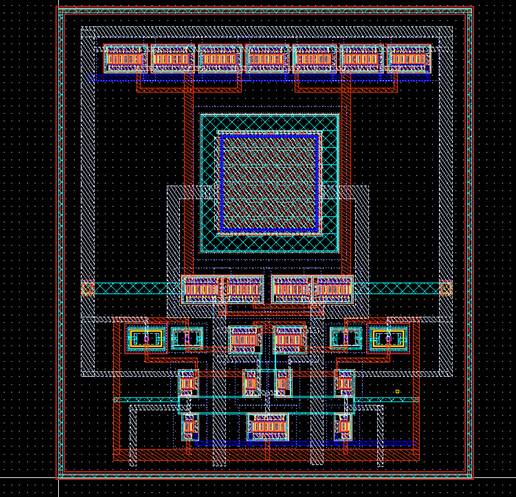

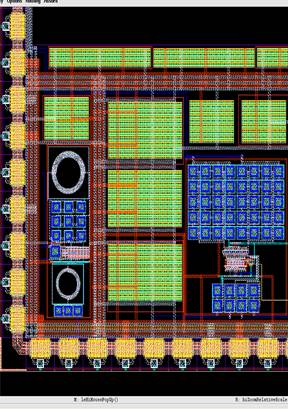

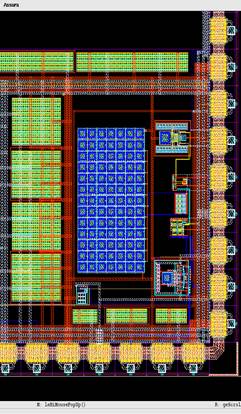

附图:

参考文献:

1.《cmos模拟集成电路版图设计》

2.《半导体制造技术》

3.《集成电路版图基础》

4.《cmos circuit design,layout and simulation》

5.《the art of analog layout》

第二篇:集成电路版图技巧总结

四.版图技巧Z

1.对敏感线的处理

对敏感线来说,至少要做到的是在它的走线过程中尽量没有其他走线和它交叉。因为走线上的信号必然会带来噪声,交错纠缠的走线会影响敏感线的信号。

对于要求比较高的敏感线,则需要做屏蔽。具体的方法是,在它的上下左右都连金属线,这些线接地。比如我用M3做敏感线,则上下用M2和M4重叠一层,左右用M3走,这些线均接地。等于把它像电缆一样包起来。

2.匹配问题的解决

电路中如果需要匹配,则要考虑对称性问题。比如1:8的匹配,则可以做成3×3的矩阵,“1”的放在正中间,“8”的放在四周。这样就是中心对称。如果是2:5的匹配,则可以安排成AABABAA的矩阵。

需要匹配和对称的电路器件,摆放方向必须一致。周围环境尽量一致。

3.噪声问题的处理

噪声问题处理的最常用方法是在器件周围加保护环。

Nmos管子做在衬底上 因此周围的guardring是Pdiff,在版图上是一层PPLUS,上面加一层DIFF,用CONTACT连M1。Pdiff接低电位。

Pmos管子做在NWELL里面 因此周围的GUARDING是Ndiff,在版图上先一层NPLUS,上面加一层DIFF,用CONTACT连M1。Ndiff接高电位。

在一个模块周围为了和其他模块隔离加的保护环,用一圈NWELL,里面加NDIFF,接高电位。

电阻看类型而定,做在P衬底上的周围接PDIFF型guarding接地;做在NWELL里面的则周围接NDIFF型guarding接高电位。

各种器件,包括管子,电容,电感,电阻都要接体电位。

如果不是RF型的MOS管,则一般尽量一排N管一排P管排列,每排或者一堆靠近的同类型管子做一圈GUARDING,在P管和N管之间有走线不方便打孔的可以空出来不打。

4.版图对称性

当电路需要对称的时候,需要从走线复杂度,面积等方面综合考虑。

常见的对称实现方式:

一般的,画好一半,折到另一半去,复制实现两边的对称。

如果对称性要求高的,可以用质心对称的方式,把管子拆分成两个,四个甚至更多。

如把一个管子拆成两个 可以AB

BA

的方式

如果有四个管子,可以各拆成三个,用ABCDABCDABCD的方式

五.布局布线

布局布线是一个全局问题。在画较大的电路时候是很重要的。首先确定各模块的位置,在确定位置的时候需要考虑的问题主要有:各输入输出之间的连线最短,最方便;各模块接出去连PAD的各端口方便;高频线距离尽量短;输入输出之间相隔比较远等。这些问题需要在着手画各模块之前先有个安排。在画好各模块后摆放时会做调整,但大局不变。

连线一般的规则是单数层金属和双数层金属垂直,比如一三五层连水平;二四六层连垂直。但这样的主要目的是各层能方便走线,排得密集。所以也不是死规则,在布线较稀疏的情况下可以做适量变通。

在布线时最重要的问题是考虑电路的各支路电流问题。首先要明确各支路电路的峰值,这样就能确定金属线的最小宽度。确保整条支路不会被电流过大而烧断。当然连线也不能太宽,这样的话电容会大。

电路中如果画到电流源可以离得较远,因为电流源理想的时候电阻无穷大,这就意味着电流源连出来的线可以长一些,因为不需考虑连线太长电阻太大的问题。

六.版图流程

整体布局——各模块布局——模块布线——各模块通过DRC,LVS——整体布线——整体通过DRC,LVS,通过天线效应DRC——提取后仿参数

DRC:在线的有DIVA 只需把.rul文件放在相应目录下 直接在线跑

Dracula:非在线

LVS:也有DIVA,DRACULA等。本次使用calibre进行lvs。具体流程如下:

1. 版图生成GDS文件。在icfb窗口的“file”中选“export”的“stream”

2. 生成netlist。在ADS中的“tool”里export网表

3. 用LVS文件,修改其中对应的layyout和netlist文件名称。

把以上三个文件放在同一目录下。

EDA中在该目录下跑CALIBRE

命令: calibre(空格)-lvs(空格)做lvs的文件名

在生成的lvs.rep中找错误。

注意:layout中,gnd和vdd作为pin。Pin只用.txt对应的metal标识。

在跑好LVS后,要在版图上对应的地方找到可能的错误,需要以下步骤:

在icfb窗口: load“~/calivre.skl”

Calibre-Setup-Socket…

在lvs路径 caliber -rve svdb&

在【svdb】窗口 setup-layout viewer

七.ELLA的心得

1.关于电路的问题

画模拟版图首先要注意的是线宽问题。每条支路上的电流是多少要问清电路设计者。对于比较大电流的支路,线宽一定要满足电流,但也不能太宽,否则寄生电容肯定会大。可以采用几条金属线上下重叠并联的方式,这样的话宽度小了电流又能满足。

画版图的时候也不能一味埋头苦画,远抱着质疑的态度。比如判断设计者给出的电流是否正确可信,给出的结构和器件尺寸是否合理等。这就需要对电路知识有很好的了解,懂电路来画版图才有意思。

2.关于ESD的问题

一般的工艺模型里可能会提供ESD模型。但是本次流片并没有。ESD需要自己画。参考文件中给出ESD的设计规则,有些是DRC做不出来的,需要自己注意。ESD需要在输入输出口,电源和地之间,不同的电源之间等都做,而且结构不同。

对于栅直接接到PAD的电路,需要特别注意。在栅往外接的时候接一个200欧姆的电阻,这样电流进来的时候不容易将栅极击穿。在该PAD两边最好放GND和VDD的pad,这样电流容易往两边走。

3.关于滤波电容问题

在电路的空隙地方填入滤波电容。具体接法是:

NMOS管的源漏接地,栅接电源;

PMOS管的源漏接电源,栅接地。

本次电路中滤波电容采用mm模型,管子做成10um×10um,四周围相应的GUARDRING。

4.关于天线效应

第一层金属在接栅时候如果面积很大就会收集离子使得电位升高而击穿栅氧层。此时应该将第一层金属断开,往上连接,最好连到最高层。如果需要走第一层就再连回来。

5.关于电源线和地线问题

电源线和地线一般在60um左右。但是线宽超出20um工艺上有问题因此需要打孔。本次电路的处理方式是没有打孔,将线接成三根20um的从pad引出来,布线时,按照

Vdd gnd vdd gnd vdd gnd 这样间隔的布线。

整个版图的电源和地线呈网格状,这样压降小,稳定。

6.学会看参考文件

总的文件是guideline 里面有一些规定。不像DRC那样必须遵守。这次没有仔细看。

关于DRC,LVS,LPE等的相关文件在给出的文件里都有。DESIGN RULE 等文件需要在画之前先有了解。

在画之前应该把这些信息过目一遍,心中有数。至少知道什么信息在什么地方。

7. 本次流片所画版图:

画版图需要极大的耐心和细心。最主要的是心态保持平和轻松,切忌烦躁。即使时间紧迫,也不能抱着得过且过的心态,一定要尽量做到最优。(水瓶座的完美主义这里发挥了作用)

虽然之前大家都说一个这样的chip一个月是非常紧张的,最后还是按时完成。只要相信自己能做到,就一定真的能做到。除此之外,还需要很强的韧性。如果看到DRC出来几万个错误也不能崩溃。其实可能都是一个问题造成的,逐一改过来就可以啦!!