第二篇:专用集成电路设计实验报告

专用集成电路设计实验报告

班 级:

学 号:

姓 名:

指导教师:

2011.07.04

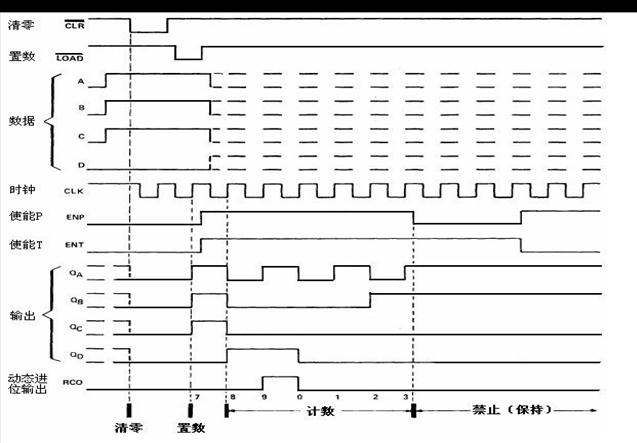

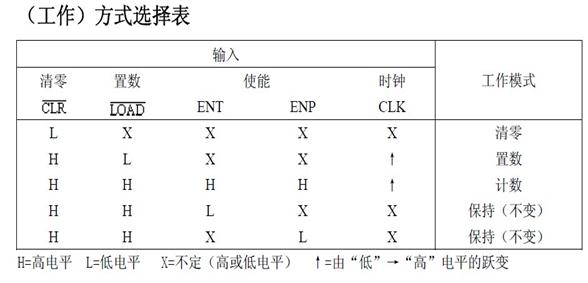

一、74160功能:

① 异步清零

当 =0时,不管其他输入端的状态如何(包括时钟信号CP ),

=0时,不管其他输入端的状态如何(包括时钟信号CP ),

计数器输出将被直接置零,称为异步清零。

② 同步并行预置数

在 =1的条件下,当

=1的条件下,当 =0、且有时钟脉冲CLK 的上升沿作用时,A、B、C、D 输入端的数据将分别被QA~QD所接收。由于这个置数操作要与CLK上升沿同步,且DA、DB、DC、DD的数据同时置入计数器,所以称为同步并行置数。

=0、且有时钟脉冲CLK 的上升沿作用时,A、B、C、D 输入端的数据将分别被QA~QD所接收。由于这个置数操作要与CLK上升沿同步,且DA、DB、DC、DD的数据同时置入计数器,所以称为同步并行置数。

③ 保持

在 =

= =1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

=1的条件下,当ENT=ENP=0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。需要说明的是,当ENP=0, ENT=1时,进位输出C也保持不变;而当ENT=0时,不管ENP状态如何,进位输出RCO=0。

④ 计数

当 =

= =ENP=ENT=1时,74160处于计数状态。

=ENP=ENT=1时,74160处于计数状态。

这种同步可预置十进计数器是由四个D 型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。对所有触发器同时加上时钟,使得当计数使能输入和内部门发出指令时输出变化彼此协调一致而实现同步工作。这种工作方式消除了非同步(脉冲时钟)计数器中常有的输出计数尖峰。缓冲时钟输入将在时钟输入上升沿触发四个触发器。

74LS160时序图:

真值表:

二、用VHDL进行功能仿真

1、程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY LS160 IS PORT(

data:IN std_logic_vector(3 downto 0);

clk,ld,enp,ent,clr:IN std_logic;

count:buffer std_logic_vector(3 downto 0);

rco:OUT std_logic); END LS160;

ARCHITECTURE behavior OF LS160 IS

BEGIN

rco<='1'when(count="1001"and enp='1'and ld='1'and clr='1')else'0'; PROCESS(clk,clr,enp,ent,ld)

BEGIN

IF(CLR='0')THEN count<="0000";

ELSIF(clk'event and clk='1')THEN

IF(ld='1')THEN

IF(enp='1')THEN

IF(ent='1')THEN

IF(count="1001")THEN

count<="0000"; ELSE

count<=count+1; END IF;

ELSE

count<=count;

END IF;

ELSE

count<=count;

END IF;

ELSE

count<=data;

END IF;

end if;

END PROCESS;

END behavior;

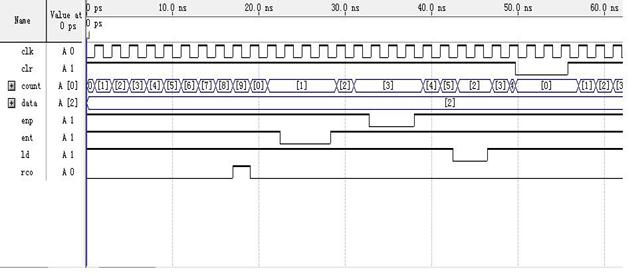

2、仿真波形: