暨南大学本科实验报告专用纸

课程名称 数字逻辑电路实验 成绩评定 实验项目名称 中规模集成电路功能测试及应用 指导教师 实验项目编号0806003804 实验项目类型 验证型实验地点 学生姓名 学号 学院 电气信息学院 系 专业 实验时间 2013 年6 月 3日上午~ 6 月3日上午温度 ℃湿度

中规模集成电路功能测试及应用

一、实验目的

1.熟悉数据选择器和译码器的逻辑功能。

2.实现数据选择器和译码器的扩展应用。

二、实验器件、设备和仪器

1.双4选1数据选择器74LS153 1片

2.双2:4线译码器74LS139 2片

3.6反相器74LS04 1片

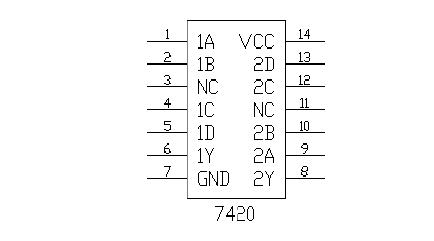

4.双4输入与非门74LS20 1片

5. 数字信号显示仪

6.数字万用表UT56 1台

7. TDS-4数字系统综合实验平台

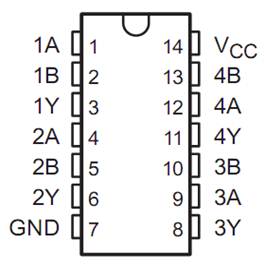

芯片引脚图

1

三、实验内容

1.验证译码器的逻辑功能

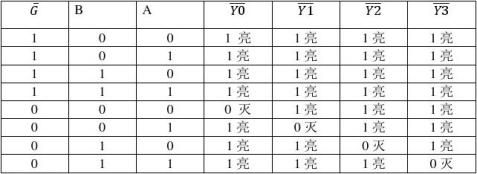

(1)静态测试方法测试验证74LS139 中一个2:4线译码器的逻辑功能。 验证步骤:

① G、B、A端信号的接实验台逻辑电平开关, 4个译码输出引脚Y0~Y3接逻辑电平指示灯。② G、B、A改变引脚、产生8种组合,观测指示灯的显示状态, 自拟表格记录测试结果。 ③对照74LS139 逻辑真值表,验证芯片74LS139

=0时,该译码器才能工作,即? 为使能端,且低电平有效。当? =1只有?

时,信号输出端都是高电平。当芯片使能时,BA输入的编码相应的输出端 ???为

低电平,其余都是高电平。

综上可知,74LS139 具有2:4线译码器的逻辑功能

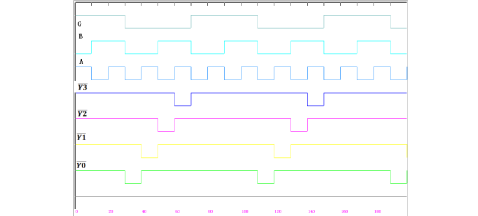

(2)动态测试方法测试验证74LS139 中一个2:4线译码器的逻辑功能。

2

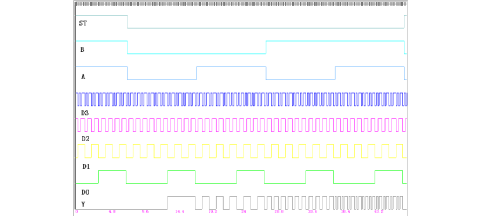

G,B,A的输入信号直接从可编辑数字波形发生器BCD码中选择,如下所示

由上图,可知:

=0时, BA输入的编码相应的输出端 当????为低电平,其余都是高电平 =1时,信号输出端都是高电平 当?

2.逻辑部件的扩展

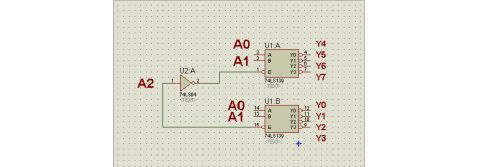

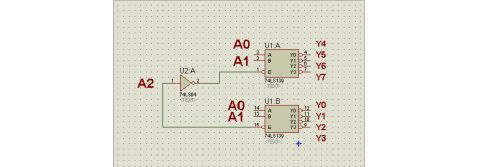

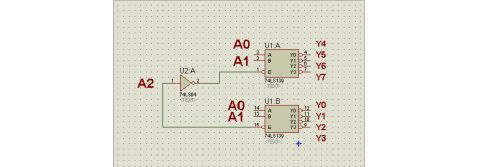

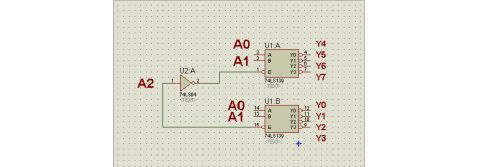

将74LS139双2:4线译码器器扩展为3:8线译码器。

①画出扩展3:8线译码器逻辑图,连接组装逻辑电路。

②测试电路功能。

逻辑电路如上所示

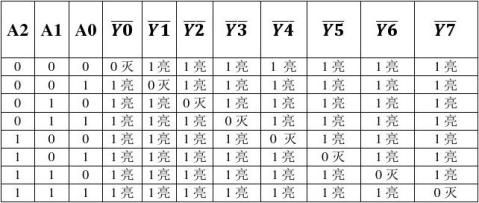

静态测试:地址控制信号可采用用逻辑电平(即手控),输出用逻辑电平指示灯显示,测试结果如下表所示

3

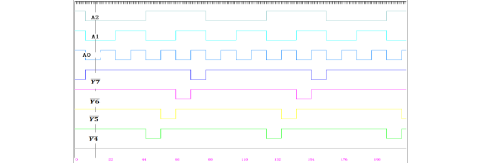

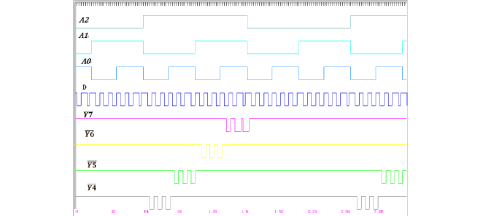

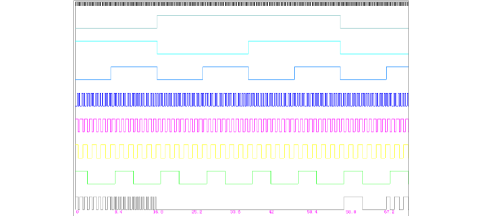

地址控制信号直接从编辑数字波形发生器BCD码中选择合适的输入信号,选择频率为50KHz,由数字逻辑信号仪测出全部输入和输出信号波形图,记录分析时序图,时序图如下所示

结果是正确的

③根据测试结果,可以得出电路的逻辑功能是正确的

4

3. 用译码器设计实现测试1:8线数据分配器

①画出用74LS139译码器芯片设计的1 : 8线数据分配器

②根据 1 : 8线数据分配器电路逻辑图逻路组装电路 ,用静态测试方法对电路进

功能表如上表所示

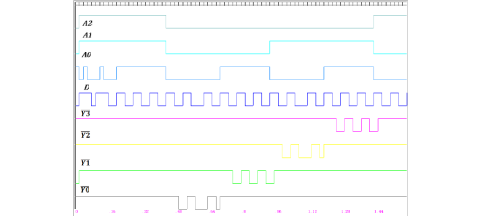

动态测试如下所示: 5

④根据静态测试所得功能表以及动态测试所得的时序图, 可以知道:

=D,其余输出端为1,当输入地址编码A2A1A0时,相对应的输出端 ???????所

以该电路的逻辑功能是正确的

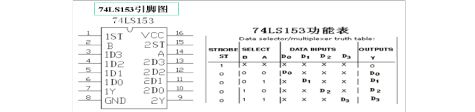

4. 测试验证数据选择器逻辑功能

采用动态测试方法测试74LS153 中一个4选1数据选择器的逻辑功能。 测试验证步骤:

① 4个数据输入引脚D3~D0分别接实验台上的2MHz、1MHz、500kHz

、

6

l00kHz脉冲源。

②使能端ST电平和地址输入端B、A信号可直接从编辑数字波形发生器BCD码中选择合适的测试输入信号或者可由编辑数字波形发生器编辑产生8种不同的地址控制信号和使能输入信号组合,选择频率为50KHz,由数字逻辑信号仪测出全部输入和输出信号波形图,记录分析其时序图。

时序图如下所示:

③用数字信号显示仪同时观察、记录和分析数据选择器输入、使能端ST电平和地址输入端B、A信号与输出波形逻辑关系,

上面第一张图中可以看出当使

7

能端ST=0时,Y=???,第二张图可以看出当使能端ST=1时,Y=0。所以该芯片具有4选1数据选择器的逻辑功能。

四、问题回答

1.三态缓冲器不仅能组成的单向总线,而且还能构成双向总线,数据选择器能组成怎样的总线电路?

答:单向的;数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如第四个小实验中有四路数据D0~D3,通过选择控制信号 A、B(地址码)从四路数据中选中某一路数据送至输出端Y即是数据选择器的一种应用,所以数据选择器只能进行单向的总线电路,不能构成双向的总线

2. 列举出中规模集成电路中输入使能端的作用?

答:使能端有三个作用:(1)消除译码器输出尖峰干扰(冒险),即使能电平的有效出现在A,B稳定之后;有效使能电平的撤除在A,B再次改变之前(避免A,B, 在变化过程中引起输出端产生瞬时干扰脉冲)。(2)能够使用使能端进行芯片的逻辑功能扩展,例如第二个小实验,应用了使能端,将双2:4线译码器扩展为了3:8线译码器。(3)方便构造其他功能的电路,如第三个小实验,利用了使能端,将74LS139译码器芯片设计成1 : 8线数据分配器

3. 用测试功能的方法判断芯片好坏,具体测试方法有哪两种?

答:动态测试和静态测试

4.数字电路实验难免出现问题,你认为产生问题的主要原因有哪几种?你怎样避免此类问题的发生。

答:(1)实验器材或者实验平台坏了,包括芯片坏了,导线断了,整个平台坏了等等硬件设施问题,本实验室这个问题还是挺严重的

(2)主观上的错误,包括电路设计错误,连线错误,记录数据错误,或者其他种种操作错误都有可能导致实验失败

5.看组合逻辑电路图,分析电路逻辑功能 。

8

答:左边是2:4的译码器,当BA=00,右边的三态门只有最上边的选通,Y=1; 同理,当BA=01时,Y=0;当BA=10时,Y为频率为0.1MHz的信号;当BA=11时,Y为频率为1MHz的信号。所以该电路的功能是4选1的数据选择器

6.记录实验中出现的问题,分析原因,写出解决方法。

答:本次实验还是挺顺利的,中间出现一些连线错误的情况,但经过查找最后都解决了

五、实验总结

通过本实验熟悉了数据选择器和译码器的逻辑功能。同时学会了如何实现数据选择器和译码器的扩展应用。

9

第二篇:数字电路实验报告 实验4

实验四 计数器

一、 实验目的

1.熟悉计数器的工作原理,掌握中规模(MSI)计数器的逻辑功能。

2. 掌握用MSI计数器实现任意模计数器的方法。

二、 实验设备和器件

1、数字逻辑电路实验板 1块

2、74HC(LS)00(四二输入与非门) 1片

3、74HC(LS)160(4位十进制计数器) 2片

三、 实验原理

时序逻辑电路是数字电路中另一类重要电路。时序逻辑电路的特点,就是任意时刻的输出不仅取决于该时刻的输入信号,而且与信号作用前电路所处的状态有关。

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频以及其它特定的逻辑功能。计数器种类很多。根据计数制的不同,分为二进制计数器和十进制计数器。实现四个状态变量十进制计数功能的电路称为4位十进制计数器。利用集成计数器芯片可方便地构成任意模计数器,方法有反馈清零法和反馈置数法两种。

实验用器件管脚介绍:

1、74HC(LS)00(四二输入与非门)管脚如下图所示。

2、74HC(LS)160(4位十进制计数器)管脚如下图所示。

四、 实验内容与步骤

1、测试74HC(LS)160的逻辑功能(基本命题)

例如,74HC(LS)160工作于计数模式时,接通电源后,利用数码管显示说明其确为模10计数器。

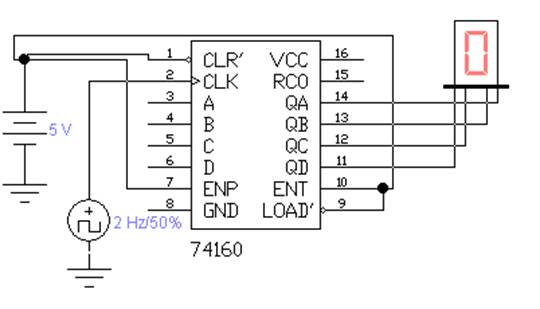

1.1电路图

1.2实验结果

数码管显示从0——9循环,每0.5秒改变一次。

2、74HC(LS)160构成模6计数器(基本命题)

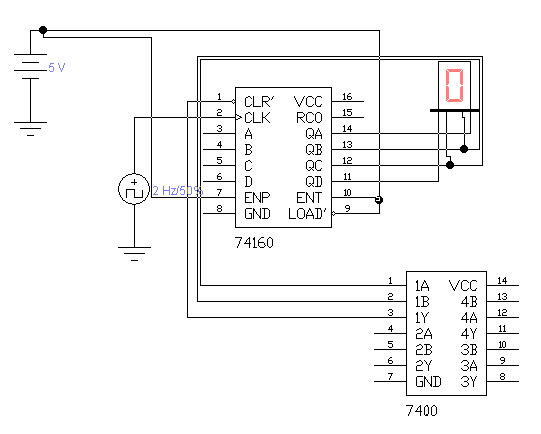

设计用与非门74HC(LS)00及计数器74HC(LS)160实现模6计数器的实验电路图,搭接电路,利用数码管显示说明其确为模6计数器。

2.1电路图

2.2实验结果

数码管显示从0——5循环,每0.5秒改变一次。

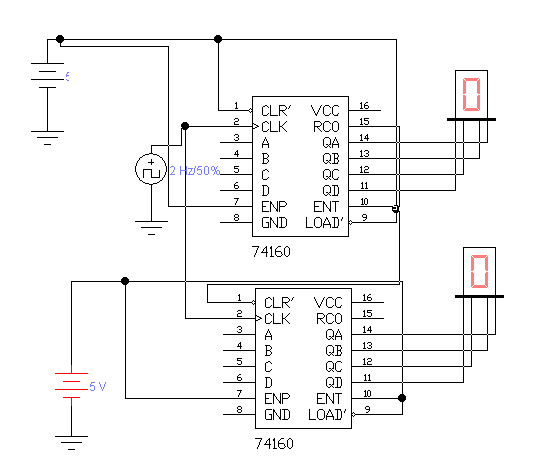

3、74HC(LS)160构成模100计数器(扩展命题)

因为一片74HC(LS)160为模10,所以直接两片级联即为模100计数器。设计用计数器74HC(LS)160实现模100计数器的实验电路图,搭接电路,利用数码管显示说明其确为模100计数器。

3.1电路图

3.2实验结果

数码管显示从0——99循环,每0.5秒改变一次。

五、 实验注意事项

集成电路要轻插轻拔!

六、 出现的问题。

实验做得比较顺利,除了实验三的线路特别不稳定(不知道是不是接触不良),而且很多同学都有这个问题,明明线路接的是对的,但轻轻一碰就不能正常显示了。

然后就是做报告用workbench模拟的时候,电路连的应该没问题,但是数码管不走,看数码管参数的时候,有很多选项, 都试了一下,还是不行,那些选项的意思也不是很清楚。。。