集成电路设计综合实验

实验报告

学 院: 电气与控制工程学院

班 级:

姓 名:

学 号: 1

完成日期:

目录

一.实验要求..............................................2

二.实验目的..............................................2

三.实验内容..............................................2

(一)版图提出电路并分析仿真...............................3

3.1.1提取电路图.........................................3

3.1.2电路测试图.........................................3

3.1.3电路版图...........................................4

3.1.4电路仿真图.........................................4

3.1.5功能分析...........................................5

(二)CMOS结构的二选一选择器..............................5

3.2.1实验步骤...........................................5

3.2.2二选一电路图.......................................6

3.2.3电路测试图.........................................6

3.2.4电路版图...........................................7

3.2.5仿真结果...........................................7

四.心得体会.......................................8

一:实验要求

完成并掌握D触发器,二选一电路的电路设计和版图设计。

二:实验目的

1.学习并掌握集成电路设计集程(正,反方向);

2.培养从版图设计提取电路的能力;

3.学习版图设计技巧,方法;

4.学习并掌握电路仿真分析能力;

5.复习和巩固基本数字单元电路设计。

三:实验内容

3.1反向提取给定电路模块,画出电路原理图,分析功能,并进行仿真验证,画出电路版图,完成DRC验证。

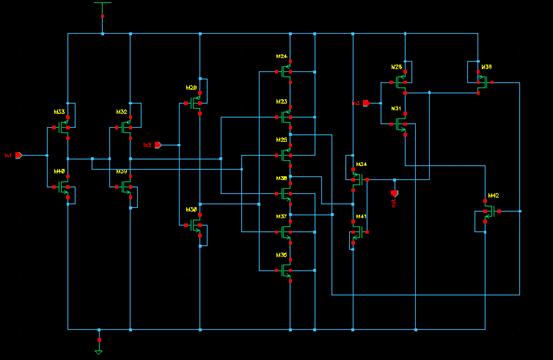

3.1.1提取电路图

3.1.2电路测试图

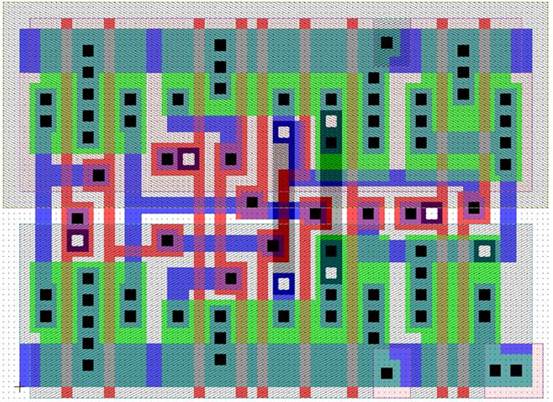

3.1.3电路版图

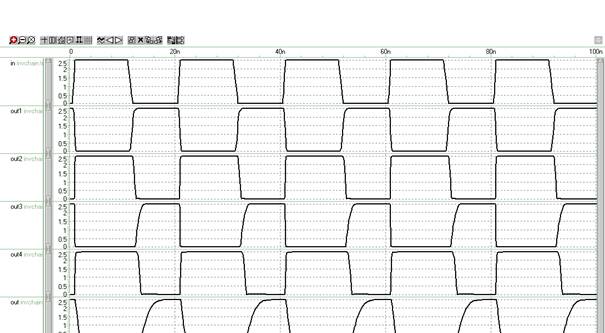

3.1.4电路仿真图

3.1.5功能分析

使能端控制输出,当为高电平时输出与输入有关,当为低电平时输出全部被置“1”。

当使能端有效时,在时钟在低电平的时候,输出与输入反向。在时钟高电平时输出保持不变。

所以是低电平有效的D触发器。

3.2设计一个CMOS结构的二选一多路选择器,并仿真分析,完成其版图设计及DRC验证。

3.2.1实验步骤

1.分析二选一多路选择器功能

2.构建CMOS结构电路图

3.在cadence上仿真电路

4.分析结果是否满足功能要求

5.如果有误调整电路

6.根据电路图绘制版图

7.对版图进行DRC验证并修改

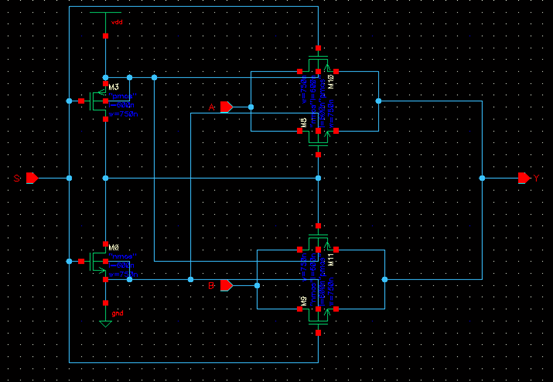

3.2.2二选一电路图

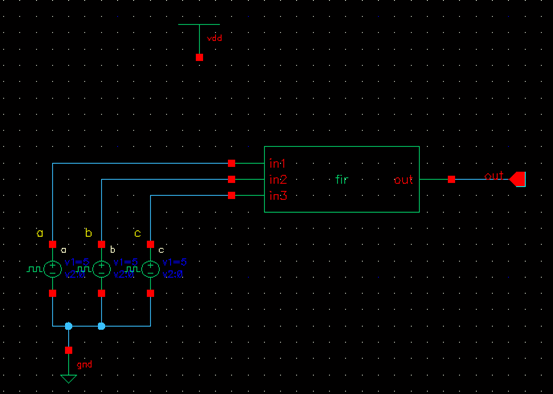

3.2.3电路测试图

3.2.4电路版图

3.2.5仿真结果

四:心得体会

在这为期两周的课程中我学到了很多,刚开始在版图中提取电路图遇到了困难,不知道如何下手,经过老师和同学的指导渐渐发现了规律,先确定管子,再弄清楚连线关系,就可以提取出电路图了。接下来分析电路功能时,可以先把整个电路分成几个模块,比如把反相器、与非门等简单电路提取出来,这样整个电路就变得明了了。然后经过电路仿真,再列出真值表就能知道电路功能了。

在画版图前要先了解所使用的设计规则,这样在可以减少验证时的错误。我所遇到的困难之一是分不清工艺层次,不能在画版图时想象出MOS管的立体结构,还有调节尺寸是一个很繁琐的工作,不过随着熟练度的提升我克服了这些问题。

通过这次学习我对cadence系统的理解进一步加深,并且学到了更多的专业知识,相信这对以后的工作能带来更多帮助,感谢老师的悉心指导和同学们的真诚帮助。

第二篇:数字集成电路原理标准实验报告

电子科技大学微电子与固体电子学院

标 准 实 验 报 告

(实验)课程名称 数字集成电路原理

学 号:2010032020024

姓 名:李天生

指导老师:张驰

20##年7月8日

电子科技大学教务处制表

电子科技大学

实 验 报 告

学生姓名: 学号: 指导教师:

实验地点: 实验时间:

一、实验室名称:

二、实验项目名称:数字集成电路最优延迟设计与分析

三、实验学时:3

四、实验原理

1、Hspice的具体功能

电路级和行为级仿真

直流特性分析、灵敏度分析

交流特性分析

瞬态分析

电路优化(优化元件参数)

温度特性分析

噪声分析

傅立叶分析

Monte Carlo, 最坏情况,参数扫描,数据表扫描

功耗、各种电路参数(如H参数、T参数、s参数)等可扩展的性能分析

2、Hspice界面

Hspice是一个在cmd shell窗口中运行的程序,无图形化界面;

Hspice的输入网单文件是一个有特定格式的纯文本文件——可在任意的文本编辑工具中编辑;

Hspice的输出也是一系列纯文本文件,根据不同分析要求,输出不同扩展名的文件。如:.lis .mt0 .dat .smt等。

HSPICE 的运行: 在运行HSPICE之前,应该首先登录到SUN工作站上,并确保你的使用HSPICE的权限和环境变量已设好。

打开一个“终端”窗口,然后进入到你的工作目录下。输入行命令运行。

hspice有两种工作模式:提示行模式和非提示行模式

3、Hspice两种工作模式

a)、提示行模式

键入hspice, 然后回车;

系统会提示你输入一些参数,比如

Enter input file name:

此时输入你的HSPICE网表文件,缺省的扩展名为.sp

Enter output file name or directory: [<filename.lis>]

缺省值为输入HSPICE网表文件名加上.lis扩展名。但.sp 和.lis 并不是必须。除此之外,还有一些参数(这些参数的隐含值一般不需要更改),直接回车即可。等你按照系统的提示确定所有的参数后,HSPICE就开始运行。

b)、非提示行模式

一般情况下的输入举例如下:

hspice demo.sp 或者

hspice demo.sp => demo.lis

4、Hspice输出

输出文件:一系列文本文件

*.ic :initial conditions for the circuit

*.lis :text simulation output listing

*.mt0,*.mt1… :post-processor output for MEASURE statements

*.pa0 :subcircuit path table

*.st0 :run-time statistics

*.tr0 ,*.tr1…:post-processor output for transient analysis

*.ac0,*.ac1…: post-processor output for AC analysis

MetaWave:观察波形(post-processor),人机交互界面

五、实验目的

本实验是基于《数字集成电路原理》课程其目的在于:

· 根据实验任务要求,综合运用课程所学知识自主完成反相器链的最优延迟优化设计。

· 学习并掌握国际流行的EDA仿真软件hspice的使用方法,并进行hspice电路网表的

设计与仿真验证。

六、实验内容

1、 熟悉hspice工具环境与网表控制命令。

2、根据设计指标要求,自主完成3-5级反相器链的网表设计。

3、对设计网表进行最优延迟分析与尺寸优化。

4、总结、撰写并提交实验报告。

七、实验仪器设备

(1)工作站或微机终端 一台

(2)局域网

(3)EDA仿真软件hspice 1套

八、实验步骤

1、熟悉hpice仿真软件使用环境,掌握网表控制命令的书写格式。

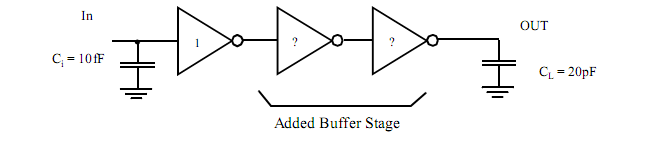

2、根据如下反相器链电路结构图考虑最优路径延迟的设计思路

3、基于TSMC0.25工艺库完成一个标准单位反相器的延迟分析。

4、参考如下三级反相器网表完成3-5级反相器的最优延迟设计与验证

.title this is a inverter chain

.op

.options list node post

.trans 0.1n 100n

vpu in 0 pulse ( 0 2.5 0.5n 0.5n 1n 10n 20n )

vdd 1 0 2.5

mnm1 out1 in 0 0 nch w=300n l=250n

mpm2 out1 in 1 1 pch w=600n l=250n

mnm3 out2 out1 0 0 nch w=300n l=250n

mpm4 out2 out1 1 1 pch w=600n l=250n

mnm5 out out2 0 0 nch w=300n l=250n

mpm6 out out2 1 1 pch w=600n l=250n

cl1 out 0 1p

cl2 in 0 10f

.measure tran tdelay trig v(in) val=1.25 td=0 rise=1

+ targ v(out) val=1.25 td=0 fall=1

.measure tran ttrans when v(out)=1v

.measure tran p_ AVG POWER from=0n to=100ns

.lib 'mix025_1.l' TT

.end

九、实验数据及结果分析:

结果分析:

实验波形及数据分析:

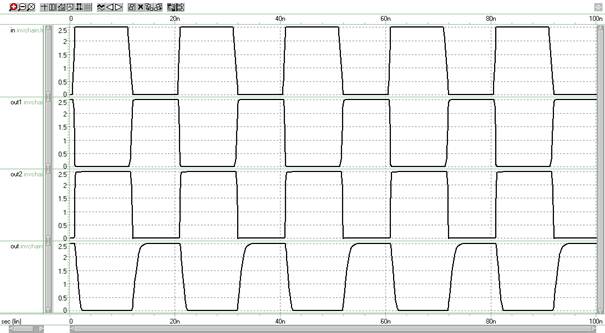

3级反相器波形

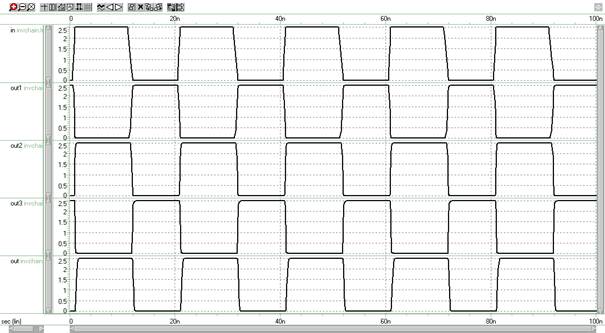

4级反相器波形

5级反相器波形

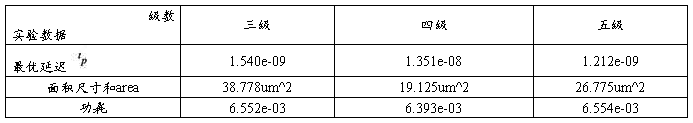

数据分析:

当只有三级反相器时整个电路延时在1.54ns左右,功耗在6.5mW的样子总体面积39um2,这个数据在电路中还算可以接受另外观察其波形,可以发现在功能上也是能够保持的比较好。当级数增加到4级的时候电路延时增加13.5ns而其他的功耗面积都和原来差不多总体性能下降但是在波形上有一定的改善。在反相器增加到5级时,延时为1.2ns功耗面积也差不多,波形变差但还是在接受范围内。

十、实验结论:

通过实验数据及波形我们可以看出一定的增加反相器级数能够在一定程度上降低延迟,然而在某个级数的基础上可能会比原来的延时要差,所以在控制级数以及功耗上下功夫。另外一点就是,有时在宽长比上设置使得延迟非常的小,但是在波形上变的非常差,这也是一个考虑因素,在设置宽长比降低延迟的同时也要考虑到功能(即波形)上的符合要求。当这些考虑周全后也需要在功耗和面积上进行优化,最终得到一个比较好的结果。

十一、总结及心得体会:

通过hspice我们可以非常方便的分析数字电路的各项功能指标以及进行优化设计,也能够进一步了解到电路各个参数之间的相互制约,以及我们在电路设计中应该要进行的折中,单纯的追求一个参数的优化有可能会使整个电路在功能上不能实现,然而这样的话就前功尽弃了。在电路设计中需要多加进行整体分析。

十二、对本实验过程及方法、手段的改进建议:

希望增加利用hspice进行源代码编写实现自己电路的分析

报告评分:

指导教师签字:

评分标准:该实验课程将以一定比例(10%)计入《数字集成电路原理》课程总分,该实验评分标准为:总分10分,具体如下: