集成电路设计综合实验报告

学院:电控学院

班级:微电子1001班

姓名:xxx

学号:xxxxxxxxxx

一、实验目的

1、培养从版图提取电路的能力

2、学习版图设计的方法和技巧

3、复习和巩固基本的数字单元电路设计

4、学习并掌握集成电路设计流程

二、实验内容

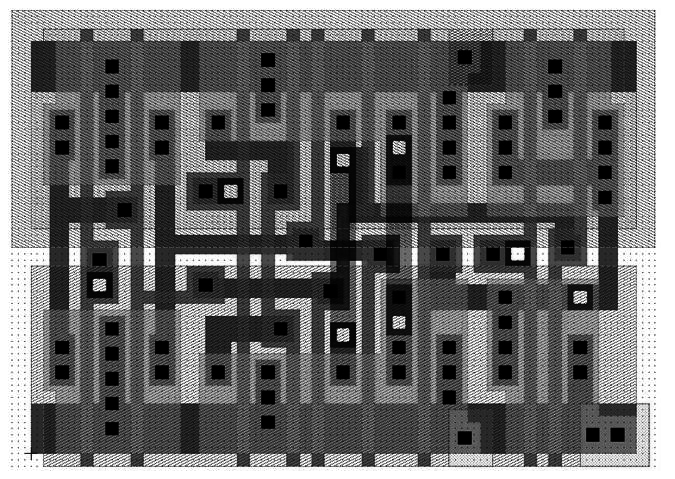

1、反向提取给定电路模块,要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。

)

(1)实验原理

标准CMOS工艺下的集成半导体器件主要有NMOS晶体管、PMOS晶体管、多晶硅电阻和多晶硅电容等。在P型衬底N阱CMOS工艺中,NMOS晶体管直接制作在衬底材料上,PMOS晶体管制作在N阱中。在集成电路版图的照片中,NMOS管阵列和PMOS管阵列一般分别制作在不同区域,PMOS管阵列制作在几个N阱内,NMOS管阵列制作在多个区域。这一点在照片中可以明显地区分开来。N阱和两种有源区存在较为明显的颜色差别。通过对N阱、P型有源区和N型有源区的颜色辨别,可以确认PMOS管阵列和NMOS管阵列位置。

N型选择区和有源区共同构成了N型掺杂区,P型选择区和有源区共同构成了P型掺杂区。在实际的电路连接关系中接触孔的多少取决于晶体管的连接关系,当晶体管一侧或两侧与其它器件存在物理连接时,不需要接触孔。从图中可以看出,形成晶体管的重要结构是多晶硅与有源区的十字交叉区域,只要存在多晶硅栅和某种有源区十字交叉图形,就可以确定一只晶体管的位置,进而通过测量可以确定其宽长比参数。

确定MOS管的类别主要是通过观察该十字交叉区域是否在N阱区域内,N阱区域内为PMOS晶体管,阱外则为NMOS晶体管。

在P型衬底N阱CMOS工艺条件下,NMOS器件直接制作在衬底材料上,PMOS器件制作在N阱中。在模拟集成电路中,MOS晶体管常常工作在线性区或饱和区,需要承受较大的功耗,这些晶体管具有较大的宽长比。模拟集成电路版图常常不规则,这就要求在电路提取时要充分注意电路连接关系。

为了解决较大宽长比器件与版图布局资源之间的矛盾,实际版图照片中常常可以看到,以多只较小宽长比晶体管并联形式等效一只较大宽长比晶体管的情形。这种版图尺寸的转换技术可以实现对芯片总体布局资源的充分合理利用,同时又有利于系统的整体性能提升,有着非常重要的应用。

在确认了NMOS、PMOS晶体管后,根据MOS晶体管源极、漏极的含义,电源电位的高低可以确定出MOS管的源极、漏极和栅极位置。栅极为器件的输入,漏极为器件的输出。NMOS源极接在较低电位,PMOS晶体管源极接在较高电位,这样可以确认各晶体管的源极、漏极和栅极的连接关系。

在模拟集成电路版图中,普通信号连线往往比电源连线要细些,由此可以确定与NMOS源极连接连线为地线或较低电位,与PMOS源极连接连线为正电源或较高电位,这样可以确认正负电源位置。接合上述知识,可以确认版图中的各类器件。可以完成各个器件之间的连接关系确认,画出相应电路的结构图。

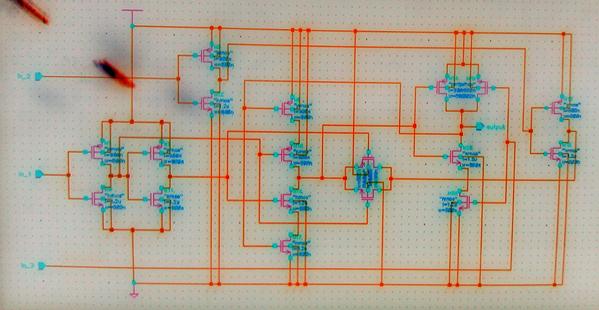

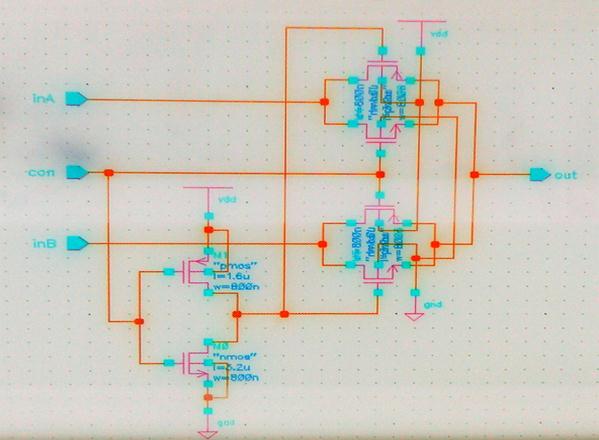

(2)电路原理图提取

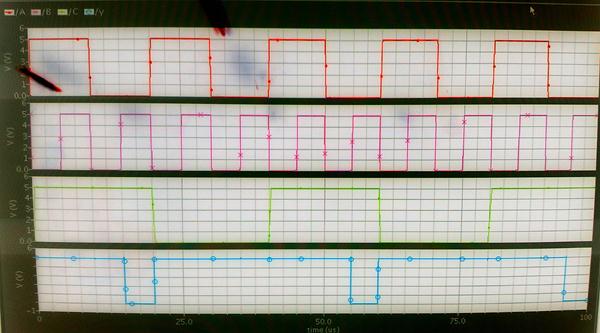

(3)仿真波形

由仿真波形可以看出,当输入为低高高时,输出为低,其余为高。即out=(in_1-)(in_2)(in_3)。

(4)由电路原理图设计版图

该版图经DRC验证之后准确无误。

2、设计一个CMOS结构的二选一选择器。

(1)要求、功能

根据二选一选择器功能,分析其逻辑关系。功能:S为控制信号,A,B为信号当S为高时将A的信号输出,S为低时B信号输出。

(2)电路原理图

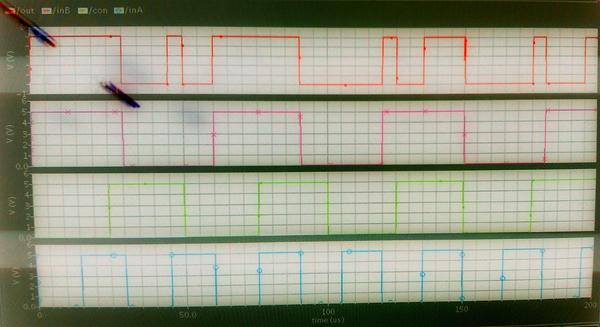

(3)仿真波形图

(3)版图设计

利用几何设计规则文件进行在线DRC验证并修改版图,该版图经DRC验证后准确无误。

三、心得体会

本次课程设计实习由于第一个星期赶在考研之前,所以第一个星期并没有用心去做,而在考研之后才专心做此次课程设计。本次课程设计用的软件就是Cadence,因为之前已接触两次了,所以上手比较快。

课程设计第一个题目是将版图提取出其电路原理图,之前没有做过这样的工作,做起来比较麻烦。做的时候就是对着版图分析,先是从左向右一个一个的提取出单个原件,比如一个MOS管或是一个反向器。再把这些单个单元画在纸上,然后根据版图上的连线把这些单元连起来。之后不断的修改器件的位置以组合成我们常用的单元,比如提取后的原理图中出现的反向器、三态门、传输门以及与非门。在这些都搞定之后便用软件将其画出来,设置每个MOS管的宽长尺寸,检验连线有无错误之后便对其进行波形仿真。通过对波形分析得到其真值表,并写出其逻辑表达式,然后分析功能。最后还是得按照自己提取的原理图将其版图画出,在进行DRC验证,这样第一题的任务便完成了。第二题是设计二选一,这个就比较简单了,只要清楚其工作原理就很容易画出其原理图,然后同样是仿真波形,版图设计,器件比较少设计也就比较容易了。

此次课程设计是三个人一组,所以做起来也就不是那么的无助,大家一起讨论如何提取原理图,如何通过真值表画出原理图,遇到不会操作的也有同伴上网查找,彼此之间互相解决疑问,这样的团队合作比以往的单人做效率高了很多,这也是用了三天就能把两星期的任务完成的重要原因。

通过课程设计,一方面熟悉了Cadence软件的操作,另一方面也在团队合作中解决了遇到的种种问题,加快了自己在这方面设计的速度,提高了效率。

第二篇:集成电路分析与设计实验A-LAB7实验报告文档

集成电路分析与设计实验A—Lab7 Verilog HDL实现7位二进制序列检测电路设计

集成电路分析与设计实验A

集成电路分析与设计实验A—Lab7 Verilog HDL实现7位二进制序列检测电路设计

1.七位二进制序列检测电路的状态转换图

名单序号 学号 需要检测的二位十进制码为 七位二进制码为 ,序列检测电路的状态转换图如下所示:

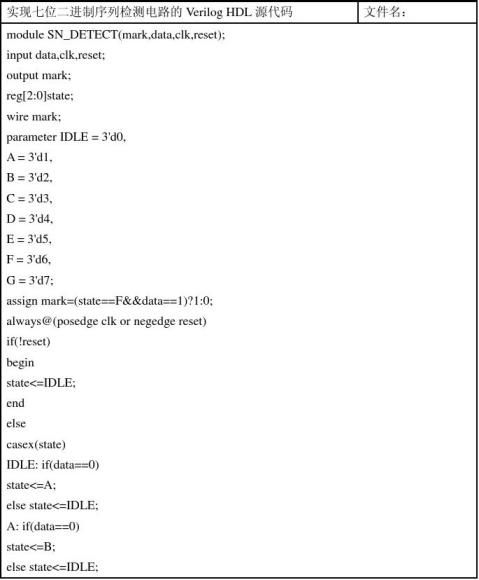

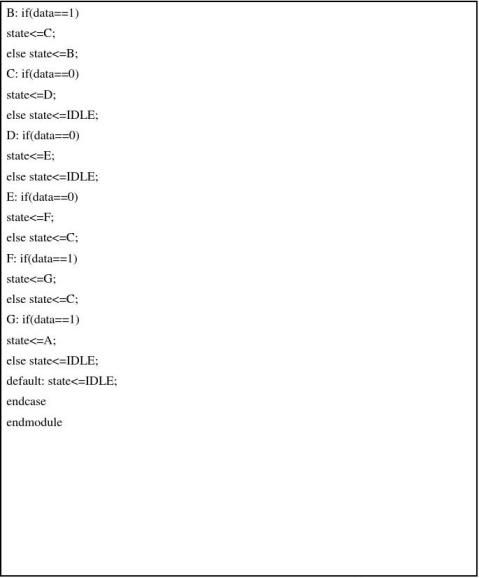

2.实现七位二进制序列检测电路的Verilog HDL源代码

集成电路分析与设计实验A—Lab7 Verilog HDL实现7位二进制序列检测电路设计

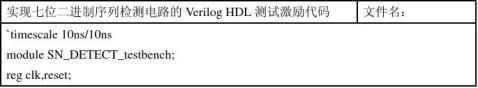

3. 实现七位二进制序列检测电路的Verilog HDL测试激励,要求全面测试电路正常和异常输入情况。

集成电路分析与设计实验A—Lab7 Verilog HDL实现7位二进制序列检测电路设计

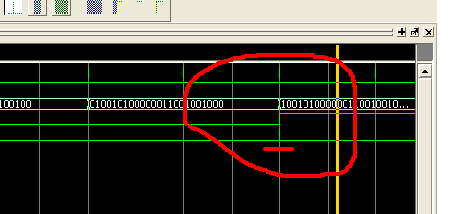

4.仿真结果及波形显示

集成电路分析与设计实验A—Lab7 Verilog HDL实现7位二进制序列检测电路设计