电气与信息工程学院

EDA技术及其应用

实验报告

实验一 0~9999的计数器电路设计

指导老师:谭会生老师

学生姓名:王炜

班级:电子信息1202

学号:12401720207

实验时间:20##-03-31

实验一 0~9999的计数器电路设计

1.实验目的

(1)掌握EDA使用工具QUARTUS2 的使用方法。

(2)学会用quartus软件建立项目并编写程序和调试下载的方法。

(3)掌握VHDL程序的软件及硬件的仿真方法。

2.实验内容

设计并调试好一个计数范围为0~9999的4位十进制计数器电路CNT9999,并用软件QUARTUS II进行仿验证。

3.实验条件

开发软件:Quartus ii 8.0

4.实验设计

1)系统原理框图

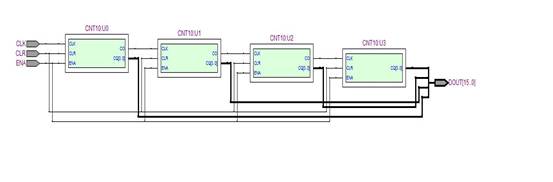

为了简化设计并便于显示,本计数器电路CNT999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图1-1所示的原理图构成顶层电路CNT9999。

图1-1 CNT9999电路原理图

2)VHDL程序

计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下:

CNT10的VHDL源程序:

--CNT10.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT(CLK,CLR,ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END ENTITY CNT10;

ARCHITECTURE ART OF CNT10 IS

SIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR,ENA)IS

BEGIN

IF CLR='1' THEN CQI<="0000";

ELSIF CLK'EVENT AND CLK='1' THEN

IF ENA='1' THEN

IF CQI="1001" THEN

CQI<="0000";

ELSE

CQI<=CQI+'1';

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CLK,CQI)IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CQI="1001" THEN

CO<='1';

ELSE

CO<='0';

END IF;

END IF;

END PROCESS;

CQ<=CQI;

END ARCHITECTURE ART;

CNT9999的VHDL源程序:

--CNT9999.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT9999 IS

PORT(CLK,CLR,ENA:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END ENTITY CNT9999;

ARCHITECTURE ART OF CNT9999 IS

COMPONENT CNT10 IS

PORT(CLK,CLR,ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CO:OUT STD_LOGIC);

END COMPONENT CNT10;

SIGNAL S0,S1,S2,S3:STD_LOGIC;

BEGIN

U0:CNT10 PORT MAP(CLK,CLR,ENA,DOUT(3 DOWNTO 0),S0);

U1:CNT10 PORT MAP(S0,CLR,ENA,DOUT(7 DOWNTO 4),S1);

U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(11 DOWNTO 8),S2);

U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(15 DOWNTO 12),S3);

END ARCHITECTURE ART;

3)仿真波形设置

顶层CNT9999仿真输入设置及可能结果估计图如图1-2。

图1-2 CNT9999仿真输入设置及可能结果估计图

5.实验结果及总结

1)系统仿真情况

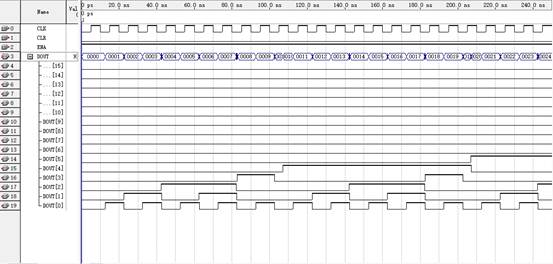

CNT9999的时序仿真结果如图1-3所示。

图1-4 CNT9999的时序仿真结果

从系统仿真结果可以看出,本系统底层和顶层的程序设计完全符合设计要求。同时从系统时序仿真可以看出,从输入到输出有一定的延时,大约为3ns,这正是器件延时特性的反映。

2)逻辑综合结果

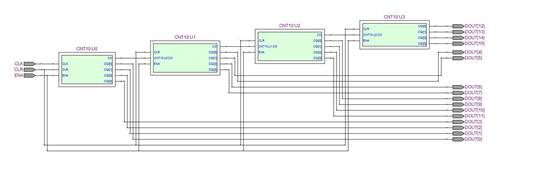

使用Quartus II 8.0进行逻辑综合后,CNT9999的RTL视图如图1-5所示。

图1-5 CNT9999的RTL视图

图1-5 CNT9999的RTL视图

3)实验过程中出现的问题及解决办法

遇到问题:

程序编写好后进行仿真时,发现计数器只能实现从0~9一直循环,而不会依次计数到9999,经查找分析原因是CNT10进位信号提前了。

解决办法:

修改VHDL源程序,将如下代码修改:

修改前:

PROCESS(CLK,CQI)IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CQI<"1001" THEN

CO<='0';

ELSE

CO<='1';

END IF;

END IF;

END PROCESS;

修改后:

PROCESS(CLK,CQI)IS

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF CQI="1001" THEN

CO<='1';

ELSE

CO<='0';

END IF;

END IF;

END PROCESS;

经过相应的程序修改,最后程序通过了,仿真成功,实验完成。

第二篇:EDA 六十进制的计数器实验报告

EDA技术实验项目报告

项目题目: 六十进制的计数器

姓 名:

院 系: 应用技术学院

专 业: 电子信息工程(职教)

学 号:

指导教师:

综合成绩:

完成时间: 2012 年 5 月 22 日

一、项目实验内容摘要

(1)实验目的:

1、掌握带进制的的计数器设计方法。

2、掌握实现带计数、译码、显示功能数字系统架构方法。

3、掌握QUARTUS Ⅱ代码设计输入方法设计的全过程。

(2)实验内容:

(3)实验原理

二、项目实验源代码

三、项目实验工具软件的选用以及实验过程

(1)实验项目硬件要求:

1、EDA2000实验箱(其他厂家具有同等配置试验箱均可),主要使用:输入:时钟源,按键开关,拨码开关,输出:LED灯

2、主芯片:EP1K1OTC100-3(大于此规模的芯片亦可)

3、计算机与QUARTUS 软件

(2)实验项目步骤:

利用Quartus Ⅱ平台进行一般数字系统设计实验主要由以下步骤组成。

1、首先建立工作文件,打开QuartusII,选择菜单File→New。在New窗口中的Device Design Files中选择编译文件的语言类型,选择“VHDL File”,然后在VHDL文本编译窗中输入源程序代码,最后进行文件存盘(选择File→Save As命令)。

2、创建工程。打开建立新工程管理窗。选择菜单File→New Preject Wizard命令,即弹出“工程设置”对话框。

3、 编译前设置,选择芯片ACEX1K EP1K10TC100-3

4、全程编译

5、时序仿真

6、引脚设置和下载

7、配置文件下载

8、实验连线。

9、编程配置器件

四、项目实验结果

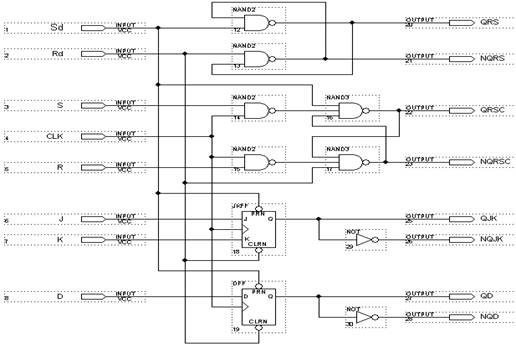

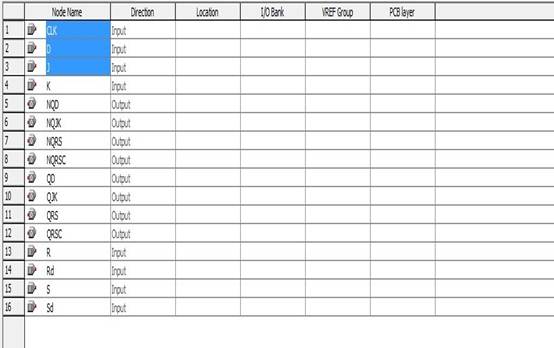

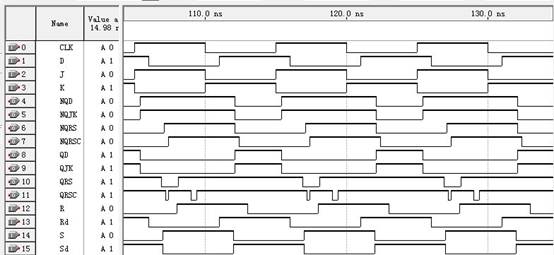

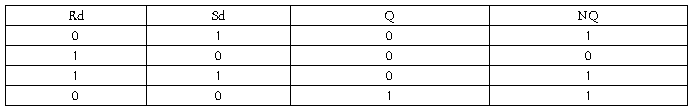

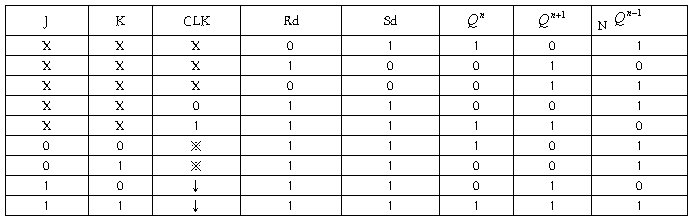

表一 基本RS触发器

表二 D触发器

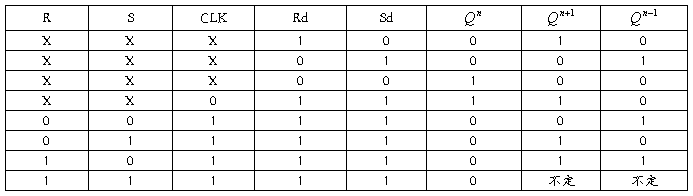

表三 同步RS触发器

表四 J-K触发器

五、项目实验分析

输入信号Sd,Rd对应的管脚接按键开关,CLK接时钟源(频率<0.5Hz):输入信号J,K,D,R,S对应的管脚分别接拨码开关;输出信号QRS,NQRS,QRSC,NQRSC,QJK,NQJK,QD,NQD对应管脚分别接LED灯。另外准备几根连接线,在改变为T“触发”器时,短接相应管脚,或连接“0”“1”电平。拨动拨码开关或者按下按键开关,观察LED灯,与实验内容是否相符。

六、项目实验参考资料

《脉冲与数字电路》 陈立万主编

《EDA实验教程 》 陈强主编

七、小组验收记录及评价