实验4:同步计数器及其应用实验报告

一、 实验目的

1、了解可编程数字系统设计的流程

2、掌握Quartus II 软件的使用方法

3、掌握原理图输入方式设计数字系统的方法和流程

4、掌握74LS161同步16进制计数器的特点及其应用

二、 实验设备

1、计算机:Quartus II 软件

2、Altera DE0 多媒体开发平台

3、集成电路: 74LS10

4、集成电路:74LS161

三、 实验内容

1、 74LS161逻辑功能的测试

2、用74LS161实现12进制计数(异步清零)

3、用74LS161实现12进制计数(同步置数)

四、 实验原理

74LS161

1、 74LS161:异步清零、同步置数四位二进制计数器

2、引脚的定义:

使用74161实现16进制和12进制

1) 首先使用quartus软件建立原理图,首先实现16进制,所以只需要将需要的输入输出接到相应的引脚上,其中需要注意的是我们需要让这个板子开始工作,所以需要将T和P引脚接响应的高电压,然后将cp信号接入相应的输入;q0q1q2q3接到相应的输出就可以了,然后编译。现在在建立波形文件完成仿真,通过仿真结果就可以看到自己的电路是否正确。最后一步就是实现在FPGA上的应用,我们需要做的就是给原来的 原理图分配相应的引脚,然后重新编译后,插入线就可以看到仿真结果了。

2) 12进制可以采取两种方式,也就是同步置数和异步清零两种方式,我使用的异步清零,从而只需要对q0q1q2q3在12的时候执行清零的动作就可以了,也就是加一个而输入的与非门就可以了。

五、 实验结果

第二篇:实验4-加减计数器实验报告

上 海 理 工 大 学

计 算 机 工 程 学 院

实 验 报 告

一实验目的:

1 掌握加减计数器以及特殊功能计数器的设计原理。

2.用VHDL语言设计多功能计数器。

二实验原理:

计数分同步计数器和异步计数器。

1 加减工作原理

加减计数也称可逆计数器,就是根据计数控制信号的不同,在时钟脉冲的作用下,计数器可以进行加1计数操作或者减1计数操作。

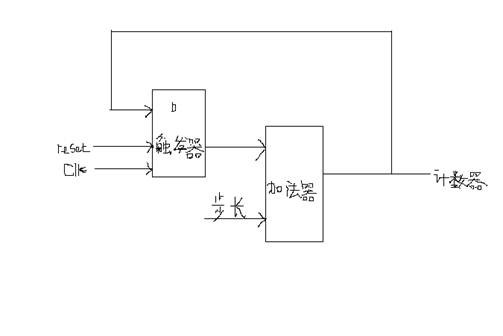

2 变步长工作原理

如步长为3的加法计数器,计数状态变化为0 。3。6 。9。12……,步长值由输入端控制。在加法计数时,当计数值达到或超过99时,在计数器下一个时钟脉冲过后,计数器也。

三实验内容:

1 设计的计数步长可在0~79之间变化

2.通过仿真或观察波形图验证设计的正确性。

3 编译下载验证结果。

四设计提示

1. 注意IF语句的嵌套。

2. 注意加减计数的变化,计数值由9变0(加法)及由0变9(减法)各位的变化。由于计数器为十进制计数器,还应考虑进位或借位后进行加6及减6校正。

五实验步骤:

(1) 代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY count is ――实体

PORT(clk,clr,updn:in STD_LOGIC; ――端口

length:in STD_LOGIC_VECTOR(7 downto 0);

S:out STD_LOGIC_VECTOR(7 downto 0)

);

END count;

ARCHITECTURE countB of count is ――结构体

SIGNAL C_count: STD_LOGIC_VECTOR(7 downto 0); ――信号量

begin

S<= C_count;

PROCESS (clk,clr,length,updn)

VARIABLE temp:STD_LOGIC_VECTOR(8 downto 0); ――变量

BEGIN

if(clr='1') then

C_count<=(others=>'0');

elsif(clk' EVENT and clk='1') then

if(updn='1') then

temp:=C_count+length;

if(temp>"011111111") then

C_count<=( others=>'0');

else

C_count<=C_count+length;

end if;

else

if(temp<length) then

C_count<=(others=>'0');

else

C_count<=C_count-length;

end if;

end if;

end if;

end process;

end countB;

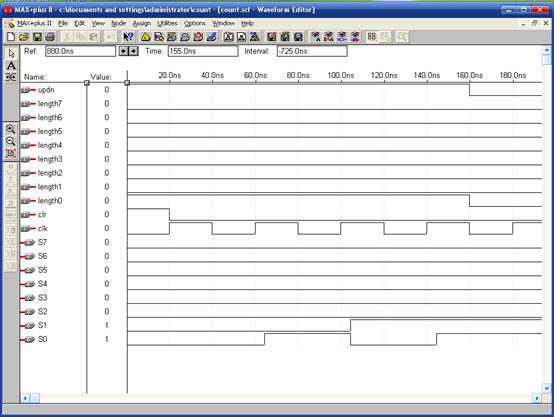

2 仿真截图

上述仿真数据:updn-----判断做加法还是减法

Clk――时钟

Clr――清零

Length(7 downto 0)----步长

S (7 downto 0)――输出

六实验小结:

这次步长可变的加减计数器需要将二进制数转换成BCD码,代码编了可是没有运行成功。实验过程中的硬件下载出错,没有实现下载结果。不过通过这次实验,可以深刻理解计数器的做法。