实验四:计数器的设计

实验四:计数器的设计

实 验 室: 实验台号: 日 期:

专业班级: 姓 名: 学 号:

一、实验目的

1. 通过实验了解二进制加法计数器的工作原理。

2. 掌握任意进制计数器的设计方法。

二、实验内容

(一)用D触发器设计4位异步二进制加法计数器

由D触发器组成计数器。触发器具有0和1两种状态,因此用一个触发器就可以表示1位二进制数。如果把n个触发器串起来,就可以表示N位二进制数。(用两个74LS74设计实现)

(二)利用74LS161设计实现任意进制的计数器

设计要求:学生以实验台号的个位数作为所设计的任意进制计数器。

先熟悉用1位74LS161设计十进制计数器的方法。

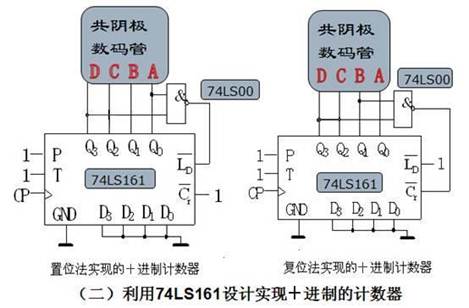

① 利用置位端实现十进制计数器。

② 利用复位端实现十进制计数器。

提示:设计任意计数器可利用芯片74LS161和与非门设计,74LS00为2输入与非门, 74LS30为8输入与非门。

74LS161为4位二进制加法计数器,其引脚图及功能表如下。

三、实验原理图

1.由4个D触发器改成的4位异步二进制加法计数器

2.由74LS161构成的十进制计数器

四、实验结果及数据处理

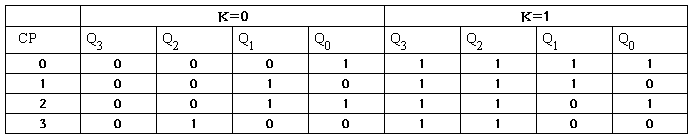

1. 4位异步二进制加法计数器实验数据记录表

2. 画出你所设计的任意进制计数器的线路图,并说明设计思路。

五、思考题

1. 由D触发器和JK触发器组成的计数器的区别?

2. 74LS161是同步还是异步,加法还是减法计数器?

3. 设计十进制计数器时将如何去掉后6个计数状态的?

第二篇:《设计一个四位可逆二进制计数器》的实验报告

实验七 设计一个四位可逆二进制计数器

一、实验目的

掌握中规模集成计数器的使用方法及功能测试方法。

二、实验内容及要求

用D触发器设计一个同步四位二进制可逆计数器。

三、设计过程

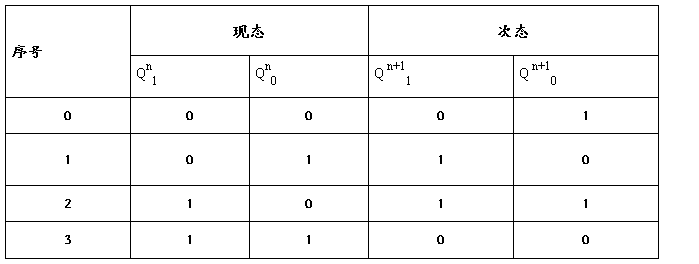

(1)根据题意列出加计数状态表和驱动表,如下表所示。

从绘图工具栏中选择直线工具,然后在要做上划线的文字上按住鼠标左键划到自己想终止的文字上松开鼠标左键就可以了!

(2)求得各位触器的驱动信号的表达式

D1=

(3)根据题意列出减计数状态表和驱动表,如下表所示。

(2)求得各位触器的驱动信号的表达式

由上分析可知:加减计数只在于时钟CP的不同,若要使一个电路能够可逆计数,增设一控制开关,就可实现。设K=1时为加计数,设K=0时为减计数,

加法:CPn= 减法:CPn=

减法:CPn=

则有:CPn=

(或如 K=0时为加法: CPn=

K=1时为 减法: CPn= =

= 则有:CPn=

则有:CPn= )

)

四、可逆计数器逻辑图如下:

四、实验用仪器、仪表

数字电路实验箱、万用表、74LS74、74ls86

六、实验数据