实验报告

20##至 20##学年度第1学期

课程名称: 数字电子课程设计

系 别: 电气工程系

班 级: 电气工程及其自动化二班

学 号: 1109141117

姓 名: 吕辉

指导教师: 王开全

第二篇:四位二进制加法计数器设计报告

四位二进制加法计数器设计报告

一、计数器简介

计数器是最常用的时序电路之一,可用来计数、分频、定时、产生节拍脉冲以及其他时序信号。计数器分类有很多,按触发器动作可分为同步计数器和异步计数器;按计数数值增减可分为加计数器、减计数器和可逆计数器;按编码可分为二进制计数器、BCD码计数器、循环码计数器。本次设计的是四位异步二进制加法计数器。

二、设计构思

四位异步二进制计数器逻辑图如上,它由4个T触发器组成。计数脉冲CP加至时钟脉冲输入端,每输入一个计数脉冲,U1将翻转一次。U2、U3和U4都以前级触发器的/Q端输出作为触发信号,当Q0端由1变成0时,即/Q0由0变成1时,U1翻转,其余类推。/R端是用来清零端,只能全部置0,/S端是用来置1端,只能全部置1。

三、实现构思并用Workveiw仿真

1、T触发器的实现

本次设计是通过D触发器来构成T触发器,即将D触发器的/Q端与D端相连即可 ,下面是D触发器的设计与仿真以及元件模块的制作:

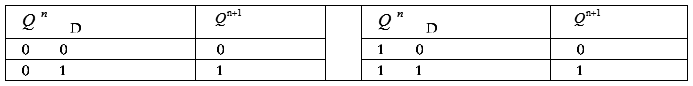

a、D触发器的逻辑图如下图,引脚/SD可以直接置1,而引脚/RD可以直接置0,时钟触发端为CP,有正反两个输出端Q与/Q,这种触发器在工作中具有维持、阻塞特性,所以称之为维持阻塞触发器。 b、下面进行D触发器电路仿真,根据仿真波形可知该D触发器满足特性表

b、下面进行D触发器电路仿真,根据仿真波形可知该D触发器满足特性表

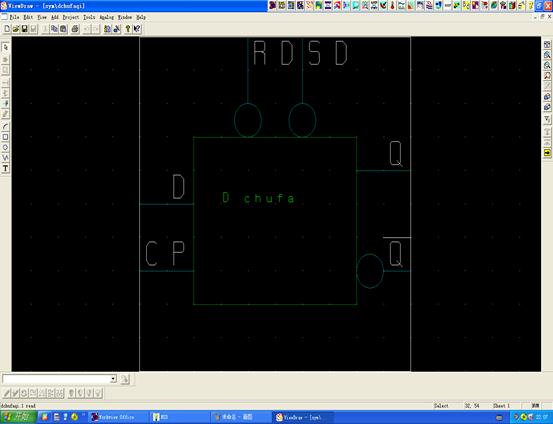

仿真截图如下: c、D触发器元件制作截图

c、D触发器元件制作截图

2、四位二进制异步加法计数器的实现

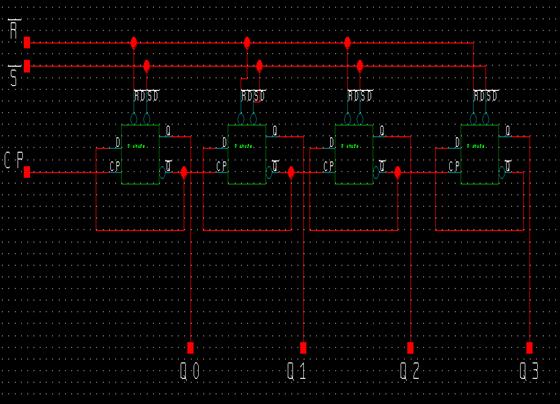

首先是将每个D触发器的/Q端与D端相连,构成T触发器,然后按照先前的构思连接电路,加法计数器的计数脉冲输入端为CP,全部清0端为/R,全部置1端为/S,输出端由低位到高为分别为Q0、Q1、Q2、Q3。

其电路截图如下:

下面进行计数器的逻辑仿真,CP输入单位时间脉冲,/R在第一个时钟脉冲置0,其余以后的时钟周期都置1,/S在所有的时钟周期内都置1,然后,进行逻辑仿真。分析仿真波形可知计数器由0000初始状态一直计数到1111,由此可见设计的四位二进制异步加法计数器能够实现预期的功能。其仿真结果截图如下: