实验六 同步计数器的设计

学号: 姓名:

一、实验目的和要求

1.熟悉JK触发器的逻辑功能。

2.掌握用JK触发器设计同步计数器。

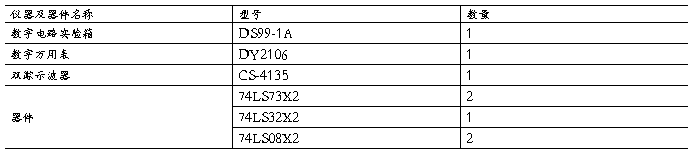

二、实验仪器及器件

三、实验预习

1、复习时序逻辑电路设计方法。

⑴ 逻辑抽象,得出电路的状态转换图或状态转换表

① 分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。通常都是取原因(或条件)作为输入逻辑变量,取结果作输出逻辑变量。

② 定义输入、输出逻辑状态和每个电路状态的含意,并将电路状态顺序编号。

③ 按照题意列出电路的状态转换表或画出电路的状态转换图。

通过以上步骤将给定的逻辑问题抽象成时序逻辑函数。

⑵ 状态化简

① 等价状态:在相同的输入下有相同的输出,并且转换到同一次态的两个状态。

② 合并等价状态,使电路的状态数最少。

⑶ 状态分配

① 确定触发器的数目n。因为n个触发器共有 种状态组合,所以为获得时序电路所需的M个状态,必须取

种状态组合,所以为获得时序电路所需的M个状态,必须取

<

<

② 给每个电路状态规定对应的触发器状态组合。

⑷ 选定触发器类型,求出电路的状态方程、驱动方程和输出方程

① 根据器件的供应情况与系统中触发器种类尽量少的原则谨慎选择使用的触发器类型。

② 根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,即可写出电路的状态方程、驱动方程和输出方程。

⑸ 根据得到的方程式画出逻辑图

⑹ 检查设计的电路能否自启动

① 电路开始工作时通过预置数将电路设置成有效状态的一种。

…… …… 余下全文

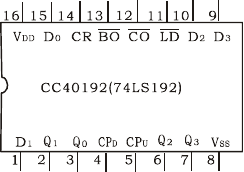

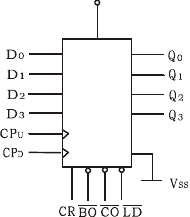

—置数端 CPU—加计数端 CPD —减计数端

—置数端 CPU—加计数端 CPD —减计数端 —非同步进位输出端

—非同步进位输出端  —非同步借位输出端

—非同步借位输出端

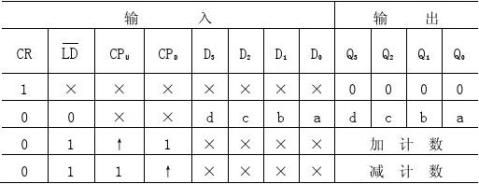

也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

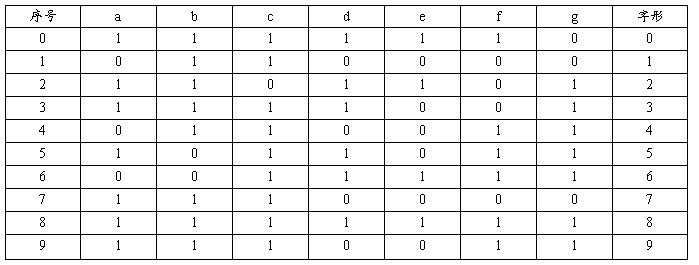

也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。 为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421码十进制加、减计数器的状态转换表。

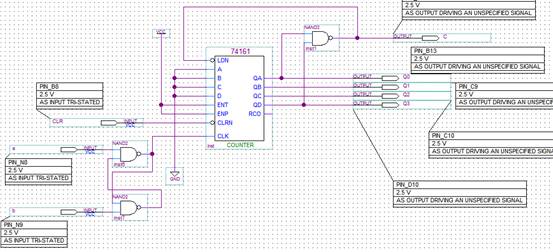

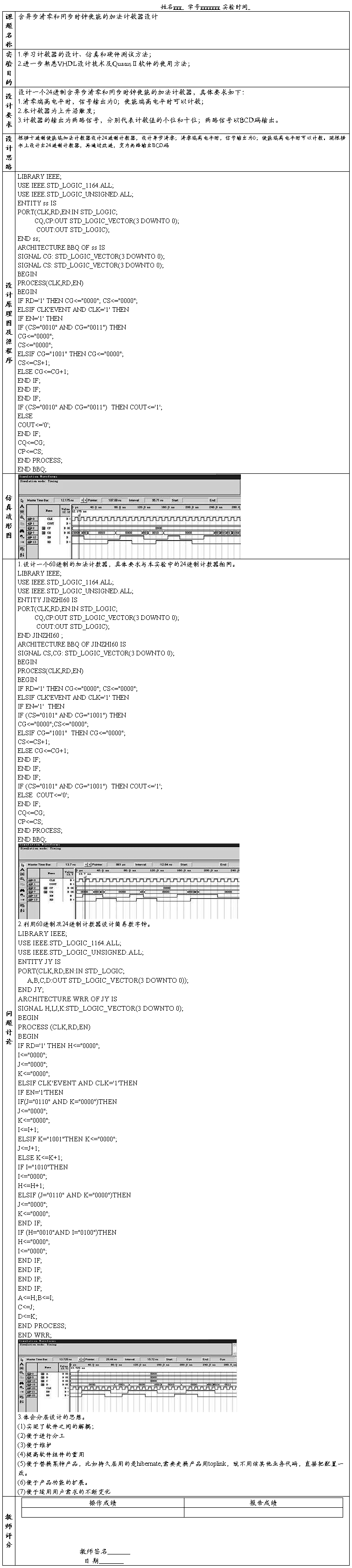

为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行 8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421码十进制加、减计数器的状态转换表。 实验四:计数器的设计

实验四:计数器的设计

![文本框: [广东水利电力职业技术学院]](https://upload2.fanwen118.com/wk001/2616734/2616734_img_002.png)