实验八 设计任意进制计数器

一、实验目的

掌握中规模集成计数器的使用方法及功能测试方法。

二、实验内容及要求

采用(74LS192)复位法或预置数法设计一个三位十进制计数器。要求各位同学设计的计数器的计数容量是自己学号的最后三位数字。

三、设计过程

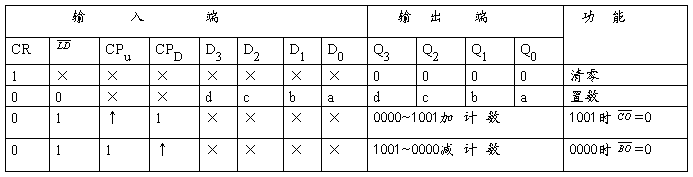

74LS192是中规模同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列如图所示。74LS192(CC40192)的功能如下表所示。

表74LS192(CC40192)的功能

用M进制集成计数器可以构成N(任意)进制的计数器。通常用反馈清零法和反馈置数法。当计数器的计数N>M时,则要用多片M进制计数器构成。其计数规律为:当低位计数器没有达到计数的最大值时,如74LS192的1001时,其高位芯片应处于保持状态,只有当低位芯片计数达到最大值时,给相邻的高位芯片计数器发一个信号,使其脱离保持状态,进入计数状态。现以233为例为计数容量进行设计。由于233为三位数,因此需用三块74LS192。

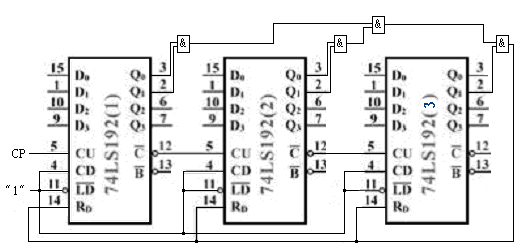

1、清零法:

CR(RD)=(Q1Q0)百(Q1Q0 )拾(Q1)个

初态:0000

终态:233-1=232即:0010 0011 0010

状态转换图:(略)

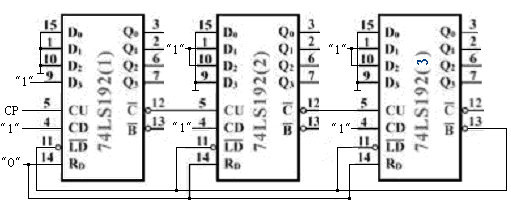

2、置数法:由于74LS192是具有异步清零、置数功能的十进制计数器,因此保留哪233种状态,方法有多种。下图是其中两种置数法。犹以最后一种使用器件最少,接线最为简单。

方案一:

方案三:

=(Q1Q0)百(Q1Q0 )拾(Q2Q0)个 (或

=(Q1Q0)百(Q1Q0 )拾(Q2Q0)个 (或 =

= )

)

初态:0000 (或1000-332=668)

终态:332-1=331即:0011 0011 0001 (或999)

四、实验用仪器、仪表

数字电路实验箱、万用表、74LS192、74LS00、74LS20、74LS08等

五、实验步骤

① 清零法:

1. 检查导线及器件好坏(即加上电源后,按74LS192的功能表进行检测)。

2. 按上图连接电路。 、CPD分别接逻辑开关并置为高电平,百位(74LS192(3))、拾位、个位的Q3、Q2、Q1、Q0分别接发光二极管或数码管,计数脉冲接手动或1Hz时钟脉冲。检查无误后接通电源。

、CPD分别接逻辑开关并置为高电平,百位(74LS192(3))、拾位、个位的Q3、Q2、Q1、Q0分别接发光二极管或数码管,计数脉冲接手动或1Hz时钟脉冲。检查无误后接通电源。

3. 加入CP进行测试并检查结果是否正确,如有故障设法排除。

4. 结果无误后记录数据后拆线并整理实验设备。

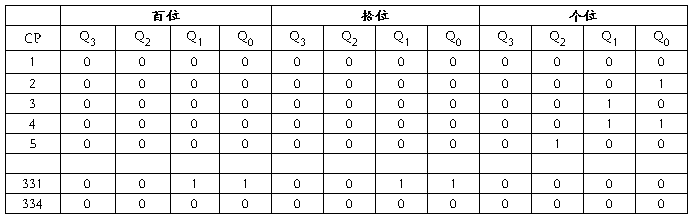

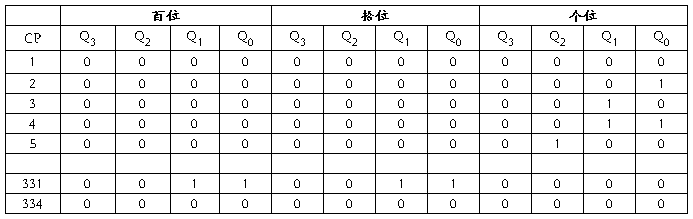

实验数据如下:

实验证明,实验数据与设计值完全一致。设计正确。

② 置数法:

1. 检查导线及器件好坏(即加上电源后,按74LS192的功能表进行检测)。

2. 按上图连接电路。CR、CPD分别接逻辑开关并置为高电平,百位(74LS192(3))、拾位、个位的Q3、Q2、Q1、Q0分别接发光二极管或数码管,计数脉冲接手动或1Hz时钟脉冲。检查无误后接通电源。

3. 加入CP测试并检查结果是否正确,如有故障设法排除。

4. 结果无误后记录数据后拆线并整理实验设备。

实验数据如下:

实验证明,实验数据与设计值完全一致。设计正确。

六、设计和实验过程的收获与体会。

1、设计过程的收获与体会:

①设计前要确定是用清零法还是置数法。

②要将状态表列出。特别是置数法,要保留哪几种状态方法有多种。

③可用Electronics Workbench进行仿真。以验证设计正确与否。

2、实验过程的收获与体会:

① CC40192的CR、 、CPD端不能悬空;

、CPD端不能悬空;

② 出现故障时,首先检查电源,然后检查CP,CR、 、CPD端的电平状态。如不相符,则可能存在断路现象。如相同,可能存在设计错误,或者可能器件已损坏。

、CPD端的电平状态。如不相符,则可能存在断路现象。如相同,可能存在设计错误,或者可能器件已损坏。

③实验逻辑电路图最好把集成块的引脚标上,以便接线和检查。

第二篇:实验报告2

内蒙古工业大学信息工程学院

实 验 报 告

课程名称: CPLD/FPGA应用开发技术

实验名称: 组合逻辑电路的设计

实验类型: 验证性□综合性□ 设计性■

实验室名称: 信息工程学院9楼机房

班级: 电子09-2班 学号:

姓名: 组别:

同组人: 成绩:

实验日期: 2012年5月2 日

实验报告成绩: 指导教师审核(签名): 年 月 日

一、实验目的

1、了解时序电路的 VHDL 语言设计方法。

2、了解同步计数器的使用方法。

3、理解时序电路和同步计数器加译码电路的联系,设计任意编码计数器。

二、实验设备

1、PC 机

2、EDA 实验箱(主芯片是ALTERA EPM7128SLC84-15)。

三、实验内容

1、用 VHDL 语言输入法设计一个同步四位二进制加法计数器和六进制同步计数器。

2、用 74LS161 两个宏连接成八位二进制同步计数器。

3、用 74LS161 宏,同时采用清零和置数法组成六进制和十二进制计数器。

四、实验步骤

1、采用文本编辑器输入 VHDL 语言源程序,或采用原理图输入法从MF 库中调用器件

74161,生成原理图,之后建立工程。

2、编译。

3、仿真。

4、对芯片进行编程。

5、根据管脚分配情况连线。

(1) 根据芯片特点,管脚分配时一般将时钟信号分配给83 脚,复位信号分配给

1 脚。若有使能信号,使能信号分配给84 脚。

(2) 时钟信号的连接:将实验板上提供的时钟与芯片的83 脚相连。

(3) 复位信号的连接:将实验板上的某按键开关输出与芯片的1 脚相连。

(4) 将计数器的输出端分别与LED 灯相连。

6、按动复位键,观察实验结果。

7、改变输入时钟信号的频率,观察实验结果。

五、实验程序

1、用 VHDL 语言输入法设计一个同步四位二进制加法计数器和六进制同步计数器。

(1)四位二进制加法计数器程序代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CN2 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

OUT1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CN2;

ARCHITECTURE SS OF CN2 IS

SIGNAL CNT: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR)

BEGIN

IF CLR='0' THEN OUT1<="0000";

ELSIF (CLK'EVENT AND CLK='1') THEN

IF CNT="1111" THEN CNT<="0000";

ELSE CNT<=CNT+'1';

END IF;

OUT1<=CNT;

END IF;

END PROCESS;

END SS;

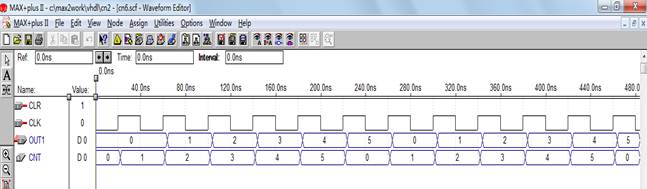

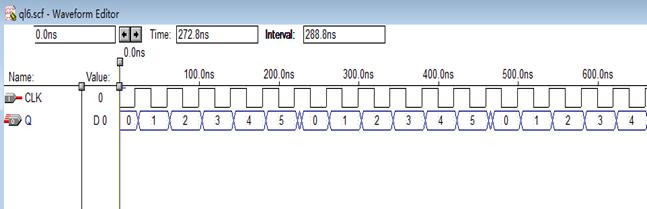

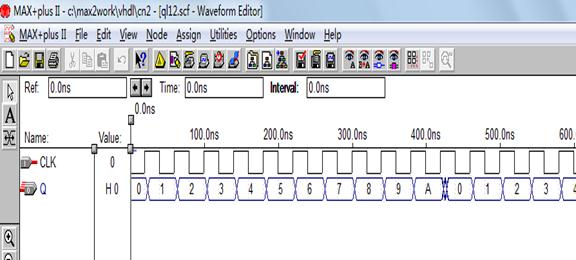

仿真波形

(2)六进制同步计数器程序代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CN6 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

OUT1:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END CN6;

ARCHITECTURE SS OF CN6 IS

SIGNAL CNT: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR)

BEGIN

IF CLR='0' THEN OUT1<="000";

ELSIF (CLK'EVENT AND CLK='1') THEN

IF CNT="101" THEN CNT<="000";

ELSE CNT<=CNT+'1';

END IF;

OUT1<=CNT;

END IF;

END PROCESS;

END SS;

仿真波形

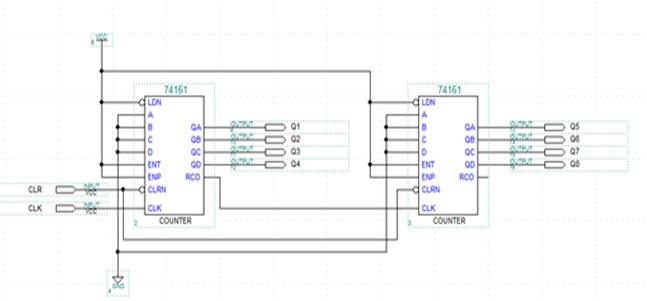

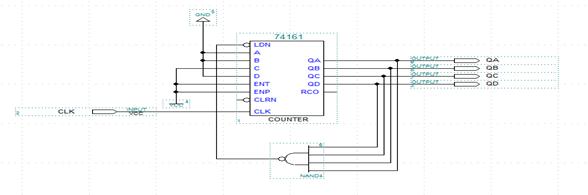

2、用 74LS161两个宏连接成八位二进制同步计数器。

原理图:

结果分析:由仿真结果可知,计数器输出Q4,Q3,Q2,Q1,O4,O3,O2,O1组成的八位二进制数每计数六个清零一次,所以构成六进制同步计数器,符合设计要求。

输入数据:CLR为清零端,开始为零(有效),然后为1(无效)。CLK为时钟输入端,是周期为50s的方波,以观察输出知否正确。

管脚分配: CLK对应管脚83。CLR对应管脚84。Q4,Q3,Q2,Q1,O4,O3,O2,

仿真波形

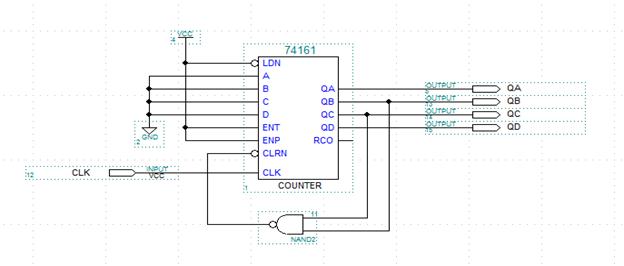

3、 用 74LS161宏,同时采用清零和置数法组成六进制和十二进制计数器。

六进制

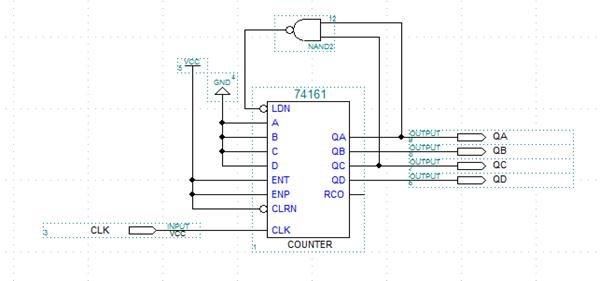

清零法原理图

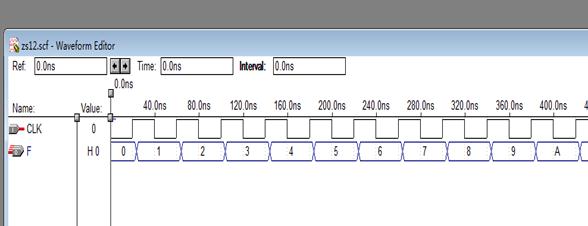

结果分析:由仿真结果可知,计数器输出O1,O2,O3,O4组成的四位二进制数每计数六个置数一次,所以构成一个六进制同步计数器,计数范围为0010——1001,符合设计要求。

输入数据:CLR为清零端,开始为零(有效),然后为1(无效)。CLK为时钟输

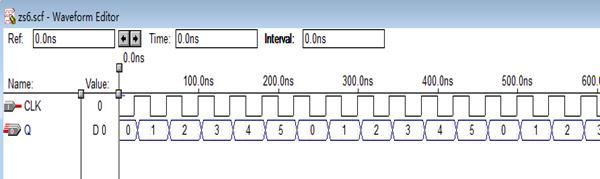

仿真波形

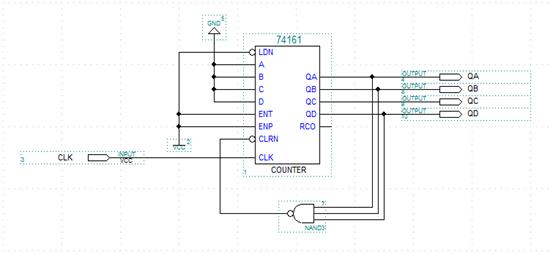

置数法原理图

仿真波形

仿真波形

十二进制

清零法原理图

清零法原理图

仿真波形

置数法原理图

仿真波形

六、实验心得体会

经过试验,很好地将理论与实践结合起来,不仅学会了VHDL语言,它很好的描述了数字电路系统设计,而且熟悉了MAX+plus2的基本用法,在使用软件调试的过程中能够快速有效的找出错误,提高了实验的效率,从仿真的结果也能够很直观的看出结果,这为我们以后自己编程序查找错误提供了很好的帮助。但是也有很多细节容易忽视,对软件运用不是很熟悉,以后多加练习进行加强。