数字钟课程设计

一、 课程设计目的:

利用所学的模拟电子技术,数字电子技术等知识设计数字钟电路,并完成电路的组装与焊接。在课程设计过程中要了解各种芯片的引脚功能。

二、设计任务:

设计一个数字钟,具有以下功能:

? 时间以24小时为一个周期;

? 显示时、分、秒;

? 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间

三、 设计要求:

(1)、在数字钟焊接过程中不能出现虚焊、短焊和漏焊的情况。

(2)、能画出数字钟课程设计电路图

(3)、数字钟焊制完成后能用万用表对其查错

四、数字钟课程设计器材:

1、CD4511

2、74LS90

3、74HC08

4、74HC32

5、CD4013

6、74HC04

7、CD4060

8、L7805

9、IN4007、100uf电容、103瓷片电容

10、晶振

11、开关、电阻、导线若干

12、发光二极管

13、七段数码管

14、14、16、24引脚插座

15、插孔电路板

16、电烙铁、钳子等一套工具

五、数字钟电路原理框图:

六、数字钟系统构成:

1、电源电路:

7805是一个很常用的稳压芯片,使用方便。用一个简单的电路即可输入一个很稳定的电压,输出电压为5V。接入电路时①脚接高电位,②脚接地,③脚输出

2、秒信号产生电路:

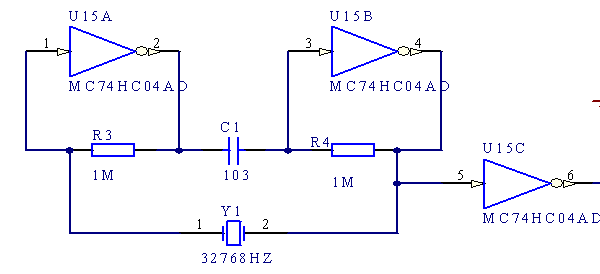

(1)、脉冲信号产生电路:——石英晶振电路

此电路中要用到74HC04芯片,是一个六反相向器。内含6个相同的反相器,1A输入高电平,1Y输出低电平。

(2)、分频电路:

此分频电路中要用到CD4060和CD4013两个芯片。

CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,RESET为高电平时,计数器清零且振荡器无效。RESET为低电平时,在Ф1(或Ф0)的下降沿计数器以二进制进行计数

CD4060引脚结构图图

用4060进行14分频,产生2HZ的信号,再用D触发器构成2分频电路,产生1HZ的信号

CD4013是一双D触发器,由两个相同的、相互独立的D触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出

CD4013引脚结构图

3、秒显示电路:

此部分电路中要用到七段数码管、CD4511芯片和74LS90芯片

(1)、74LS90是一个异步二、五、十进制计数器。有异步置0、9和计数功能。计数脉冲由CP。端输入,从Q。端输出,则构成1位二进制计数器。计数脉冲由CP1 端输入,从Q3 Q2 Q1端输出,则构成异步五进制计数器;将CP1与Q0相连,计数脉冲由CP0端输入,从Q3、Q2、Q1、Q0端输出,则构成异步十进制计数器

(2)、显示器件——七段数码管:

图中即为七段式LED数码管,是由七个条状发光二极管封装在一起构成的,利用七个发光段的不同组合显示0~9等阿拉伯数字。数码管上分别由a b c…….f七段组成,DP为小数点段,各笔划段引线管脚采取双列,在数码正置俯视时,左下脚为第一脚,按顺时针依次确定其余各引脚,图(b)为G5011内部电路,它是一种共阴极显示数码管,测试时,共阴极接电源负极,电源正极通过限流电阻器分别于各笔段引脚相连,每个笔段发光二极管电流限制在5~10mA之间,如果数码管共阴端通过一个电阻器接地,点亮笔段增多,数码管的亮度减小。

(3)、显示译码器——CD4511

CD4511引脚结构图

CD4511是一个用于驱动共阴极 LED (数码管)显示译码器。

BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入 DCBA 状态如何,七段均发亮,显示“8”。它主要用来检测数码管是否损坏。

LE:锁定控制端,当LE=0时,允许译码输出。 LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

A1、A2、A3、A4、为8421BCD码输入端。

a、b、c、d、e、f、g:为译码输出端,输出为高电平有效。

4、分显示电路:

注:分显示电路和秒显示电路相同,故电路原理图和相应解释可参照上面秒显示电路图。

5、时显示电路

此部分电路中包含七段数码管、CD4511芯片、74LS90芯片

电路原理中CD4511和74LS90芯片运用原理和秒、分显示电路中的相同,但在接线是不相同的,特别是在计数电路那一部分中,时计数是计数到23就要清零。而秒、分显示电路中计数部分是计数到59后清零并进位。

下图即为时计数电路连线原理图

数字钟系统构成总结:

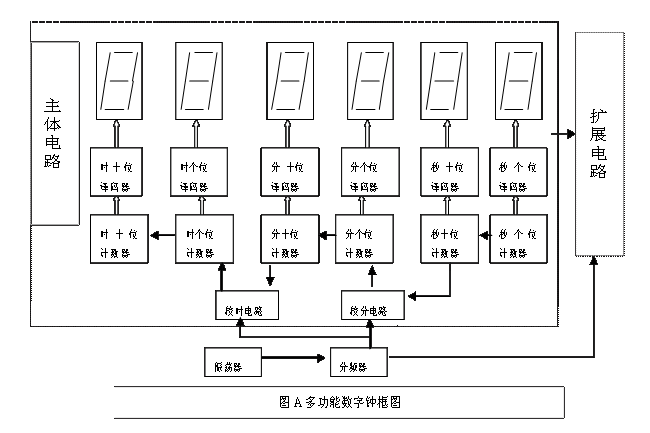

1、数字钟的构成:振荡器、分频器、计数器、译码器、显示器等几部分。

2、 数字钟的时、分、秒实际上就是由一个24进制计数器(00-23),两个60进制计数器(00-59)级联构成。设计数字钟实际上就是计数器的级联。

3、60进制计数器的设计。

4、24进制计数器的设计。

5、计数器的级联设计。

七、调试查错:

在电子钟焊制完成后接通电源,调试过程中出现了下列问题:

(1)发光二极管不亮。

(2)发光二极管亮了,但七段数码管上没有显示。

(3)在时、分、秒 正常显示后,接通电源第一遍的时候时、分、秒都计数不准确,到第二个轮回才计数正常。

(4)数字钟焊制完成后不美观。

出现上述问题的原因:

(1)在焊接的过程中出现了漏焊的现象,导致电源线路没有接通,使得发光二极管不亮,这说明在焊接过程中不仔细。

(2)七段数码管不显示是因为领取元器件时七段数码管领的是共阳级的,所以导致七段数码管不能显示

(3)、在焊制数字钟之前没有很合理的排版,考虑不全。

八、课程设计心得体会

从本次课程设计过程中让我学到了很多东西,在此次的数字钟设计过程中,更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法.。像CD4511、74LS90、CD4013、74HC32、CD4060、74HC08、74HC04等这些芯片的原理及使用方法。更重要的是在这次的课程设计过程中让我学会了怎样用万用表去查错,我想这对我以后从事电子方面的事时有很大的帮助。虽然在焊制的过程中,出现了几个小问题,像漏焊等这种情况,可以说算得上是一次性成功的。

九、课程设计成果展示:

十、数字钟课程设计总电路原理图:

第二篇:数字钟课程设计

目录

【摘要】 ……………………………………………………

1、数字钟的组成及基本原理

1.1振荡器 ……………………………………………………………..

1.2分频器 …………………………………………………………..

1.3计数器 ……………………………………………………………..

1.4译码显示 ………………………………………………

1.5校时、校分 ……………………………………….

1.6扩展电路………………………………………….

2、具体电路以及参数计算 ………………………………………

2.1振荡电路 ……………………………………………….

2.2分频器电路 ………………………………………………………..

2.3计数器电路 ……………………………………………………………

2.3.1计数器六十进制的接法 …………………………………

2.3.2二十四进制计数器的接法 …………………………………….

2.4译码显示电路 …………………………………………

2.5校时、校分电路 …………………………………………………………..

2.6整点报时电路……………………………………………….

3、组装并调试 ……………………………………………………..

3.1各部分分块调试 ………………………………………………

3.2调试中出现的问题及解决方案 ……………………………………………..

4、设计心得与体会 ……………………………………………………………………

5、附录 ……………………………………………………………………..

6、参考文献 ……………………………………………………………..

多功能数字钟设计与制作

学生:

指导老师:

【摘要】:

多功能数字钟是采用数字电路实现用数字显示时间的计时装置。主要由振荡器、分频器、计时器、译码显示及扩展电路几部分构成。具有时间显示、校时校分及闹钟设置、整点报时等扩展功能并且具有走时准确、显示直观、稳定等优点深受人们喜爱。

关键字:振荡器、分频器、计时器、译码显示、报时

【Abstrac】:

Multifunction Digital Clock is a timing device which use digital circuit to show the time by numbers. It mainly consists of oscillator, frequency divider ,timer display ,decoding show and expansion circuipoint .It has the function of time display、hour and minute changes and other extensions such as alarm clock settings and the whole point timekeeping.with its advantage of time walking accurately、direct and stable display ,it is deeply loved by the consumers.

【Keyword】:Occillator Divider Timer Decoding display Timekepping

1.数字钟的组成及基本原理

如图A所示,数字钟电路系统由主体电路和扩展电路两大部分组成。其中主体电路完成数字钟的基本功能,即:能准确计时,以数字形式显示小时、分秒的时间;小时计时以“24进1”,分和秒的计时以“60进1”;具有校正时和分的功能。扩展电路完成数字钟的扩展功能。

1、系统的工作原理:

振荡器产生稳定的高频脉冲信号,作为数字中的时间基准,然后经分频器输出标准秒脉冲。秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。计数器的输出分别经译码器送显示器显示,计时出现误差时可以进行校时、校分。各扩展电路必须在主体电路正常运行的情况下才能进行功能扩展。

2、各单元电路的基本原理:

1.1振荡器电路

振荡器是数字钟的核心。振荡器的稳定度及频率的精确度决定了数字钟的准确程度。一般来说,振荡器的频率越高,计时精度越高,但耗电量增大且分频级数多。一般有如下几种方案构成振荡器电路:

方案1.、如图1-1所示为电子手表集成电路(如5c702)中的晶体振荡器电路,常取晶振的频率为32768Hz,因其内部有15级2分频集成电路,所以输出端正好可得到1Hz的标准脉冲。该方案优点是走时准确及稳定,集成度高,所需芯片少。

方案2、由集成电路定时器555与RC组成的多谐振器,电路图如图1-2。输出频率为1000Hz。该方案的优点是起振容易,振荡周期调节范围广,缺点是频率稳定性差,精度低,所以在本实验中不宜使用。

方案3、由集成逻辑门与RC组成的对称式多谐振荡器,可以输出频率为1MHz的脉冲。该方案的优点是精度高,集成简单,所需元器件少。

由于此次设计所提供的芯片主要是74ls00且方案三精度较高,连线简单所以选用方案三。(图参见P139黄封面书)

1.2分频器电路

分频器的功能主要有两个:一是产生标准秒脉冲信号,二是提供功能扩展电路所需要的信号。选用中规模集成芯片74ls90可以完成上述功能,用6个级联即可以得到1Hz的脉冲,该方案原理简单,易于调试,且可以得到各种频率的脉冲,适合功能的扩展。因此此次设计选用该方案。

1.3计数器电路

分和秒都是模M=60的计数器,它们的个位都是十进制计数器,而十位则是六进制计数器。时计数器是一个“24翻1”的特殊进制计数器,即当数字钟的计时器运行到23时59分59秒时,秒的个位计数器再输入一个秒脉冲时,数字钟应自动显示为00时00分00秒,实现日常生活中习惯用的计时规律。修改由于都不多于十进制,则可以用6个中规模集成电路计数器74ls90来实现计数。该方案功能灵活,芯片统一便于调试与组装。

1.4译码显示电路

译码显示电路的作用是将时分秒计数器输出的4位2进制代码翻译并显示出相应的十进制的状态。通常译码器与显示器是配套使用的,如果选择共阴极发光二极管数码显示器BS201/202,则译码驱动器应选配74ls48或CD4511。修改本设计中使用的就是BS201与CD4511配套使用。

1.5校时校分电路

当数字钟接通电源或者计时出现误差时,均需要校正时间。对校时电路的要求是,在进行小时校正时不影响分和秒的计时,同理,在进行分校正时不影响时和秒的正常计数。其实现方法可以是将校时校分信号直接加到分、时计数器上,因此校时校分电路实际上是一个输入信号的转换开关。以下是几种方案:

方案1:简单的手动开关,如图1-4-1所示,正常工作时,s指向A,校时时只需使s指向B。这种电路简单,但是开关的通断产生随机的机械抖动信号,不易控制其稳定性。

方案2:如图1-4-2所示,用三个与非和一个可调电位实现信号的转换,当正常工作时,电位器动滑头指向B,这时CP=C0;当需要校时,动滑头指向A,此时CP等于秒脉冲,两个电容可以滤去滑动中产生的干扰信号。

方案3:三个与非门和基本RS触发器。基本RS触发器可以完全消除开关的机械抖动,是最佳的一种校时校分电路。

1.6扩展电路

随着技术的发展,这种具有基本功能的数字钟并不能满足人们的要求,所以通常要根据不同人的需要进行功能的扩展,下面按照人们常用到的数字钟功能提供了几种扩展电路方案。

方案1:仿广播电台整点报时电路。要求是:每当数字钟计时到整点(或快到整点时)发出音响,通常按照4低音1高音的顺序发出间断声响,一最后一声高音结束的时刻为整点时刻。

方案2:定时控制电路。定时控制电路可以使数字钟在规定的时刻发出信号,或驱动音响电路进行“闹时”;或控制某装置电源的接通或断开实现定时控制。具体电路图见图1-6-1

方案3:报整点时数电路。功能是:每当数字钟计时到整点时发出声响,且几点响几声。实现这一功能的电路要经过三个阶段的工作:分进位脉冲到来时小时计数器加1;报时计数器应记录此时的小时数;报时计数器开始做减法计数,每减一个脉冲,音频电路鸣叫一声,直到计数器的值为零。具体电路如图1-6-2。此方案较为复杂。

由于材料有限,本次设计选用接法较为简单但功能实用的方案1

2、具体电路及参数计算

2.1振荡器

选用由集成逻辑门与RC组成的时钟脉冲源振荡器,可以输出频率为1MHz的脉冲。具体方案电路如下图2-1

原理及参数计算:

2.2分频器

本设计采用6片74ls90级联成 分频电路得到1Hz频率脉冲,且可以得到用于扩展电路所需要的各种频率。具体接线图如下图2-2

分频电路得到1Hz频率脉冲,且可以得到用于扩展电路所需要的各种频率。具体接线图如下图2-2

2.3、时分秒计数器

选用6片74ls90来实现计数功能,其中分个位、秒个位及时个位是十进制,分十位和秒十位是六进制,时十位只能显示0、1、2三个数字。如图2-3-1。分计时和秒计时中当Q1、Q2全为1时,R01、R02均为高,计时器清零实现60进制。如图2-3-2,时计数中当十位Q1和个位Q2均为1时,十位个位上R01、R02全为高,计时器清零实现24进制。

2.4译码显示电路

本设计使用BS201和CD4511配套使用实现译码显示功能。左图为一个一码显示的配套电路,本次设计中需使用6套来显示我们所需要观察到的数字。

2.5校时校分电路

本次设计采用方案3,用三个与非门和基本RS触发器来实现校分/时功能。其中基本RS触发器可以完全消除开关的机械抖动。具体电路如图2-5

2.6整点报时电路

仿电台整点报时要求在快到整点时按4低音1高音的顺序发出间断声响,一最后一声高音结束的时刻为整点时刻。设4声低音(采用50HZ分别发生在59分51秒、53秒、55秒、57秒、59秒,它们的持续时间为1S。由此可见,分十位和个位的计数器的状态分别为秒十位计数器的状态为 ,

, ,秒十位计数器的状态为

,秒十位计数器的状态为 。秒个位计数器

。秒个位计数器 的状态可用来控制500HZ和50HZ的音频。表2-6-1列出了秒各位计数器的状态,由表可得只有当

的状态可用来控制500HZ和50HZ的音频。表2-6-1列出了秒各位计数器的状态,由表可得只有当 ,

,

,

, 及

及 时,音响电路才能工作。音响电路中采用射级输出端,推动8欧德蜂鸣器,三极管基极串接1K欧限流电阻,是为了防止电流过大损坏蜂鸣器,三极管选用高频功率管即可,本设计使用8085NPN型三极管,具有方向特性可以节约一个非门。整点报时的电路图如图2-6-2

时,音响电路才能工作。音响电路中采用射级输出端,推动8欧德蜂鸣器,三极管基极串接1K欧限流电阻,是为了防止电流过大损坏蜂鸣器,三极管选用高频功率管即可,本设计使用8085NPN型三极管,具有方向特性可以节约一个非门。整点报时的电路图如图2-6-2

表2-6-1