计算机组成原理实验报告

学院:

专业:

班级:

学号:

姓名:

评分:

20##年**月**日

实验一

1. 实验名称:验证74LS181运算和逻辑功能

2. 实验目的:

(1) 掌握算术逻辑单元(ALU)的工作原理;

(2) 熟悉简单运算的数据传送通路;

(3) 画出逻辑电路图及布出美观整齐的接线图;

(4) 验证4位运算功能发生器(74LS181)组合功能。

3. 实验原理:

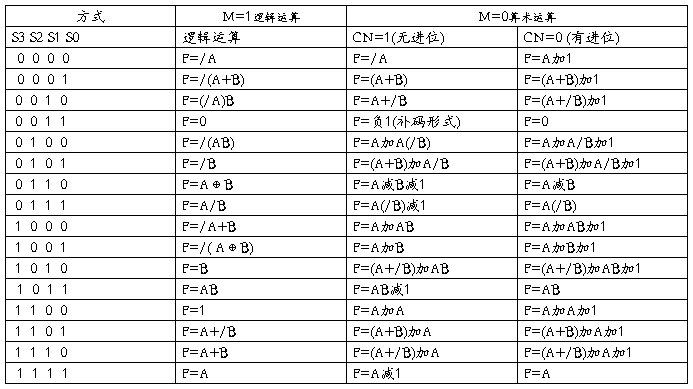

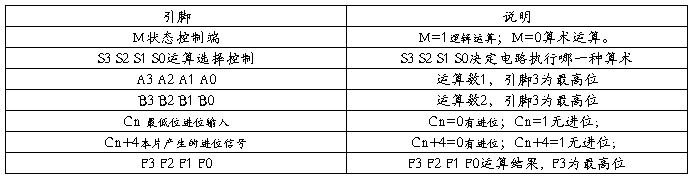

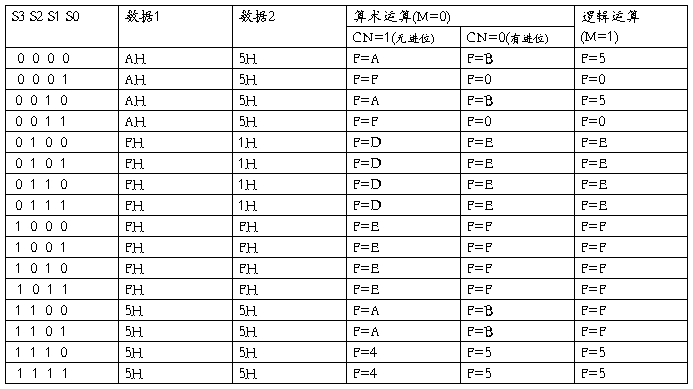

ALU能进行多种算术运算和逻辑运算。4位ALU-74LS181能进行16种算术运算和逻辑运算。功能表如下:

(上表中的“/”表示求反)

ALU-74LS181引脚说明:M=1 逻辑运算,M=0 算术运算

4. 实验内容:

电路图如下(放大可查看详细结构):

验证74LS181型4位ALU的逻辑算术功能,填写下表:

5. 总结及心得体会:

在该实验中,首先入手熟悉Multisim的常用操作。比如,怎么添加元件,连线等,总的来说,操作起来还是比较简单的。

然后开始试着绘制实验一的电路图,一个简单的图,花费了很长时间,才搞清楚原理。找元件,连线,都很费劲,尤其是找元件,有些元件有很多相似的元件,但功能不一样,一时疏忽,弄错了,直接导致连接后无法使用。

在试验中,常常遇到的问题就是明明导线已经连接好了,但是电路就是无法导通,后来把图放大后仔细检查时,发现原来是在连接导线时有些地方的导线和其他的导线交叉了,这样的对于新手来说很常见,而且一般很难发现。

通过实验,基本了解了ALU的工作原理,算术逻辑运算器单元ALU(74LS181)能跟据S3 S2 S1 S 0 M端口控制来对输入的数据完成各种不同的运算。外接存储器实现了数据的缓冲与存储的功能。

所以,经过几天的实践,收获挺大的,熟悉了简单运算器的数据传送通路,掌握了算术逻辑单元的工作原理。使我对知识有了更深的了解,积累了实践操作的宝贵经验。同时,了解到,计算机硬件方面也很有趣,因此硬件知识也很重要,以后慢慢学习提高。

实验二

1. 实验名称:运算器(2)

2. 实验目的:

(1).熟练掌握算术逻辑单元(ALU)的应用方法;

(2).进一步熟悉简单运算器的数据传送原理;

(3).画出逻辑电路图及布出美观的接线图;

(4).熟练掌握有关数字元件的功能和使用方法;

(5).熟练掌握子电路的创建及使用。

3. 实验原理:

本实验仿真单总线结构的运算器,原理如图2-2所示。

图2-2 单总线结构的运算器示意图

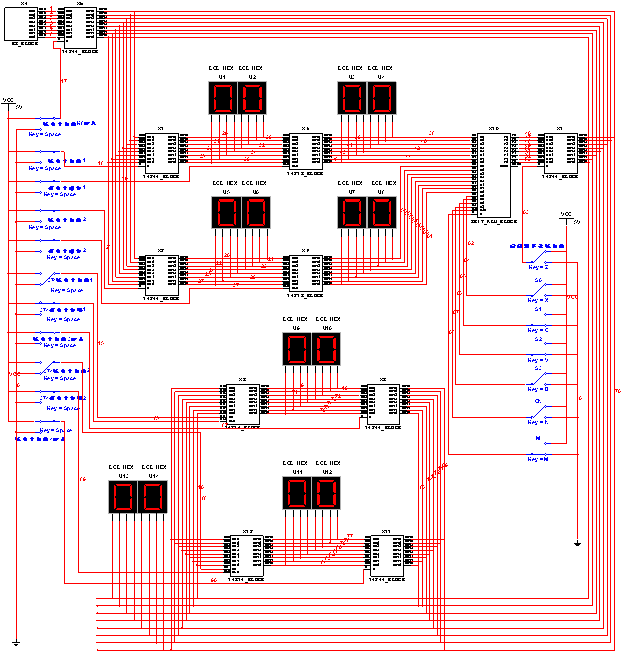

电路图中,上右下三方的8条线模拟8位数据总线;K8产生所需数据;74244层次块作为暂存工作寄存器DR1和DR2;两个74374层次块作为通用寄存器组(鉴于电路排列情况,只画出两个通用寄存器GR1和GR2,如果可能的话可设计4个或8个通用寄存器);众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;核心为8位ALU层次块。

4. 实验内容:

在Multisim画出电路图并仿真,完成如下操作。

(1) 说明整个电路工作原理。

(2) 说明74LS244N的功能及其在电路中的作用,及输入信号G有何作用。

(3) 说明74LS273N的功能及其在电路中的作用,及输入信号CLK有何作用。

(4) 说明74LS374N的功能及其在电路中的作用,及输入信号CLK和OC有何作用。

(5) K8产生任意数据存入通用寄存器GR1。

(6) K8产生任意数据存入通用寄存器GR2。

(7) 完成GR1+ GR2→GR1。

(8) 完成GR1- GR2→GR1。

(9) 完成GR1∧GR2→GR1。

(10) 完成GR1∨GR2→GR1。

(11) 完成GR1?GR2→GR1。

(12) ~GR1→GR2。(“~”表示逻辑非运算)。

(13) ~GR2→GR1。

运算器实验电路图如下(放大可查看详细结构):

(1).说明整个电路工作原理。

答: K8产生所需数据,打开74LS244层次块三态门电路,将产生数据输入总线,将数据存入74LS374层次块作为的通用寄存器组GR1和GR2;通过其他 74LS244的开关,将通用寄存器里的数据放到74LS273层次块作为的暂存工作寄存器DR1和DR2中;将DR1和DR2中的数据通过核心8位ALU层次块运算,将结果又保存到GR1或者GR2中。众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;

(2).说明74LS244N的功能及其在电路中的作用,及输入信号G有何作用;

答:74LS244层次块为三态门电路,在电路中将部件与总线连接或断开,起开关作用,当G为低电平时,部件连接,G为高电平时,部件断开。

(3).说明74LS273N的功能及其在电路中的作用,及输入信号CLK有何作用;

答:74LS273作为临时工作寄存器,在电路中临时寄存数据,CLK上跳沿触发工作。

(4).说明74LS374N的功能及其在电路中的作用,及输入信号CLK和OC有何作用;

答:74LS374层次块作为通用寄存器组,在电路中寄存数据,另具有三态门的作用。CLK上跳沿触发工作,OC为低电平时,部件连接,OC为高电平时,部件断开。

(5).K8产生任意数据存入通用寄存器GR1。

答:a. K8确定任意数(测试时可指定一个2位16进制数);b. Q=0(低电平),数据送总线;c. U↑(正跳变)且Y=0.该数存入GR1

(6).K8产生任意数据存入通用寄存器GR2。

答:a. K8确定任意数(测试时可指定一个2位16进制数);b. Q=0(低电平),数据送总线;c.P↑且O=0。该数送GR2。

(7).完成GR1+ GR2→GR1。

答:a.Q=1(屏蔽掉K8)、I=0、W=0、E↑,GR1→DR1;b.Space=0、R=0、T↑,GR2→DR2;c.加法:S3~S0=1001B(对应BVCX四键)、CIN=1(对应N键)、M=0(对应M键),此时结果在ALU的输出端,令Z=0,结果送总线,U↑结果存入GR1.

(8).完成GR1- GR2→GR1。

答:前2步同上;S3~S0=0110B(对应XCVB四键)、Cin=1(对应N键)、M=0(对应M键),Z=0,P↑。

(9).完成GR1∧GR2→GR1。

答:前2步同上;S3~S0=1011B(对应XCVB四键)M=1(对应M键),Z=0,U↑。

(10).完成GR1∨GR2→GR1。

答:前2步同前;S3~S0=1110B(对应XCVB四键)、M=1(对应M键),Z=0,P↑。

(11).完成GR1?GR2→GR1。

答:a.I=0、W=0、E↑,GR1→DR1;b.S3~S0=0000B(对应XCVB四键)、M=1(对应M键),Z=0,P↑。

(12).~GR1→GR2。(“~”表示逻辑非运算)

答:a.I=0、W=0、E↑,GR1→DR1;b.S3~S0=0000B(对应XCVB四键)、M=1(对应M键),Z=0,U↑。

(13).~GR2→GR1。

答:a.Space=0、R=0、T↑,GR2→DR2;b.S3~S0=0101B(对应XCVB四键)、M=1(对应M键),Z=0,U↑。

5. 总结及心得体会:

通过本实验,我懂得了该运算器的原理。懂得了如何将数据存入通用寄存器。如何又将通用寄存器中的数据通过总线传入暂存寄存器。又如何将其输入运算器进行运算。

运算器工作原理:K8产生所需数据,打开74LS244层次块三态门电路,将产生数据输入总线,将数据存入74LS374层次块作为的通用寄存器组GR1和GR2;通过其他 74LS244的开关,将通用寄存器里的数据放到74LS273层次块作为的暂存工作寄存器DR1和DR2中;将DR1和DR2中的数据通过核心8位ALU层次块运算,将结果又保存到GR1或者GR2中。众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;

在这个实验中,明确指出,总线上只能有一个输入端口。而控制总线输入数量的三态门中,有K8层次块旁的一个,有8位运算器旁的一个,有通用寄存器旁的两个。总共四个。在进行总线操作时,只允许其中一个三态门置于导通状态。这样就保证了总线的要求。否则将出现一些问题,比如总线输出的不是K8中设置的值。这可能是这些数据参加了某种运算后的结果。

该实验同样遇到很多问题,一开始不知道怎么去自定义层次块,还有自定义层次块时没有在里面把元件连接好,有些小细节没注意,如:有些元件里面是要放置电源的,往往这些疏忽了,导致自定义的层次块无法使用。

还有在测试时也遇到了些问题,比如怎么去进行运算,运算的数据无法显示等。同时,在验证运算时,对于逻辑运算概念模糊,不理解逻辑运算时怎么进行的,以致在运算时总以为是电路运算结果错误,其实是自己计算错误,后来,在网上查找了很多资料,比如“A+B”、“AB”的运算等等,最后还是通过不断努力实现了所有功能,并测试通过。

第二篇:计算机组成原理课程设计的实验报告

长治学院

课程设计报告

课程名称:计算机组成原理课程设计

设计题目: 设计一台性能简单的计算机

系 别: 计算机系

专 业: 计科1101班

组 别: 第三组

学生姓名: 学 号:

起止日期:2013年7月4日~ 20##年7月10日

指导教师: 张剑妹

目 录

一、课程设计的目的 ----------------------------------1

二、设计要求 ----------------------------------------1

三、设计的方法及过程---------------------------------2

3.1整机设计 --------------------------------------2

3.1.1 根据设计要求正确设置正确设置多路开关-------2

3.1.2操作控制信号及其实现方式-------------------2

3.1.3根据接线表画出整机的线路图-----------------2

3.2.设计指令系统----------------------------------3

3.3.设计微指令及指令的微程序----------------------4

3.3.1设计微地址 --------------------------------4

3.3.2写出指令的执行流程-------------------------3

3.3.3编写指令的微程序---------------------------5

3.4.编写并执行应用程序----------------------------8

四、心得体会-----------------------------------------7

一 课程设计的目的

通过课程设计更清楚地理解下列基本概念:

(1)计算机的硬件基本组成;

(2)计算机中机器指令的设计;

(3)计算机中机器指令的执行过程;

(4)微程序控制器的工作原理;

(5)微指令的格式设计原理;

二 设计要求

题一研制以台性能如下的实验计算机。

(1)没有外部设备;

(2)运算器采用单累加器多寄存器结构;

(3)操作数寻址方式有:立即数寻址、寄存器寻址、直接寻址;

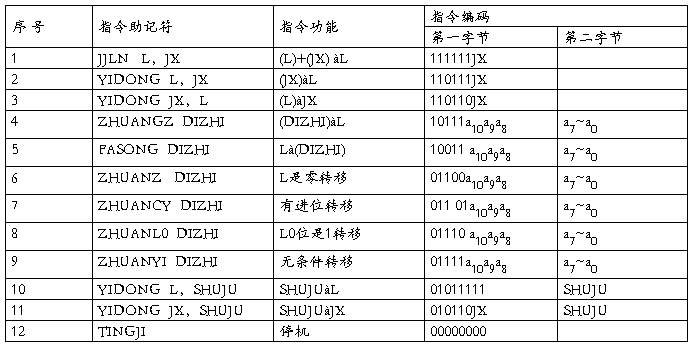

(4)设计由如下指令组成的指令系统,其中L为累加器A,Jx为通用寄存器。将指令的二进制编码填入表中;

(5)计算各指令的微地址并写出各指令的微程序;

(6)将下列程序手工汇编、手工装入并运行,察看运行结果。

ORG 100

START: YiDONG L,#3 (5F03H)

YIDONG J1,#05 (5905H)

JIA L,J1

FASONG 00D

TINGJI·

(7)编写汇编语言程序实现如下功能:将内存某两个单元的数据相加后存入另一个单元中,若有进位,则在00B单元中存入数据0,否则在00B单元中存入数据1;

(8)将该应用程序机器汇编、机器装入、并连续运行,察看运行结果并验证程序的正确性;

三 设计的方法及过程

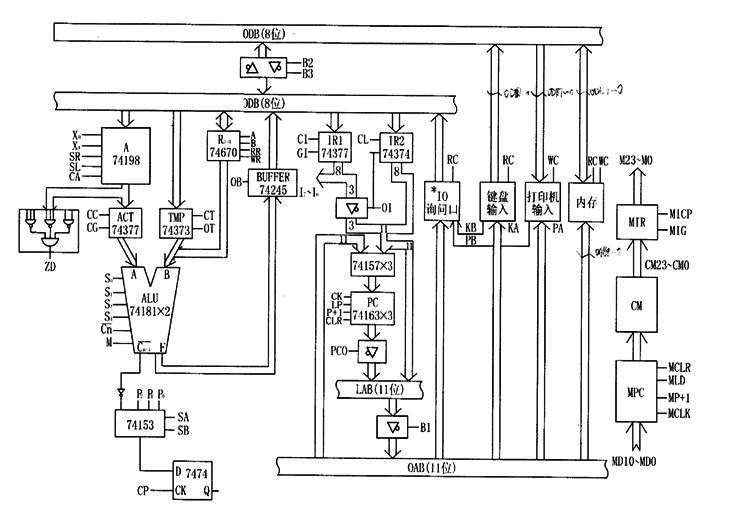

3.1 整机设计

3.1.1 根据设计要求正确设置正确设置多路开关

(1) 设计单累加器多寄存器结构的运算器, 要求开关KA、KB、KC、KR分别置左、右、右、下。

(2) 为了便于微指令的设计, 标出在运算器中数据的传输方向。

3.1.2操作控制信号及其实现方式

微操作控制信号设计的一般原则

1) 对于电平有效的操作控制信号, 可采用微指令码直接控制。

2) 对脉冲型和电平跳变信号, 需外加门电路实现。

3) 对需多个控制信号的器件,通常将某些信号固定好, 其他信号接某个Mi。

设计实验接线表

按模块逐个归纳整理, 明确各模块中各器件各控制信号的处理方法, 将其分别接在某个Mi上.

1) 运算器模块

累加器A: X0----M16 X1----M17 CA----φ

累加暂存器ACT: CC----φ CG----M5

暂存器TMP: CT-----+5V OT----M10

算逻单元: S3-S0----M23-M20 Cn----M19 M----M18

输出缓冲器BUF: OB----M8

进位产生线路: P2-P0不用 SB、SA----X1X0 CP----M13+φ

2) 寄存器堆模块

RR----M1 WR----M0·φ A、B将有指令部件控制

3) 指令部件模块

指令寄存器IR1: GI----M7 CI----φ

指令寄存器IR2: CL---- M14·φ

IR1、IR2输出控制: OI----M15

程序计数器PC: P+1----M6 CLR----+5V CK----φ

LP由LP’通过M9间接控制

PC输出控制: PCO由P+1通过M6间接控制

4) 内存模块: RC----M2(RC’)+φ WC----M3(WC’)+φ

5) 总线缓冲模块: B1、B3----RF B2----RC’

6)微程序控制模块

微程序计数器MPC: MCLR----RO MCLK----PO

MLD----M4 MP+1----+5V

操作码散转控制: MD10-MD6----GND

MD5-MD2----I7-I5,I2 MD1-M0----+5V

微指令寄存器: MIG----GND MICP----启停模块产生

7) 启停和时序模块: DR----M5 RCP----φ

3.1.3根据接线表画出整机的线路图如下:

图1. 整机逻辑框图

3.2 设计指令系统

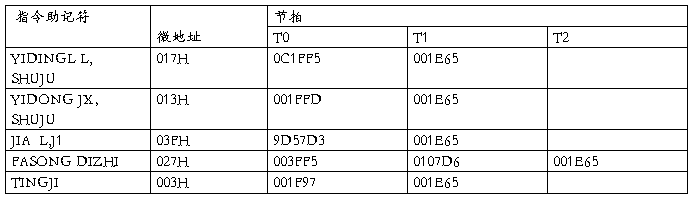

表一 指令系统

3.3 设计微指令及指令的微程序

3.3.1计算微地址

微程序入口地址形成方法:

MD10 MD9 MD8 MD7 MD6 MD5 MD4 MD3 MD2 MD1 MD0

0 0 0 0 0 I7 I6 I5 I2 1 1

取指微指令放在000H处。

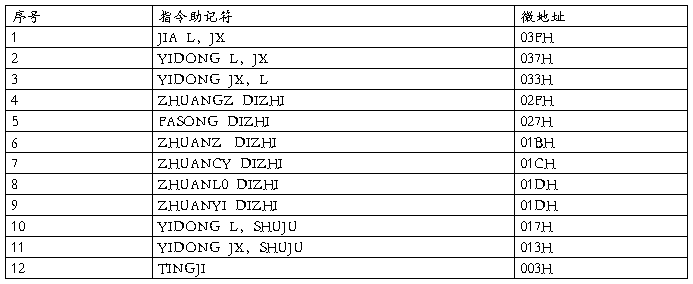

表二 微地址

3.3.2写出指令的执行流程

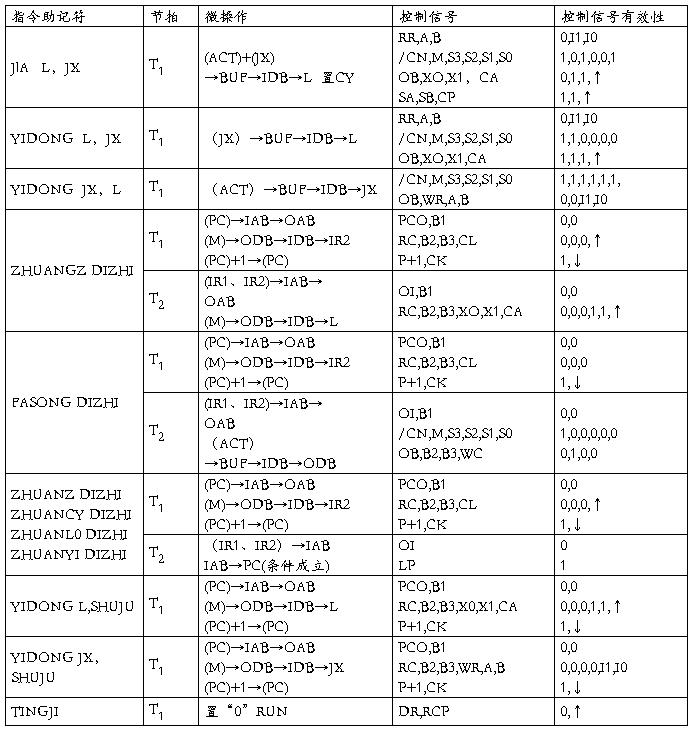

表三 指令的执行流程

3.3.3编写指令的微程序

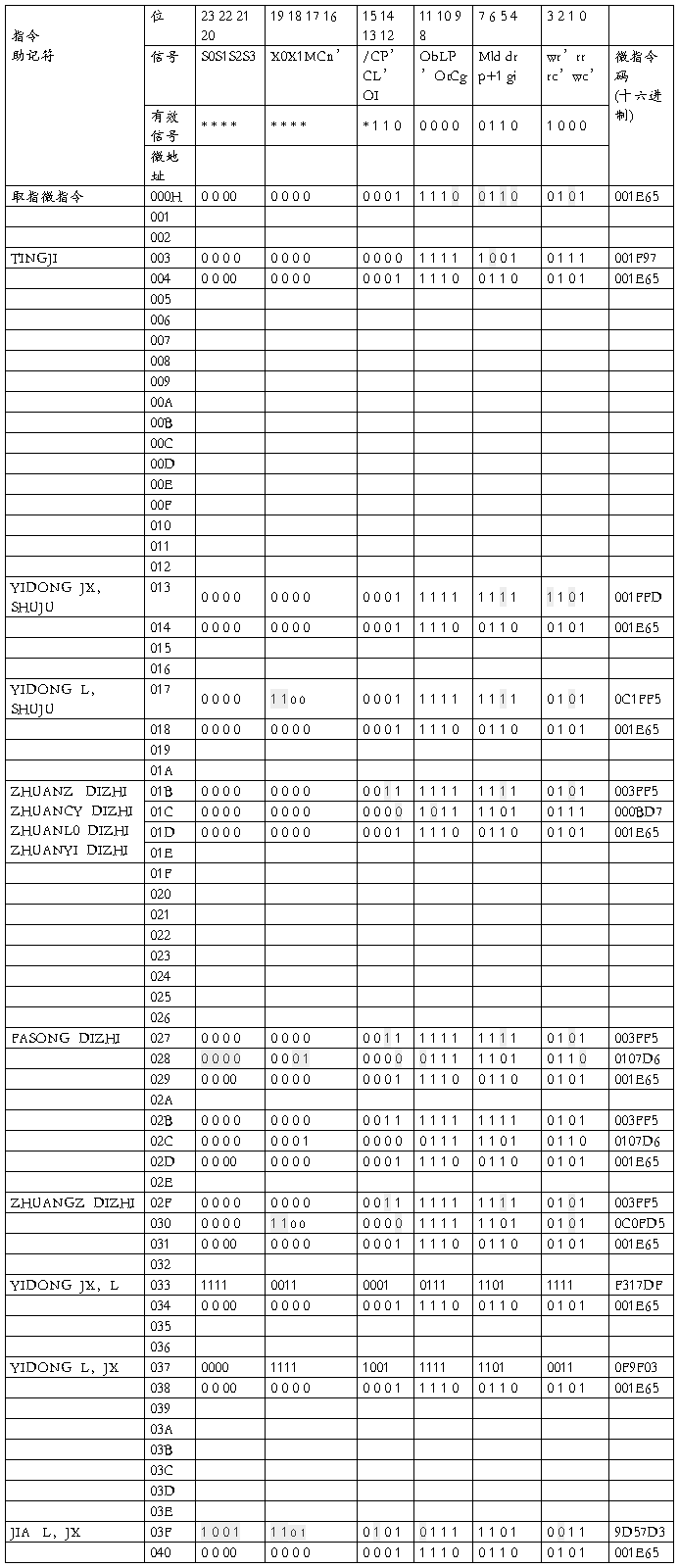

指令的微地址及微指令

M23 M22 M21 M20 M19 M18 M17 M16 M15 M14 M13

S0 S1 S2 S3 X0 X1 M /CN / CP CL

M12 M11 M10 M9 M8 M7 M6 M5 M4 M3 M2 M1 M0

OI OB LP OT CG MLD DR P+1 GI WR RR RC WC

表四 微指令表

3.4 编写并执行应用程序

汇编程序为:

ORG 100

START: YIDONG L,#03

YIDONG J1,#05

JIA L,J1

FASONG 00D

TINGJI

要求使用机器汇编和手工汇编两种方法执行应用程序,最后结果放在00D中,即显示08。

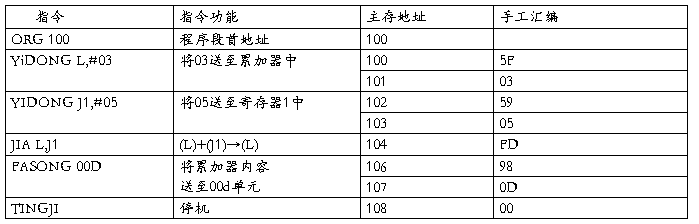

(1)手工汇编(对照表一系统)

ORG 100

START: YIDONG L,#03 ; 5F03H

YIDONG J1,#05 ; 5905H

JIA L,J1 ; fd98H

FASONG 00D ; 0D00H

TINGJI ; 00

包括微指令存控存,将指令存入主存。

a.将微指令装入控存CM中(开关拨至CM端)

b.将指令装入主存M中(开关拨至M端)

c.检查结果如下:

(2) 机器汇编方法

FD-CES系统软件视为FD-CES实验仪于PC机相连以构成高层次试验系统用的配套软件,它提供屏幕编辑、汇编、反汇编、文件传送及调试等功能,该软件在Windows 下运行。

在设计实验计算机时,需要通过屏幕编辑来设计四类文件,即:

a. 微指令定义文件(BIT.DEF):

用户可定义24位长的微指令的各位意义,在调试时将显示对应位的微指令的有效操作、高电平操作、低电平操作或无效操作。

源程序:S0 S1 S2 S3 X0 X1 M /CN NONE CP CL OI

OB LP OT CG MLD DR P+1 GI WR RR RC WC

b.指令定义文件(INS.DEF)

源程序:

;This is an example for multi accumulator ( book page-153):

?2

-JIA -YIDONG -YIDONG

4 4 4

L,JX L,JX JX,L

111111JX 110111JX 110110JX

-ZHUANGZ -FASONG -ZHUANZ

3 3 3

DIZHI DIZHI DIZHI

10111aaa 10011aaa 01100aaa

a7-a0 a7-a0 a7-a0

-ZHUANCY -ZHUANL0 -ZHUANYI

3 3 3

DIZHI DIZHI DIZHI

01101aaa 01110aaa 01111aaa

a7-a0 a7-a0 a7-a0

-YIDONG -YIDONG -TINGJI

2 2 1

L,#SHUJU JX,#SHUJU 00000000

01011111 010110JX

SHUJU SHUJU

c.微程序文件(MOP*.MID)

;This is an example for multi accumulator ( book page-155 ):

;get the first instrution

;TINGJI

;000H~002H ;003H~006H ;007H~00AH ;00BH~00EH

-001E65 -001F97 - -

- -001E65 - -

- - - -

- - -

;00FH~012H ;YIDONG JX,#SHUJU ;YIDONG L,#SHUJU ;ZHUANZ DIZHI

- ;013H~016H ;017H~01AH ;01BH

- -001FFD -0C1FF5 -003FF5

- -001E65 -001E65

- - -

- -

;ZHUANCY DIZHI ;ZHUANL0 DIZHI ;ZHUANYI DIZHI ;ZHUANZ DIZHI

;01CH ;01DH ;01EH ;01FH

-000BD7 -001E65 - -003FF5

;ZHUANCY DIZHI ;ZHUANL0 DIZHI ;ZHUANYI DIZHI

;020H ;021H ;022H

-000BD7 -001E65 -

;FASONG DIZHI ;FASONG DIZHI ;ZHUANGZ DIZHI ;ZHUANGZ DIZHI

;023H~026H ;027H~02AH ;02BH~02EH ;02FH~032H

-003FF5 -003FF5 -003FF5 -003FF5

-0107D6 -0107D6 -0C0FD5 -0C0FD5

-001E65 -001E65 -001E65 -001E65

- - - -

;YIONG JX,L ;YIDONG L,JX ;03BH~03EH ;JIA L,JX

;033H~036H ;037H~03AH - ;03FH~042H

-F317DF -0F9F03 - -9D57D3

-001E65 -001E65 - -

- - - -

- - -

d.两个汇编程序文件(*.ASM)

汇编源程序编译之后将产生目标文件(*.OBJ),当调试时则需将目标文件下载至内存。

程序一: 程序二:

ORG 100 ORG 100

YIDONG L,#03 YIDONG J2,#02 FASONG 00BH

YIDONG J1,#05 YIDONG L,#05 ZHUANYI M2

JIA L,J1 JIA L,J2 M1: YIDONG L,#00

FASONG 00D ZHUANCY M1 FASONG 00BH

END YIDONG L,#01 M2: END

(3)文件下载

a.下载Micor Program

此项功能将用户的微程序的目标代码(*.DAT)从PC机下载到实验计算机的控存中,用户可选择所需传送程序的文件名,并定义其在Control Memory中的起始地址,确认前需将M\CM开关置于CM端。

b.BIT.DEF

此项功能系统将用户的微指令位定义文件(BIT.DEF)读入。

c.下载Program

此项功能将用户的调机程序的目标文件(*.OBJ)从PC机下载到实验计算机的内存中,用户可选择所需传送程序的文件名,并定义其在实验计算机内存中的起始地址,确认前需将M\CM开关置于M端。

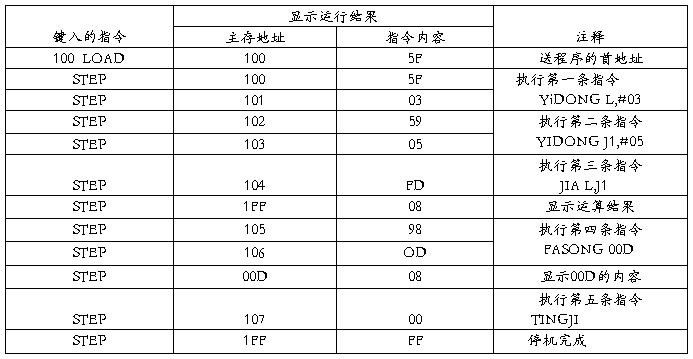

(4)实验机运行

用户完成逻辑框图的选择、内存的源程序目标代码装入、控存的微程序代码装入以及BIT.DEF的装入后,就可以开始调试、运行了。

运行功能包括三种:Start at、Step、Run。

Strat at要求用户输入运行程序的起始地址,地址用十六进制表示。

Step允许用户单步运行程序。

Run 提供连续运行程序的功能。

(5)运行结果

对于程序一,我们采用Run方法运行程序,运行程序以后检验00D单元的内容,经检验00D单元的内容为0D,实验结果正确。

对于程序二,我们采用Run方法运行程序,运行程序以后检验00B单元的内容,若00B的内容为0的话,说明此时有进位;如果内容为1的话,没有进位;此题我们设计的没有进位,所以最后00B的内容1。

四 心得体会

通过这一次的课程设计,我收获很大,我了解了一个比较简单的模型计算机的实现,真正了解了计算机组成原理的实际意义,而且在整个制作过程中,我们遇到了很多错误,出现错误时,在更改的过程,体会其中的种种困难,了解到了难点的地方,这对于我们学习计算机硬件方面的课程有着很大的帮助,同时对于之前的几次试验我们操作机器的实验理解、总结也更加的深刻了,在设计过程中,我从开始对硬件的迷惑和只懂个大概,到中间的疑惑与焦虑甚至无奈放弃,到解决了所有问题和疑惑。突然有一种雨过天晴的感觉。对于整个实验过程,首先,我们按提示进行初步的定位,寻找合适的地址指令,安排指令,出现错误时,就先查找错误所在位置进而仔细检查是否代码错误或者其他系统性的错误或是机器、接线的错误,从而根据错误行修改,操作时一定要注意规范程度避免带来不必要的麻烦,给系统的正常运行带来麻烦,在制作过程中经常出现代码错误,经过仔细的思考我们进行改进。而且,这对于我们以后工作也有着很大的好处,培养了我们遇到问题,分析问题,解决问题各个方面上的能力。平时我们做作业也都是在做书本上面给我们的题目,而这一次则是由我们自己设计出的,这对我们的创新意识也是一种很大大培养。我认为这次经历,是一次很好的锻炼的机会。

我们希望学校以后可以多为我们提供这样的机会,这样我们就可以在实践中得到平时课堂上面所缺失的一些能力,同时希望学校可以在别的学科也可以小组成员里这样给我们提供更好的条件来进行教学。这样可以使我们的综合素质的到很好的提升。

这个课程设计,在做的过程中遇到过很多难题,最后能够完成,还是要感谢老师和同学的大力辅导和帮助,还有一些有关书籍的帮忙。最后完成了这个课程设计。