1.课程设计目的与作用

1.1了解同步计数器及序列信号发生器工作原理;

1.2掌握计数器电路的分析,设计方法及应用;

1.3掌握序列信号发生器的分析,设计方法及应用;

2设计任务

2.1六进制同步计数器

1. 使用设计一个循环型3位2进制加法计数器,其中无效状态为(001,101),组合电路选用与门和与非门等。

2. 根据自己的设计接线。

3. 检查无误后,测试其功能。

2.2序列信号发生器

1. 使用设计一个能循环产生给定序列的序列信号发生器,其中发生

(101011),组合电路选用与门和与非门等。

2. 根据自己的设计接线。

3.检查无误后,测试其功能。

2.3加法计数器

1.基于集成芯片74ls163 和门电路组成一个24进制激发计数器并显示计数过程

2. 根据自己的设计接线。

3.检查无误后,测试其功能。

3设计原理

3.1同步计数器

(1)计数器是用来统计输入脉冲个数电路,是组成数字电路和计算机电路的基本时序 逻辑部件。计数器按长度可分为:二进制,十进制和任意进制计数器。计数器不仅有加法计数器,也有减法计数器。如果一个计数器既能完成累加技术功能,也能完成递减功能,则称其为可逆计数器。在同步计数器中,个触发器共用同一个时钟信号。

(2)时序电路的分析过程:根据给定的时序电路,写出各触发器的驱动方程,输出方程,根据驱动方程带入触发器特征方程,得到每个触发器的词态方程;再根据给定初太,一次迭代得到特征转换表,分析特征转换表画出状态图。

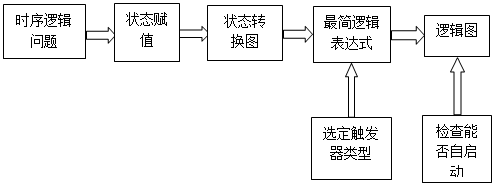

(3)设计过程:设计流程如图1所示。

图1 同步时序逻辑电路设计流程

3.1.1加法计数器

CP是输入计数脉冲,所谓计数,就是记CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器记满时再来CP脉冲,计数器归零的同时给高位进位,即要给高位进位信号。

3.1.2减法计数器

CP是输入减法计数脉冲,每输入一个CP脉冲,计数器就减一个1,当不够减时就向高位借位,显然向高位借来的1应当8,8-1=7。因此在状态为000时,输入一个CP脉冲,不够减,向高位借1当8,减去1后剩7,所以计数器的状态应该由000转换到111,且同时应向高位送出借位信号。

3.2序列信号发生器

(1) 序列是把一组0,1数码按一定规则顺序排列的串行信号,可以做同步信号地址码,数据等,也可以做控制信号。

(2) 计数型序列信号发生器是在计数器的基础上加上反馈网络构成。要实现序列长度为M序列信号发生器。其设计步骤为:

a 先设计一个计数模值为M的计数器;

b 再令计数器每一个状态输出符合序列信号要求;

C 根据计数器状态转换关系和序列信号要求设计输出组合网络。

3.3用集成芯片设计一个24进制的加法器

选取两片74LS163设计由状态00000000~00100100的24进制加法计数器。

74LS163具有以下功能:

★同步清零功能

当 时,CP来上升沿时,计数器清零。

时,CP来上升沿时,计数器清零。

★同步并行置数功能

当 、

、 时,在CP上升沿操作下,并行输入数据

时,在CP上升沿操作下,并行输入数据 进入计数器,使

进入计数器,使

。

。

★二进制同步加法计数功能

当 时,若

时,若 ,则计数器对CP信号按照8421编码进行加法计数。

,则计数器对CP信号按照8421编码进行加法计数。

★保持功能

当 时,若

时,若 ,则计数器将保持原来状态不变。对于进位信号有两种情况,如果

,则计数器将保持原来状态不变。对于进位信号有两种情况,如果 ,那么

,那么 ;若是

;若是 ,则

,则 。

。

4.仿真结果分析

4.1同步减法器(无效状态001 101)

4.1.1 过程分析

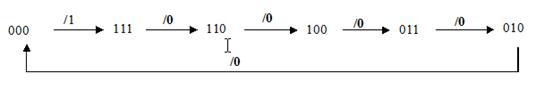

状态转换图

状态转换图

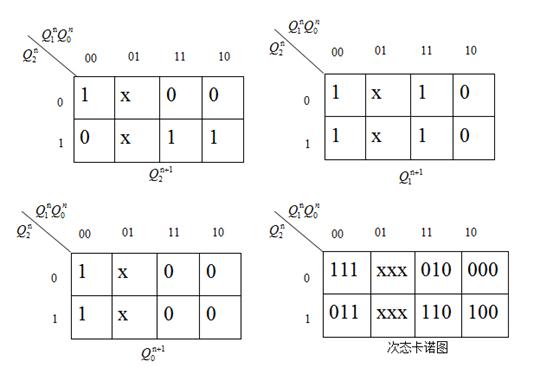

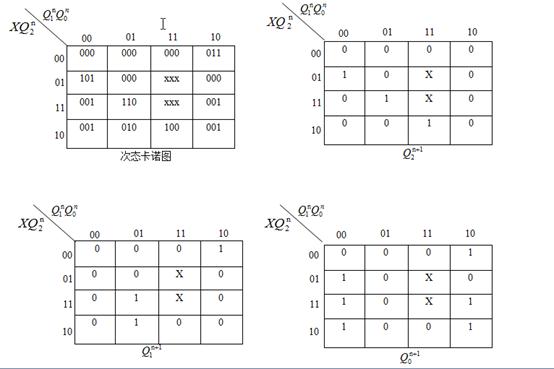

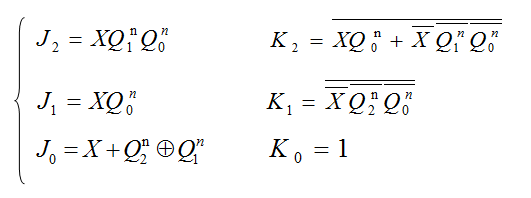

卡诺图

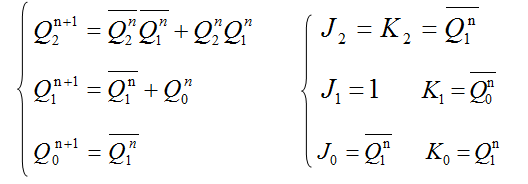

驱动方程

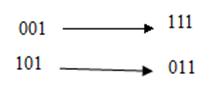

无效状态转换图

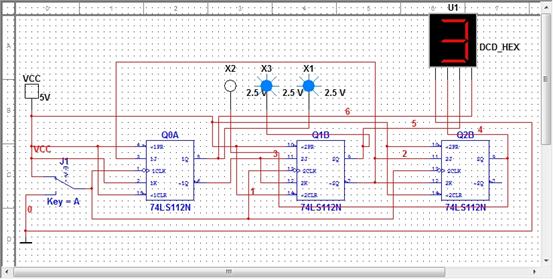

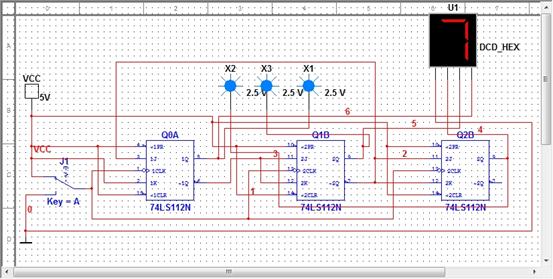

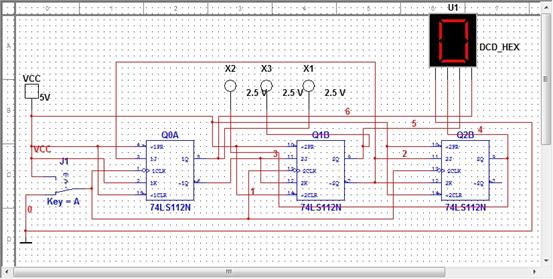

4.1.2 仿真效果

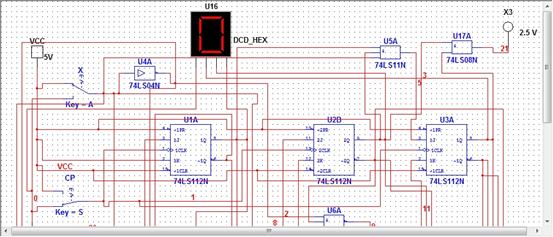

通过双击按键A产生CP脉冲,数码管显示计数,指示灯显示二进制计数,无效状态为001 101为六进制计数,计到7(111)回到初始状态0(000)效果如下图。

图1

图2

图3

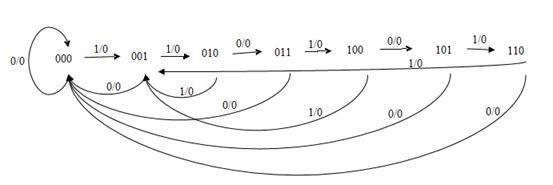

4.2序列信号发生器(检测101011)

4.2.1 过程分析

序列检测器检测101011通过JK触发器构成序列检测器

状态转换图

卡诺图

卡诺图化简图

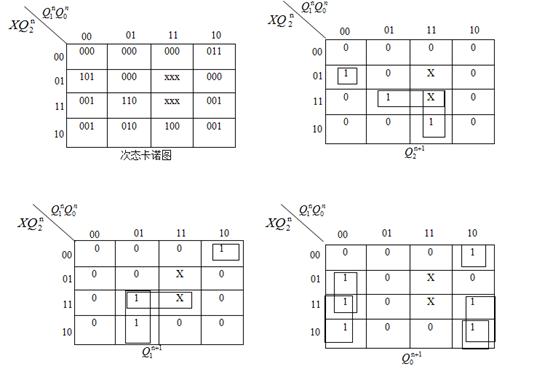

状态方程

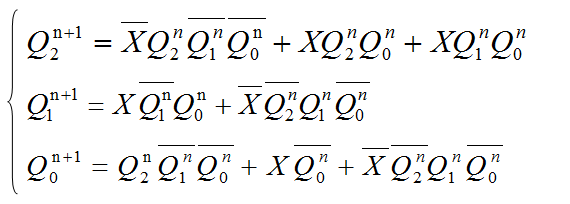

驱动方程

4.2.2 仿真效果图

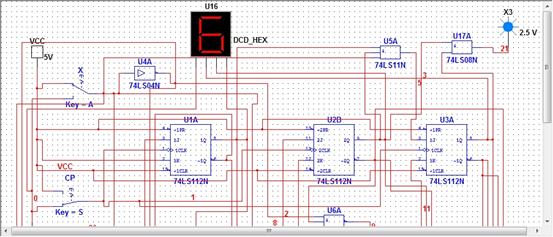

通过KEY A给X赋值0或1也就是序列码,双击KEY S产生CP脉冲,序列检测器是由JK触发器构成,数码管是显示检测到第几位,指示灯是显示以检测到指定的序列码。如果当中有错误的码,回到初始状态0(000)。效果如下

图4

图5

图6

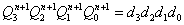

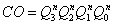

4.3基于74ls163 24进制加法计数器

4.3.1 过程分析

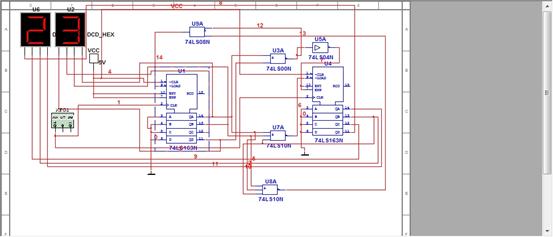

本加法计数器是基于74LS163 构成24 进制的加法计数器

24进制有两片74LS163构成个位和十位,十位计数到2(0011)就清零,Q2接在非门输入端,输出端接在163的置数端(LD).

个位每逢为9或个位为3且十位为2清零。

4.3.1 仿真结果

本加法计数器是基于74LS163 构成24 进制的加法计数器,函数发生器产生方波每逢一次上升沿记一次数,两个数码管分别显示十位和个位的数字。效果如下

图7

图8

5设计总结与体会

通过本次课程设计使我对同步计数器及序列信号发生器工作原理有了更深的了解,同时掌握计数器电路的分析,设计方法及应用和序列信号发生器的分析,设计方法及应用,基本能够独立设计出一般简单的电路。

6参考文献

1《数字电子技术基础简明教程》 余孟尝 高等教育出版社

2《数字电子技术实验》 张利萍.王向磊 沈阳理工大学出版

第二篇:数电 课设

4路彩灯显示系统

一 实验目的

熟悉常用中规模计数器的逻辑功能 掌握计数 译码电路的工作原理及应用

熟悉移位寄存器的工作原理 典型应用和调试方法 二 实验仪器与器件

数字电路实验箱

器件:74LS194 74LS161 74LS00 74LS32 74LS10 三 实验任务与要求

设计一个4路彩灯控制器,要求

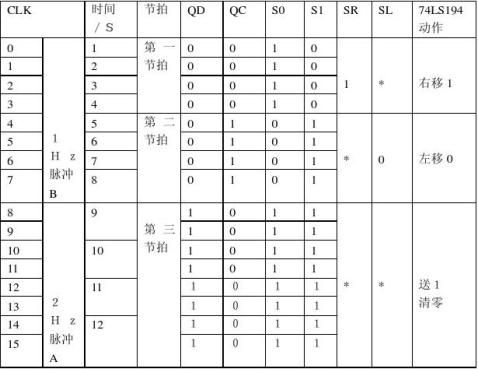

1开机后可自动从初始状态按规定程序进行循环演示 2 彩灯花形由三个节拍组成

第一节拍:逐次渐亮,亮灯时间为1s ,共用4s。

第二节拍:4路彩灯按顺序渐灭,也需4s。

第三节拍:4路彩灯同时亮0.5s,然后同时变暗0.5s,要进行4次,所需时间也为4s,3个节拍完成一个循环。 3彩灯用发光二极管模拟 四 设计思路

根据课程设计课题要求,要实现本系统,需要有时钟脉冲,循环控制电路和彩灯花样输出电路。时钟脉冲产生电路由74LS161分频实现,循环控制电路由74LS161和其他门电路实现,彩灯花样输出电路由74LS194和相关逻辑电路实现。

彩灯的三个节拍可以用移位寄存器74LS194实现,通过控制S0和S1实现右移、左移和送数,通过控制CLR'控制清零。第一节拍为1右移,第二节拍为0左移,第三节拍全亮为置数1,全灭为清零。由于程序循环一次要12秒,故需要一个12进制的计数器控制循环。第三节拍时要求1秒内全灭全亮各一次,故脉冲信号频率比先前两节拍时脉冲频率要快一倍,而且要以相同频率控制CLR’。可以用一个16进制计数器产生脉冲信号,一路送到控制12进制的计数器,一路经逻辑电路送到移位寄存器。

输 入 /CR S1 0 1 1 1

2、通过12进制计数器的输出端的C、D信号控制移位寄存器的S0和S1及其CLR'端真× 1 0 1

S0 × 1 1 0

CP × ↑ ↑ ↑

SL × × × 0

SR × × 1 ×

D0 D1 D2 D3 × d0 × ×

× d1 × ×

× d2 × ×

× d3 × ×

输 出 Q0 Q1 Q2 Q3 0 d0 1

0 d1

0 d2

0 d3

清 零 送 数 功 能

Q0n Q1n Q2n 右 移

左 移

Q1n Q2n Q3n 0

值表