电路设计与仿真八

实验目的:

1. 学习常用时序电路的分析、设计及测试方法。

2. 掌握同步二进制计数器,异步二进制计数器的工作原理。

3. 掌握加、减法计数器的设计方法。

实验原理:

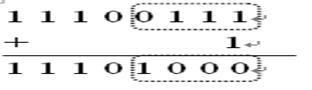

根据二进制加法运算规则,在一个多位二进制的 i位一下各位皆为1时,则第i位应改变状态。而最低位的状态在每次加1时都要改变。例如:

实验内容:

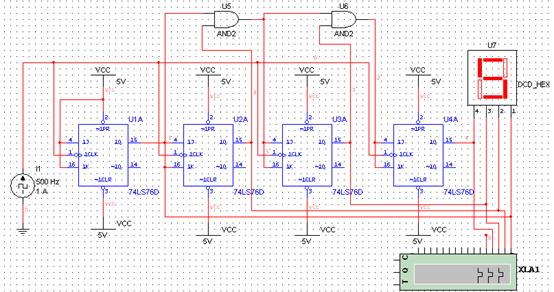

1. 实验电路图如图所示,按图连接电路,电路为一个二进制加法计数器,运行仿真,观察电路的工作状态;记录电路图及实验结果于实验报告中

电路图如下:

上图的驱动方程为:

J1=K1=1;

J2=K2=Q1;

J3=K3=Q1Q2;

J4=K4=Q1Q2Q3;

由JK触发器的特性方程Q*=JQ’+K’Q可知状态方程为:

Q1*=Q1’;

Q2*=Q1Q2’+Q1’Q2=Q1  Q2;

Q2;

Q3*=Q1Q2Q3;+(Q1Q2)’Q3=(Q1Q2)  Q3;

Q3;

Q4*=Q1Q2Q3Q4’+(Q1Q2Q3)’Q4=(Q1Q2Q3)  Q4;

Q4;

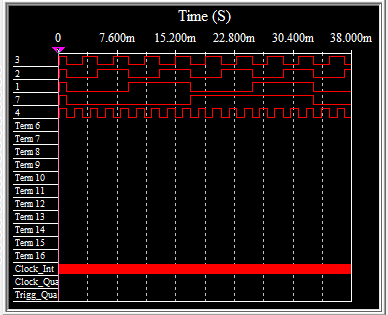

将Q1Q2Q3Q4的原态0000代入状态方程,可以得到0001——1111的十六个循环状态,当电路的下降沿信号到第十六个时,回到0000状态,即该电路可以计0——15共16个数,与逻辑分析仪的波形图结果一致。

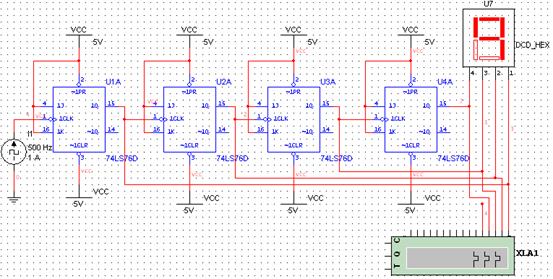

2. 实验电路图如图所示,按图连接电路,电路为一个异步二进制加法计数器,运行仿真,观察电路的工作状态;记录电路图及实验结果于实验报告中

电路图如下:

上图的驱动方程为:

J1=K1=1;

J2=K2=1;

J3=K3=1;

J4=K4=1;

由JK触发器的特性方程Q*=JQ’+K’Q可知状态方程为:

Q1*=Q1’;

Q2*=Q2’ ;

Q3*=Q3’;

Q4*=Q4’ ;

由电路图可知,第一个JK触发器接收第一个下降沿信号时,Q*=Q’=1;后面的JK触发器时钟信号始终为0,保持,故输出数字1。由此可知,后面的JK触发器都由前面的JK触发器输出Q*决定,据此,可以推出电路的各状态。

逻辑分析仪结果为:

第二篇:时序电路设计

实验二时序电路设计

一. 实验内容

使用Verilog语言完成一个时序电路模块的RTL设计,并为这个模块设计一个简单的testbench文件,并用ncverilog完成仿真过程,用拷屏的方法,完成WORD格式的实验报告,记录仿真结果的波形输出。

二. 时序电路模块设计要求

(1)滤波器电路设计

使用一个乘法器和一个加法器,设计完成一个五阶数字滤波器的设计,输入为串行数据X,复位信号RST,时钟信号CLK,使能信号EN,输出为串行数据信号Y,数据输出有效信号OEN。数字滤波器公式为:

y(i) = a0+ a1*x(i-1)+ a2*x(i-2)+ a3*x(i-3)+ a4*x(i-4)+ a5*x(i-5)

其中:

a0=0.08

a1=0.13

a2=0.23

a3=0.14

a4=0.16

a5=0.26

用Verilog语言为这个滤波器设计一个testbench,要求输入激励X为随机数据输入。

(2)接口设计

为上述设计一个外部接口,可以通过该接口对滤波器的系数a0~ a5进行改写,在上述testbench基础上,完成滤波器系数配置的配置验证,系数配置如下:

a0=0.20

a1=0.04

a2=0.08

a3=0.20

a4=0.16

a5=0.32

三. 实验过程

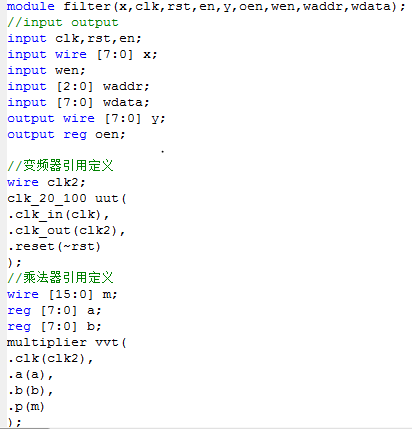

(1)分析滤波器程序需要的模块:

1)根据滤波器的公式,得知该程序需要一个乘法器模块2)i时刻输出与前5个时刻的输入有关,因此需要6个寄存器用来保存x输入的值 3)i时刻输出完成了5次乘法5次加法,因此需要一个变频器产生一个5倍频的时钟 4)需要定义五个状态,每个状态实现相应的乘法和加法操作。

(2)在给定a的5个值时出现一个问题,小数如何用二进制表示:

将滤波器公式左右同时乘以2的八次方,即所有的二进制数值左移八位,此时系数均四舍五入保留整数位,转换成二进制形式即可。将最终的计算结果高八位赋值给y即为滤波器的输出。计算得:a0=00010100,a1=00100001,a2=00111011,a3=00100100,a4=00101001,

a5=01000011。

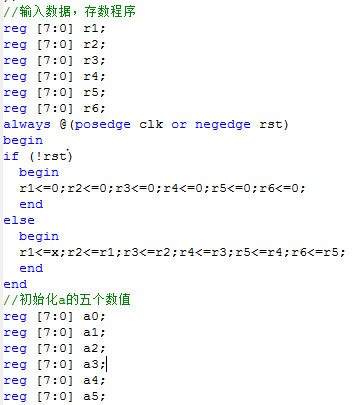

(3)第一部分:定义输入输出变量,变频器和乘法器的引用定义

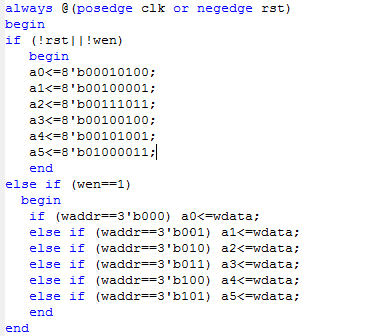

(4)第二部分:定义6个寄存器,给5个系数a赋值

这里定义了wen,waddr,wdata三个变量,为a输入的外部接口,当写入使能信号wen为1时,重新给a赋值,数值为输入信号wdata。

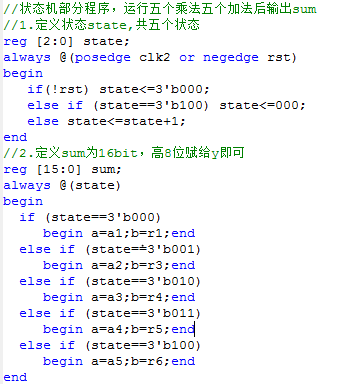

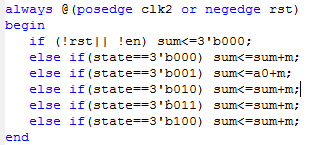

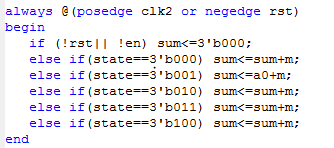

(5)第三部分:定义五个状态,每个状态完成一次乘法和一次加法

乘法器的输入赋值采用组合逻辑,根据不同的状态分别将不同的输入信号连入乘法器的输入端口,不需要时钟。加法运算采用时序逻辑,在clk2的上升沿完成一次加法,直至5次相加之和输出到sum中,这里的sum为16位二进制数。

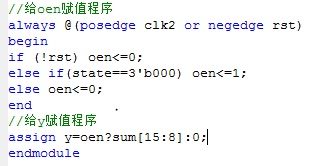

(6)第四部分:输出有效信号oen和y的赋值

当状态state为000时输出有效信号oen置1,同时输出y的值为sum的高八位,否则y输出为0。因为最初在公式两边同时乘以2的八次方了,所以最终的值为结果的高八位。

四. 实验结果

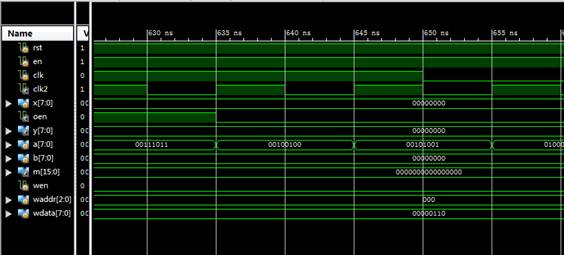

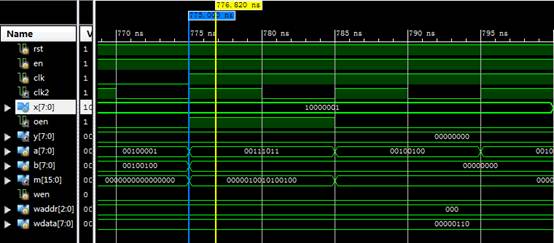

(1)700ns之前x的输入全是0,所以y的输出也一直为0,波形符合分析。

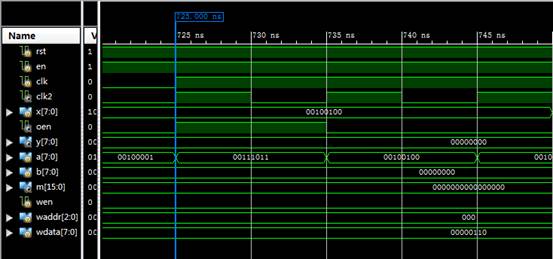

(2)725ns时刻,clk上升沿读入x的第一个值00100100(36),此时y输出仍为0

(3)775ns时刻,读入x第二个值10000001(129),y输出为0,因为此时y=a0=0.08,sum的高八位为0。

(4) 825ns时刻,读入x第三个值00001001(9),y输出为00000100(4),计算:a0=0.08,a1=0.13,y(i)=0.08+0.13*36=4.76,波形符合计算结果。

(5)875ns时刻,读入x的第四个值01100011(99),此时输出y的值00011001(25),计算:y=0.08+0.13*129+0.23*36=25.16,波形符合结果。

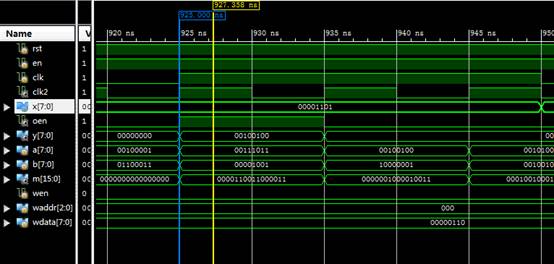

(6)925ns时刻,读入x的第五个值00001101(13),此时输出y的值00100100(36),计算:y=0.08+0.13*9+0.23*129+0.14*36=35.96,波形符合计算结果。

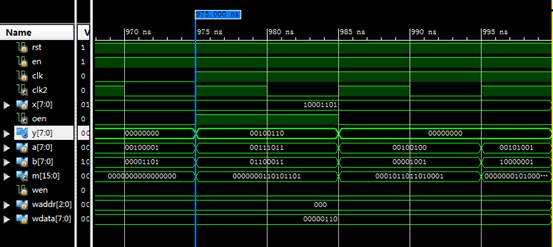

(7)975ns时刻,输出y的值00100110(38),计算:y=0.08+0.13*99+0.23*9+0.14*129+0.16*36=

38.84,波形符合计算结果。

(8)结果分析:由于仿真时间的限制,本次实验最终输出了四个不为0的y的值,每当五个状态运行完成时,oen变为1,同时输出y的值。经计算,波形输出的值为正确的滤波器输出。clk2也实现了clk的5倍频,每五个clk2之后输出一个y的值。

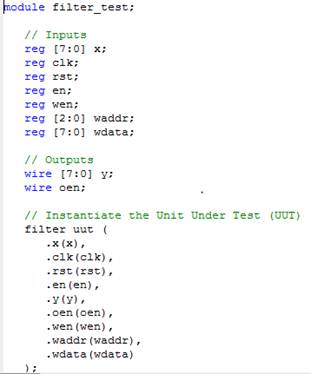

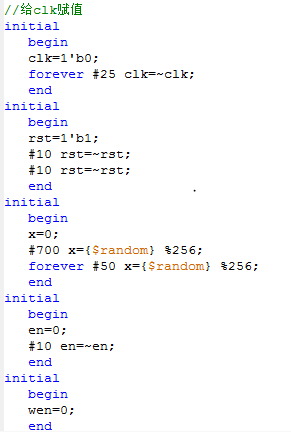

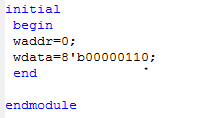

五. Testbench部分代码