实验报告

——常用电子仪器的使用与二端口网路参数的测量方法

实验目的:

⑴了解电子示波器(SS7804/7810)、函数信号发生器(EE1642B1)、直流稳压电源(DH1718E-4)等几种常用电子仪器的原理、主要技术指标。

⑵熟悉示波器状态的正确掌握方法(包括亮度、聚焦、触发源与触发方式、耦合方式、Y轴衰减器与时基单元等),掌握用示波器测量直流电源、交流电压(包括幅度、频率、相位差)、时间间隔以及脉冲波形的上升沿、下降沿等参数的方法。

⑶掌握函数信号发生器的正确调整方法。包括包括频率范围、频率微调、占空比、直流偏移、输出衰减、输出幅度等的调节。

⑷结合常用电子仪器的使用,学习二端口网路主要参数(输入电阻、输出电阻、增益、幅频特性等的测量方法。

⑸学习用示波器测量电路的电压传输特性。学习信号发生器直流偏移功能的应用。

实验原理:

⑴电子示波器(SS7804)的使用方法:

1.按下电源开关打开示波器。

2.调节亮度旋钮,若扫描线未显示,使用寻迹开关寻找。

3.将CH1/CH2连出的线连到校准信号输出端,检验Y轴灵敏度和X轴的扫描速度。

4.将要测的信号接入CH1/CH2,根据要求调整示波器的AC/DC档。调节Y轴位移旋钮,使扫描线移动到显示器正中间,再调整水平位置微调键使扫描线停止不动。

5.利用游标或屏幕的显示数据来完成实验内容。

⑵函数信号发生器(EE1642B1)的使用方法:

1. 按下电源开关,打开信号发生器。

2. 使用函数输出波形选择键选择输出波形。

3. 调节APML键调节函数信号的输出幅度。,再用RATE

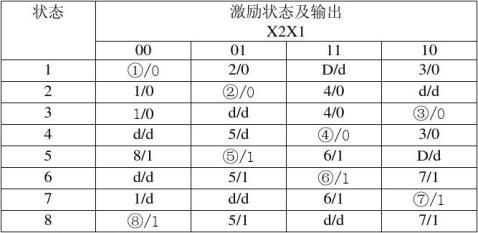

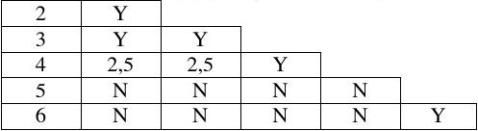

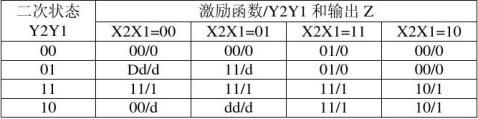

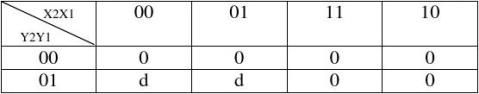

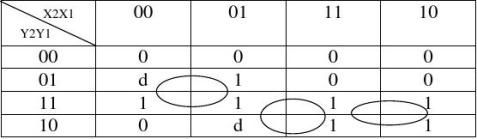

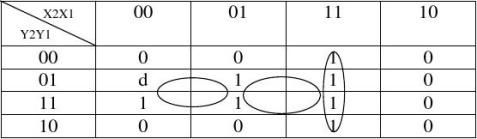

…… …… 余下全文

,

, ;

; ,

, ;

; ,

,

=

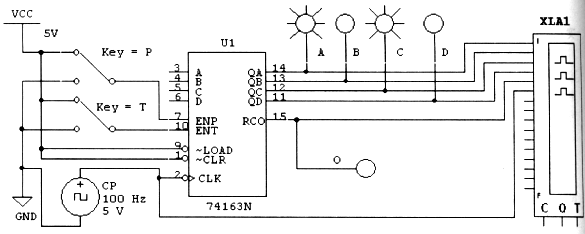

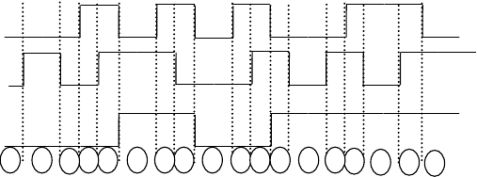

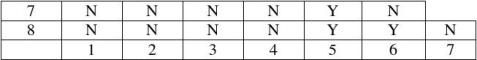

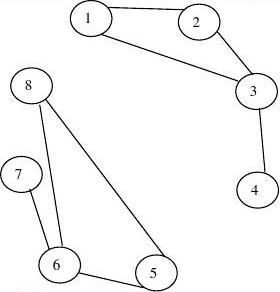

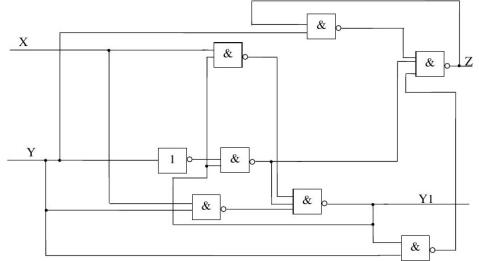

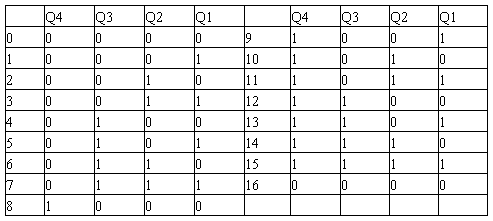

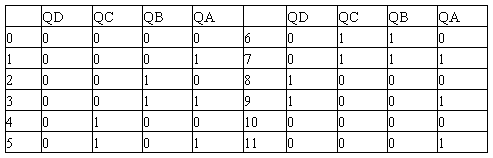

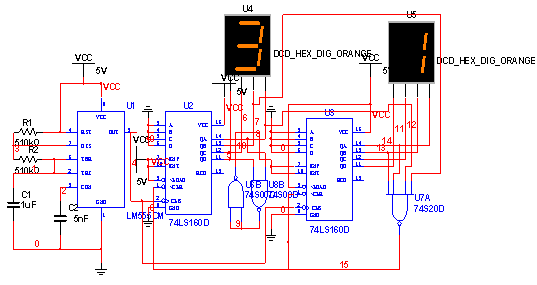

= 计图如下:

计图如下:

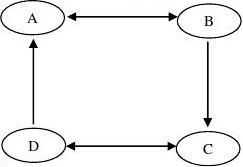

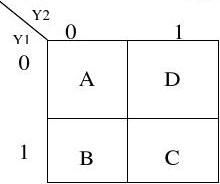

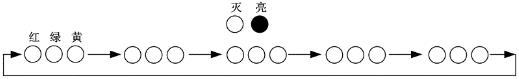

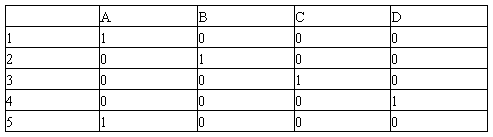

,用两个与非门实现该功能。则当

,用两个与非门实现该功能。则当 =1,

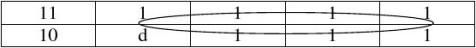

=1, =0,且时钟信号来临时,计数器置数QA1QB1QC1QD1=0000,置数信号LD=

=0,且时钟信号来临时,计数器置数QA1QB1QC1QD1=0000,置数信号LD= 则设计电路为:

则设计电路为: