阶段性考核之三:【平时成绩15分】

时序逻辑部分设计型实验报告

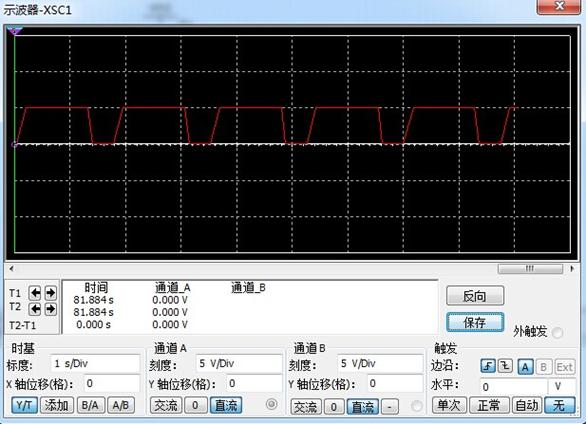

附录1:整体清零法仿真电路图

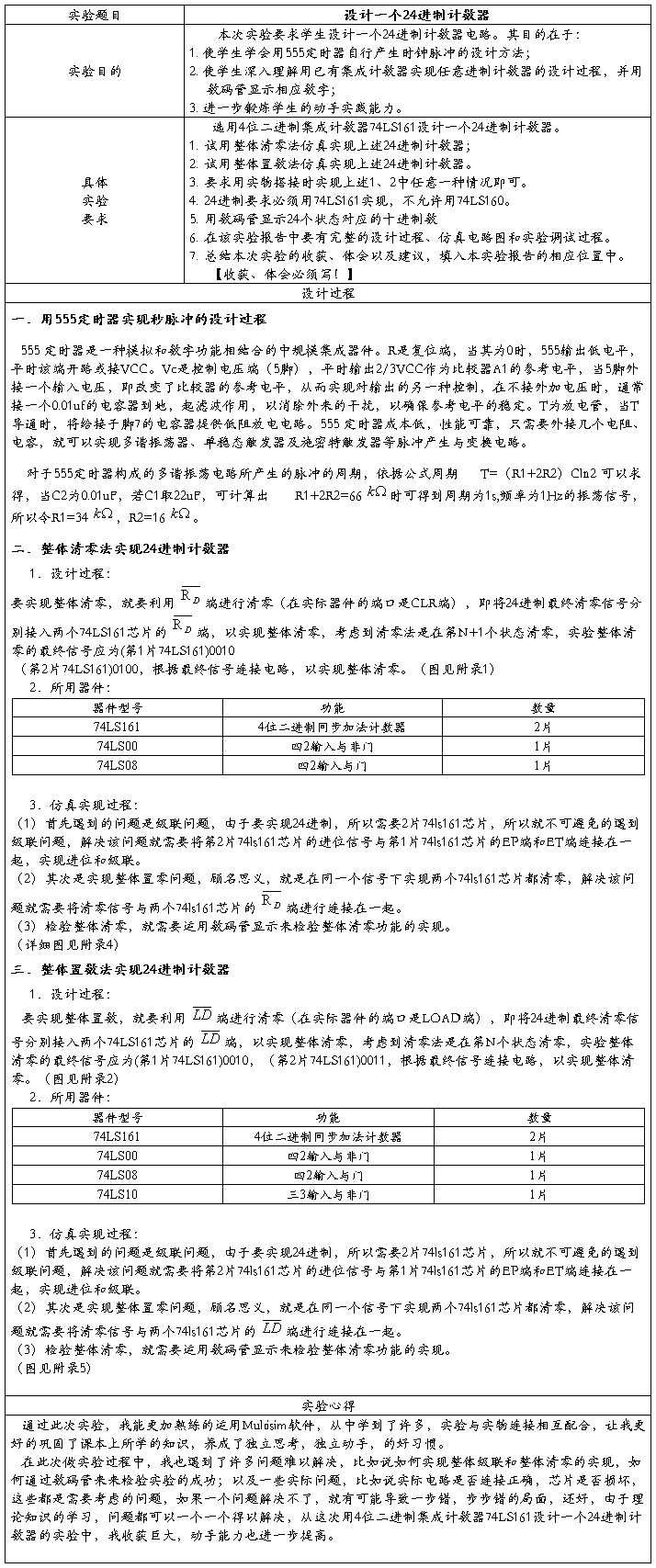

附录2:整体置数法仿真电路图

附录3:方案二仿真电路图

附录4:方案三仿真电路图(整体清零法实现24进制)

译码器的主要任务是将控制器的输出 Q1、 Q0的4种工作状态,翻译成甲、乙车道上6个信号灯的工作状态。控制器的状态编码与信号灯控制信号之间的关系如表 12、4所示。实现上述关系

附录5:方案四仿真电路图(整体置数法实现24进制)

第二篇:关于时序逻辑电路设计与仿真的实验

中北大学信息与通信工程学院实验报告

课程名称 基于VHDL的CPLD/FPGA开发与应用

实验项目名称 实验4 时序逻辑电路设计与仿真

学生姓名 彭营 专业班级 08050641 学号 0805064112

实验成绩 指导老师(签名) 日期 2011.10.20

一. 实验目的

1.学习使用MaxPlus II(Quartus II)软件;

2.掌握VHDL语言设计基本单元及其构成;

3.掌握VHDL语言设计基本的时序逻辑电路及仿真的方法;

4.学会编译,调试,仿真,分析所设计的时序逻辑电路;

二. 实验内容

1.设计带使能的递增计数器;

2.在步骤1的基础上设计一带使能的同步(异步)复位的递增(递减)计数器;

3.在步骤1的基础上设计同步(异步)清零的同步(异步)复位的递增(递减)计数器;

三. 函数的功能说明及算法思路

1.请编写带使能的递增计数器的VHDL代码;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ycounter is

port(clk,ld,enable:in std_logic;

d:in integer range 0 to 255;

qk:out integer range 0 to 255);

end ycounter;

architecture a_ycounter of ycounter is

begin

PROCESS (clk)

VARIABLE cnt : INTEGER RANGE 0 TO 255;

BEGIN

IF (clk'EVENT AND clk = '1') THEN

IF(enable = '1') THEN

cnt := cnt + 1;

END IF;

END IF;

qk <= cnt;

END PROCESS;

end a_ycounter;

2.在步骤1的基础上请编写带使能的同步(异步)复位的递增(递减)计数器的VHDL代码;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ycounter is

port(clk,clear,ld,enable:in std_logic;

d:in integer range 0 to 255;

qk:out integer range 0 to 255);

end ycounter;

architecture a_ycounter of ycounter is

begin

PROCESS (clk)

VARIABLE cnt : INTEGER RANGE 0 TO 255;

BEGIN

IF (clk'EVENT AND clk = '1') THEN

IF(ld = '0') THEN

cnt := d;

ELSE

IF(enable = '1') THEN

cnt := cnt + 1;

END IF;

END IF;

END IF;

END IF;

qk <= cnt;

END PROCESS;

end a_ycounter;

3.在步骤1的基础上请编写同步(异步)清零的同步(异步)复位的递增(递减)计数器的VHDL代码;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ycounter is

port(clk,clear,ld,enable:in std_logic;

d:in integer range 0 to 255;

qk:out integer range 0 to 255);

end ycounter;

architecture a_ycounter of ycounter is

begin

PROCESS (clk)

VARIABLE cnt : INTEGER RANGE 0 TO 255;

BEGIN

IF (clk'EVENT AND clk = '1') THEN

IF(clear = '0') THEN

cnt := 0;

ELSE

IF(ld = '0') THEN

cnt := d;

ELSE

IF(enable = '1') THEN

cnt := cnt + 1;

END IF;

END IF;

END IF;

END IF;

qk <= cnt;

END PROCESS;

end a_ycounter;

四. 实验结果与分析

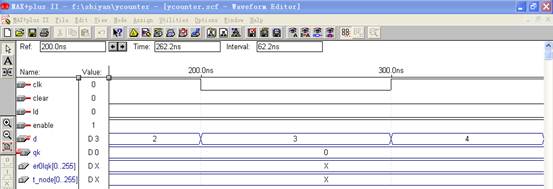

1.请对带使能的递增计数器的功能进行仿真,把仿真的结果图附上;

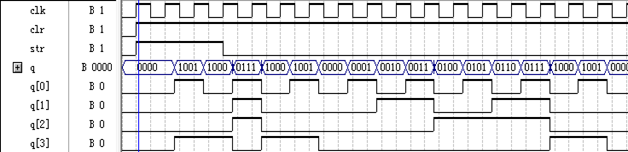

2.请对带使能的同步(异步)复位的递增(递减)计数器的功能进行仿真,把仿真的结果图附上;

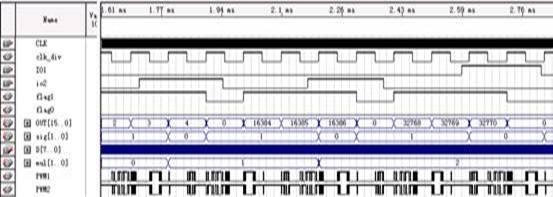

3.请对同步(异步)清零的同步(异步)复位的递增(递减)计数器的功能进行仿真,把仿真的结果图附上;

五. 心得体会

这次实验是设计一个带使能的同步(异步)复位的递增(递减)计数器和同步(异步)清零的同步(异步)复位的递增(递减)。通过本次实验我掌握了VHDL设计基本的时序逻辑电路及仿真,掌握了Quartus II软件时钟的加入方法和触发器同步复位和异步复位的实现方式。本实验中时序逻辑电路在时钟脉冲的上升沿或下降沿的控制下才能发生状态变化。因此时钟信号通常是描述时序逻辑电路程序的执行条件。VHDL语言提供了测试时钟脉冲敏感边沿的语句和函数,如触发器功能的实现。通过今天的实验我在软件上验证了信号和变量的主要区别,进一步熟悉了该软件的使用。