成绩评定表

课程设计任务书

目 录

目 录............................................................ III

1.绪 论.......................................................................................................................... 1

1.1设计背景......................................................................................................... 1

1.2设计目标......................................................................................................... 1

2.Y= 电路和版图设计................................................................................... 2

电路和版图设计................................................................................... 2

2.1 Y= 电路结构................................................................................... 3

电路结构................................................................................... 3

2.2 Y= 电路仿真................................................................................... 4

电路仿真................................................................................... 4

2.3 Y= 的电路版图绘制....................................................................... 5

的电路版图绘制....................................................................... 5

2.4 Y= 的版图电路仿真....................................................................... 6

的版图电路仿真....................................................................... 6

2.5LVS检查匹配................................................................................................... 7

总 结.............................................................................................................................. 9

参考文献...................................................................................................................... 10

附录一:原理图网表.................................................................................................. 11

附录二:版图网表...................................................................................................... 12

1.绪 论

1.1设计背景

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

Tanner Tools Pro提供完整的集成电路设计环境,可在PC机上运行,能够帮助学生进入VLSI设计领域。它从电路图设计、电路分析与仿真到电路布局环境一应俱全。学生通过仿真实验能够进一步深化对集成电路原理、半导体工艺等方面知识的理解和掌握,将电子科学与技术专业的基础知识融会贯通。

1.2设计目标

1.用tanner软件中的原理图编辑器S-Edit编辑Y= 电路原理图。

电路原理图。

2.用tanner软件中的TSpice对Y= 电路进行仿真并观察波形。

电路进行仿真并观察波形。

3.用tanner软件中的L-Edit绘制Y= 版图,并进行DRC验证。

版图,并进行DRC验证。

4.用tanner软件中的TSpice对Y= 电路进行仿真并观察波形。

电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对Y= 进行LVS检验观察原理图与版图的匹配程度。

进行LVS检验观察原理图与版图的匹配程度。

2.Y= 电路和版图设计

电路和版图设计

2.1 Y= 电路结构

电路结构

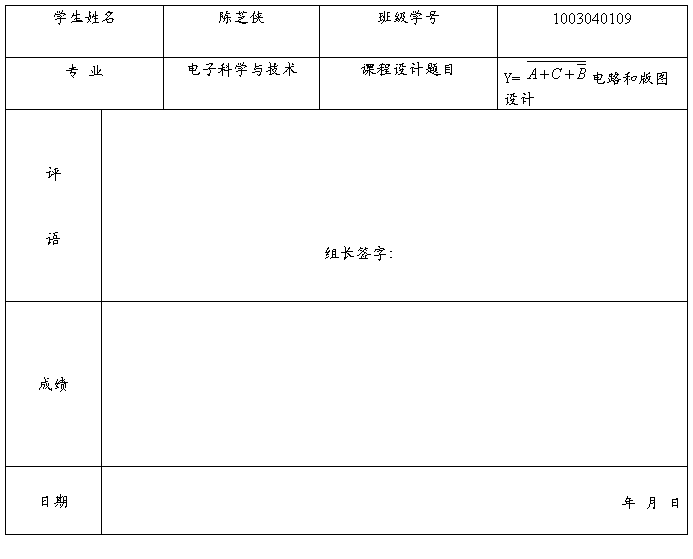

Y= 以说是最常用的基本功能电路之一了,广泛应用于数字逻辑三输入或非门电路设计中。在本次课程设计中,使用tanner软件中的原理图编辑器S-Edit编辑电路原理图。详细描述各MOS管中栅、源、漏及衬底的详细连接方式。其布尔表达式为Y=

以说是最常用的基本功能电路之一了,广泛应用于数字逻辑三输入或非门电路设计中。在本次课程设计中,使用tanner软件中的原理图编辑器S-Edit编辑电路原理图。详细描述各MOS管中栅、源、漏及衬底的详细连接方式。其布尔表达式为Y= ,其中原理图如图2.1。

,其中原理图如图2.1。

图2.1 Y= 的原理图2.2

的原理图2.2

2.2 Y= 电路仿真

电路仿真

2.2.1 使用TSpice对原理图进行仿真。

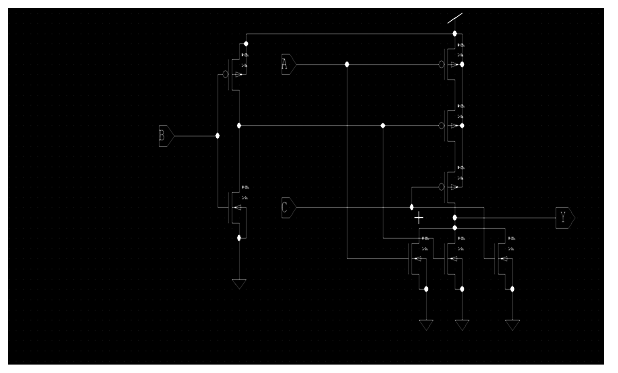

首先,生成电路网表,如图2.2。

图2.2 生成原理图电路网表

给输入端加入CP激励信号,信号D端加入信号。仿真中高电平为Vdd=5V,低电平为Gnd,并添加输入输出延迟时间。进行仿真,输出波形。波形图如下图2.3。

图2.3 Y= 的输入输出波形图

的输入输出波形图

2.3 Y= 的版图绘制

的版图绘制

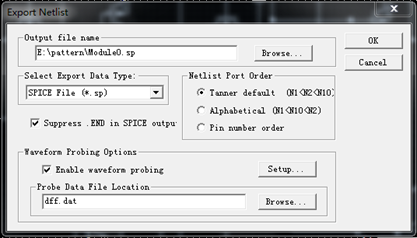

用L-Edit版图绘制软件对Y= 电路进行版图绘制,版图结果如图2.4。

电路进行版图绘制,版图结果如图2.4。

图2.4 Y= 电路版图

电路版图

进行DRC检测,检测是否满足设计规则。如图2.5。

图2.5 DRC验证结果

2.4 Y= 的版图电路仿真

的版图电路仿真

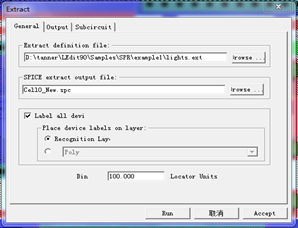

同原理图仿真相同,首先生成电路网表。如图2.6。

图2.6 生成版图电路网表

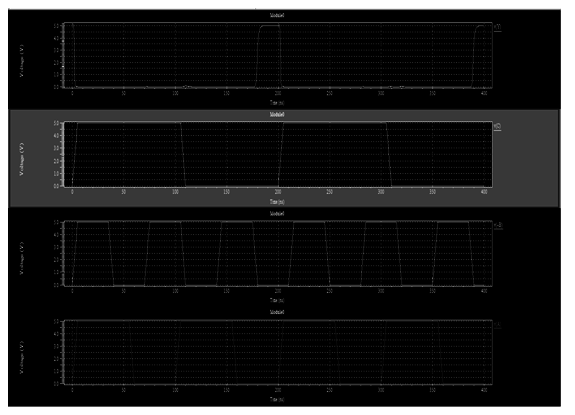

添加激励、电源和地,同时观察输入输出波形,波形如图2.7。

图2.7 Y= 输出波形图

输出波形图

Y= 电路的版图仿真波形与原理图的仿真波形,基本一致,并且符合输入输出的逻辑关系,电路的逻辑设计正确无误。

电路的版图仿真波形与原理图的仿真波形,基本一致,并且符合输入输出的逻辑关系,电路的逻辑设计正确无误。

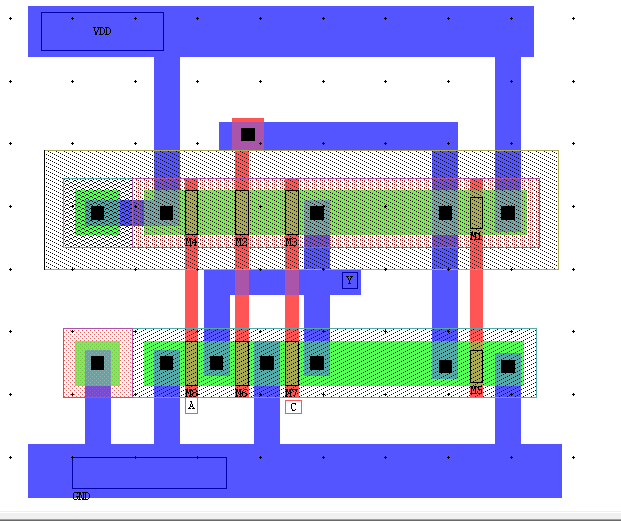

2.5 LVS检查匹配

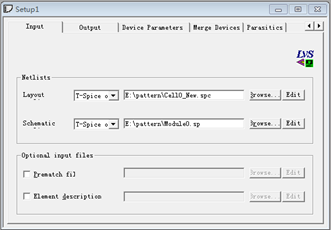

对Y= 进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,观察输出结果检查Y=

进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,观察输出结果检查Y= 电路原理图与版图的匹配程度。

电路原理图与版图的匹配程度。

首先导入网表,如下图图2.5.1。

图2.5.1 导入网表

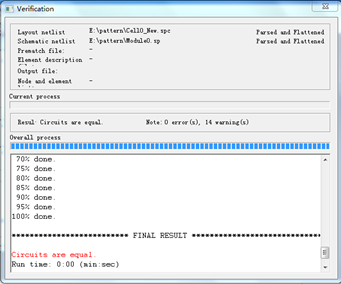

输出结果如图2.5.2。

图2.5.2 电路LVS检查匹配图

总 结

通过这段时间的课程设计学习,综合运用所学的知识完成了设计任务。使我更深的的了解版图工艺的艺术,并深入掌握仿真方法和工具 Tanner、同时为以后从事本专业工作打下坚实的基础。进一步熟悉设计中使用的主流工具,版图设计属于集成电路的后端设计,通过绘制电路版图,发现了理论与现实有着很大的差别,特别是绘制版图,需要很大的耐心和毅力,刚开始对Tanner软件很陌生,感觉画图好复杂呀,失败了一次又一次,最后通过耐心的学习和尝试,终于对Tanner软件和版图绘制的掌握,画出了漂亮的版图让人感觉好有成就感啊,让我深深体会到集成电路版图工艺的魅力,通过对典型IC集成电路的原理图和版图的绘制及仿真,对模拟电路的工作原理有了进一步的了解。再借助tanner软件模拟电路的原理图绘制及其版图生成,熟悉了tanner在此方面的应用,以增强计算机辅助电路模拟与设计的信心。

由于对于理论知识学习不够扎实,我深感“书到用时方恨少”,于是想起圣人之言“温故而知新”,便重拾教材与实验手册,对知识系统而全面进行了梳理,遇到难处先是苦思冥想再向同学请教,终于熟练掌握了基本理论知识,而且领悟诸多平时学习难以理解掌握的较难知识,学会了如何思考的思维方式,找到了设计的方向。正所谓“实践是检验真理的唯一标准”,只有自己动手做过了,才能更贴切更深刻的掌握所学的知识,使自己进一步的提高。尽管课程设计是在期末才开始,我们的教材学习完毕,掌握许多知识,但是还有很多地方理解领悟不到位,所以查阅资料使必不可少的,这就养成了我们自己学习的方式。而且又要进行软件的仿真。软件的仿真进行的比较顺利,硬件的连接出了一些问题。但最后解决了。

总的来说,课程设计是一门很严谨的的课程,给了我很多专业知识,同时在一定程度上提高了我的专业技能,还教给我许多的道理。通过课程设计,我不仅学到了知识,而且从中学到了解决问题的方法,这也是一个锻炼自己的机会。

参考文献

[1]Alan Hastings著.模拟电路版图的艺术.第三版.电子工业出版社,2013.6.

[2]曾庆贵等著.集成电路版图设计.第二版.机械工业出版社,2008.10.

附录一:原理图网表

* SPICE netlist written by S-Edit Win32 7.03

* Written on Jul 5, 20## at 10:59:29

* Waveform probing commands

.probe

.options probefilename="czx.dat"

+ probesdbfile="C:\Users\lenovo\Desktop\czx\czx.sdb"

+ probetopmodule="Module0"

.include D:\tanner\TSpice70\models\ml2_125.md

.param 1=0.5u

vvdd Vdd Gnd 5

va A Gnd PULSE (0 5 50n 5n 5n 50n 100n)

va B Gnd PULSE (0 5 50n 5n 5n 100n 150n)

va C Gnd PULSE (0 5 50n 5n 5n 60n 120n)

.tran/op 1n 400n method=bdf

.print tran v(A) v(B) v(C) v(Y)

* Main circuit: Module0

M1 Y N10 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M2 N10 B Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M3 Y A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M4 Y C Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M5 N10 B Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M6 N1 A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M7 N2 N10 N1 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M8 Y C N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

* End of main circuit: Module0

附录二:版图网表

* Circuit Extracted by Tanner Research's L-Edit Version 9.00 / Extract Version 9.00 ;

* TDB File: C:\Users\lenovo\Desktop\czx\Layout1.tdb

* Cell: Cell0 Version 1.17

* Extract Definition File: D:\tanner\LEdit90\Samples\SPR\example1\lights.ext

* Extract Date and Time: 07/05/2013 - 11:13

.include D:\tanner\TSpice70\models\ml2_125.md

.param 1=0.5u

vvdd Vdd GND 5

va A GND PULSE (0 5 50n 5n 5n 50n 100n)

vb B GND PULSE (0 5 50n 5n 5n 100n 150n)

vc C GND PULSE (0 5 50n 5n 5n 60n 120n)

.tran/op 1n 400n method=bdf

.print tran v(A) v(B) v(C) v(Y)

* Warning: Layers with Unassigned AREA Capacitance.

* <Poly Resistor ID>

* <Poly2 Resistor ID>

* <N Diff Resistor ID>

* <P Diff Resistor ID>

* <P Base Resistor ID>

* <N Well Resistor ID>

* <Pad Comment>

* <Poly1-Poly2 Capacitor ID>

* <Poly Resistor ID>

* <Poly2 Resistor ID>

* <N Diff Resistor ID>

* <P Diff Resistor ID>

* <P Base Resistor ID>

* <N Well Resistor ID>

* Warning: Layers with Zero Resistance.

* <Pad Comment>

* <Poly1-Poly2 Capacitor ID>

* <NMOS Capacitor ID>

* <PMOS Capacitor ID>

* NODE NAME ALIASES

* 1 = GND (-20,25)

* 2 = VDD (-25,95)

* 4 = Y (23,57)

* 9 = B (43.5,90)

M1 VDD B 3 VDD PMOS L=2u W=5u

* M1 DRAIN GATE SOURCE BULK (43.5 83.5 45.5 88.5)

M2 7 3 8 VDD PMOS L=2u W=7u

* M2 DRAIN GATE SOURCE BULK (6 65.5 8 72.5)

M3 Y 6 7 VDD PMOS L=2u W=7u

* M3 DRAIN GATE SOURCE BULK (14 65.5 16 72.5)

M4 8 5 VDD VDD PMOS L=2u W=7u

* M4 DRAIN GATE SOURCE BULK (-2 65.5 0 72.5)

M5 GND B 3 GND NMOS L=2u W=5u

* M5 DRAIN GATE SOURCE BULK (43.5 65 45.5 70)

M6 GND 3 Y GND NMOS L=2u W=7u

* M6 DRAIN GATE SOURCE BULK (6 41.5 8 48.5)

M7 Y 6 GND GND NMOS L=2u W=7u

* M7 DRAIN GATE SOURCE BULK (14 41.5 16 48.5)

M8 Y 5 GND GND NMOS L=2u W=7u

* M8 DRAIN GATE SOURCE BULK (-2 41.5 0 48.5)

* Total Nodes: 9

* Total Elements: 8

* Total Number of Shorted Elements not written to the SPICE file: 0

* Extract Elapsed Time: 0 seconds

.END