黄冈师院物电学院

《EDA技术》课程设计报告

项目名称: 多模式流水灯设计

专业年级: 电子信息工程20##级

学 号: 201022240202

学生姓名:

指导教师: 冯 杰

报告完成日期 20## 年 12 月 30 日

评阅结果 评阅教师

第一章 绪论

1.1 系统背景

1.1.1、EDA技术

EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

1.1.2、实验内容

设计可以多模式控制的流水灯,并用Max+PlusⅡ10.2进行编译和仿真,可以在实验箱上实现自己的需求功能。

1.1.3、设计要求

可以进行不同频率选择及不同模式选择进行组合,必须有手动选择组合,至少4种流水灯方式

第二章 系统电路设计

2.1 系统总体设计框架结构

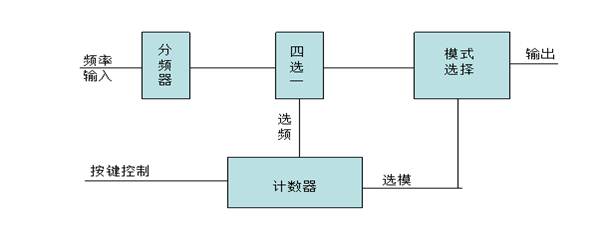

设计原理 : 由分频器实现2、4、8、16的分频,设计一个十六进制计数器,由低位控制四选一电路,高位控制模式选择电路。模式选择则由状态机来实现四种状态之间的转换。

2.2系统单元电路设计

2.2.1分频器

设计程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.std_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CLK_DIV IS

PORT(CLK : IN STD_LOGIC;

CLK_DIV2 :OUT STD_LOGIC;

CLK_DIV4 :OUT STD_LOGIC;

CLK_DIV8 :OUT STD_LOGIC;

CLK_DIV16 :OUT STD_LOGIC);

END CLK_DIV;

ARCHITECTURE RTL OF CLK_DIV IS

SIGNAL COUNT : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF (CLK'EVENT AND CLK='1') THEN

IF(COUNT="1111") THEN COUNT<=(OTHERS=>'0');

ELSE COUNT<=COUNT+1;

END IF;

END IF;

END PROCESS;

CLK_DIV2<=COUNT(0);

CLK_DIV4<=COUNT(1);

CLK_DIV8<=COUNT(2);

CLK_DIV16<=COUNT(3);

END RTL;

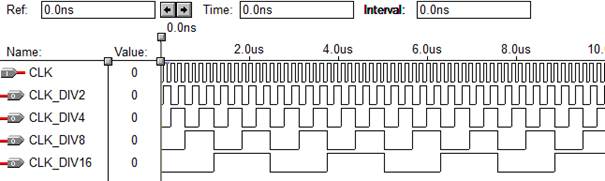

仿真分析:本程序用VHDl语言,对时钟信号进行2分频、4分频、8分频、16分频。由仿真波形图看出:CLK_DIV2、CLK_DIV4、CLK_DIV8、CLK_DIV16的时钟周期分别是CLK的2倍,4倍,8倍,16倍。所以该程序实现了2分频、4分频、8分频、16分频,及达到了设计目的。

仿真波形:

2.2.2 四选一电路

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

entity MUX4_1 IS

PORT (a,b,c,d: in std_logic;

s1,s2: in std_logic;

y : out STD_LOGIC);

END ENTITY MUX4_1;

ARCHITECTURE one OF MUX4_1 IS

BEGIN

y <= a when s1 = '0' and s2='0'

else b when s1 = '0' and s2='1'

else c when s1 = '1' and s2='0'

else d when s1 = '1' and s2='1'

else '0';

end ARCHITECTURE one;

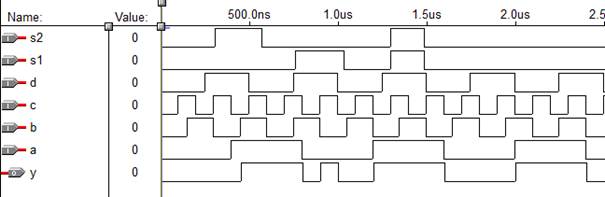

仿真波形:

仿真结果分析:由仿真图可以看出,当s1=0,s2=0时,输出Y=a;当s1=0,s2=1时,输出y=b;当s1=1,s2=0时,输出Y=c;当s1=1,s2=1时,输出Y=d;所以,该程序实现了四选一的目的,达到了设计要求。

2.2.3 十六进制计数器

程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY CNT_16 IS

PORT( CLRN,CLK: IN STD_LOGIC;

A:OUT STD_LOGIC_vector(1 downto 0);

B:OUT STD_LOGIC_vector(1 downto 0));

END CNT_16;

ARCHITECTURE a OF CNT_16 IS

BEGIN

PROCESS(CLK,CLRN)

VARIABLE tmpha:std_logic_vector(3 downto 0);

BEGIN

IF CLRN='1' THEN tmphA := "0000";

ELSIF CLK'event AND CLK='1' THEN

if tmpha<15 then tmpha:=tmpha+1;

else tmphA := "0000";

END IF;

end if;

CASE tmpha IS

WHEN "0000"=>B<="00";A<="00";

WHEN "0001"=>B<="00";A<="01";

WHEN "0010"=>B<="00";A<="10";

WHEN "0011"=>B<="00";A<="11";

WHEN "0100"=>B<="01";A<="00";

WHEN "0101"=>B<="01";A<="01";

WHEN "0110"=>B<="01";A<="10";

WHEN "0111"=>B<="01";A<="11";

WHEN "1000"=>B<="10";A<="00";

WHEN "1001"=>B<="10";A<="01";

WHEN "1010"=>B<="10";A<="10";

WHEN "1011"=>B<="10";A<="11";

WHEN "1100"=>B<="11";A<="00";

WHEN "1101"=>B<="11";A<="01";

WHEN "1110"=>B<="11";A<="10";

WHEN "1111"=>B<="11";A<="11";

WHEN others=>B<="00";A<="00";

END CASE;

END PROCESS ;

END a;

仿真波形:

仿真结果分析:

由仿真图可以看出,A作为计数器的低位,B作为计数器的高位,对脉冲Clk进行计数。实现了十六进制计数的功能。达到了设计的目的。

2.2.4状态机程序

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SJ IS

PORT (RESET,CLK :IN STD_LOGIC;

a1,a2 :IN STD_LOGIC;

Y :OUT STD_LOGIC_VECTOR (15 DOWNTO 0));

END sJ;

ARCHITECTURE behv OF SJ IS

TYPE FSM_ST IS(s0,s1,s2,s3,S4,S5,S6,S7,S8,S9,S10,S11,S12,S13,S14,S15);

SIGNAL current_state,next_state:FSM_ST;

BEGIN

REG: PROCESS(reset,clk)

BEGIN

IF reset ='1' THEN current_state <= s0;

ELSIF clk='1' AND clk 'EVENT THEN

current_state <= next_state;

END IF;

END PROCESS;

COM:PROCESS (current_state,a1,a2)

BEGIN

if a1='0' and a2='0'THEN

CASE current_state IS

WHEN S0=>Y<="0000000000000001"; NEXT_STATE<=S1;

WHEN S1=>Y<="0000000000000011" ;NEXT_STATE<=S2;

WHEN S2=>Y<="0000000000000111"; NEXT_STATE<=S3;

WHEN S3=>Y<="0000000000001111"; NEXT_STATE<=S4;

WHEN S4=>Y<="0000000000011111"; NEXT_STATE<=S5;

WHEN S5=>Y<="0000000000111111"; NEXT_STATE<=S6;

WHEN S6=>Y<="0000000001111111"; NEXT_STATE<=S7;

WHEN S7=>Y<="0000000011111111";NEXT_STATE<=S8;

WHEN S8=>Y<="0000000111111111" ;NEXT_STATE<=S9;

WHEN S9=>Y<="0000001111111111" ;NEXT_STATE<=S10;

WHEN S10=>Y<="0000011111111111" ;NEXT_STATE<=S11;

WHEN S11=>Y<="0000111111111111" ;NEXT_STATE<=S12;

WHEN S12=>Y<="0001111111111111" ;NEXT_STATE<=S13;

WHEN S13=>Y<="0011111111111111";NEXT_STATE<=S14;

WHEN S14=>Y<="0111111111111111" ;NEXT_STATE<=S15;

WHEN S15=>Y<="1111111111111111" ;NEXT_STATE<=S0;

END CASE;

elsif a1='0' and a2='1' THEN

CASE current_state IS

WHEN S0=>Y<="0111111111111111"; NEXT_STATE<=S1;

WHEN S1=>Y<="0011111111111111" ;NEXT_STATE<=S2;

WHEN S2=>Y<="0001111111111111"; NEXT_STATE<=S3;

WHEN S3=>Y<="0000111111111111"; NEXT_STATE<=S4;

WHEN S4=>Y<="0000011111111111"; NEXT_STATE<=S5;

WHEN S5=>Y<="0000001111111111"; NEXT_STATE<=S6;

WHEN S6=>Y<="0000000111111111"; NEXT_STATE<=S7;

WHEN S7=>Y<="0000000011111111";NEXT_STATE<=S8;

WHEN S8=>Y<="0000000001111111" ;NEXT_STATE<=S9;

WHEN S9=>Y<="0000000000111111" ;NEXT_STATE<=S10;

WHEN S10=>Y<="0000000000011111" ;NEXT_STATE<=S11;

WHEN S11=>Y<="0000000000001111" ;NEXT_STATE<=S12;

WHEN S12=>Y<="0000000000000111" ;NEXT_STATE<=S13;

WHEN S13=>Y<="0000000000000011";NEXT_STATE<=S14;

WHEN S14=>Y<="0000000000000001" ;NEXT_STATE<=S15;

WHEN S15=>Y<="0000000000000000" ;NEXT_STATE<=S0;

END CASE;

elsif a1='1' and a2='0' THEN

CASE current_state IS

WHEN S0=>Y<="1000000000000001"; NEXT_STATE<=S1;

WHEN S1=>Y<="1100000000000011" ;NEXT_STATE<=S2;

WHEN S2=>Y<="1110000000000111"; NEXT_STATE<=S3;

WHEN S3=>Y<="1111000000001111"; NEXT_STATE<=S4;

WHEN S4=>Y<="1111100000011111"; NEXT_STATE<=S5;

WHEN S5=>Y<="1111110000111111"; NEXT_STATE<=S6;

WHEN S6=>Y<="1111111001111111"; NEXT_STATE<=S7;

WHEN S7=>Y<="1111111111111111";NEXT_STATE<=S8;

WHEN S8=>Y<="1111111001111111" ;NEXT_STATE<=S9;

WHEN S9=>Y<="1111110000111111" ;NEXT_STATE<=S10;

WHEN S10=>Y<="1111100000011111" ;NEXT_STATE<=S11;

WHEN S11=>Y<="1111000000001111" ;NEXT_STATE<=S12;

WHEN S12=>Y<="1110000000000111" ;NEXT_STATE<=S13;

WHEN S13=>Y<="1100000000000011";NEXT_STATE<=S14;

WHEN S14=>Y<="1000000000000001" ;NEXT_STATE<=S15;

WHEN S15=>Y<="0000000000000000" ;NEXT_STATE<=S0;

END CASE;

else a1='1' and a2='1' THEN

CASE current_state IS

WHEN S0=>Y<="0000000110000000"; NEXT_STATE<=S1;

WHEN S1=>Y<="0000001111000000" ;NEXT_STATE<=S2;

WHEN S2=>Y<="0000011111100000"; NEXT_STATE<=S3;

WHEN S3=>Y<="0000111111110000"; NEXT_STATE<=S4;

WHEN S4=>Y<="0001111111111000"; NEXT_STATE<=S5;

WHEN S5=>Y<="0011111111111100"; NEXT_STATE<=S6;

WHEN S6=>Y<="0111111111111110"; NEXT_STATE<=S7;

WHEN S7=>Y<="1111111111111111";NEXT_STATE<=S8;

WHEN S8=>Y<="0111111111111110" ;NEXT_STATE<=S9;

WHEN S9=>Y<="0011111111111100" ;NEXT_STATE<=S10;

WHEN S10=>Y<="0001111111111000" ;NEXT_STATE<=S11;

WHEN S11=>Y<="0000111111110000" ;NEXT_STATE<=S12;

WHEN S12=>Y<="0000011111100000" ;NEXT_STATE<=S13;

WHEN S13=>Y<="0000001111000000";NEXT_STATE<=S14;

WHEN S14=>Y<="0000000110000000" ;NEXT_STATE<=S15;

WHEN S15=>Y<="0000000000000000" ;NEXT_STATE<=S0;

END CASE;

end if;

end PROCESS;

END BEHV;

设计分析:该程序是根据状态机编写的四个模式的选择程序,由十六进制计数器的高位控制该程序中的a1、a2。当a1=0,a2=0时,选择效果一;当a1=0,a2=1时,选择效果二;当a1=1,a2=0时,选择效果三;当a1=1,a2=1时,选择效果四;

2.3系统设计电路

将2.2中的四段程序封装后按设计原理框图连接起来,得到如下原理图:

第三章 实验结果和分析

3.1 实验使用的仪器设备

安装有Max+plusⅡ10.2的计算机一台

仿真实验箱一台

3.2 测试结果分析

为验证所设计程序是否正确,将程序下载进行硬件测试。在MAX+PLUSⅡ开发环境中进行管脚锁定,连接好下载线,然后将目标文件下载到器件中。

经过测试,流水灯样式一共有4种,如模式选择程序描述的一样,且每一种效果有四种速度可调。通过按键调节显示样式及调节流水灯变化快慢。

结束语

经过一周的努力终于完成流水灯的设计,流水灯是由四个部分组成,其中包括分频器、四选一电路、十六进制计数器、状态选择器。在该次课程设计过程中,也遇到了许多问题,但通过查阅资料,上网查阅,问题都得到了解决。列如:在一个实体中,如果有两个或两个以上的进程,那么在各自的进程中,不能对同一个信号进行赋值;信号和变量的区别在于,信号在进程之外进行定义,而变量只能在某个进程中进行定义,在多进程执行的时候,外部进程不能使用本进程的变量。还有一个最为重要的问题就是,需要考虑资源量,一个芯片中可以下载进去的程序大小是有限的,在程序设计的时候尽量少申请变量和信号,对于信号和变量,位数能少则少,这样生成的模块资源才不会占用很大。

通过这次EDA试验设计,我感觉自己设计的流水灯功能虽然很简单,但从中我获得了许多。至少说又学会了一门VHDL语言,学会了MAX-PLUS II的使用,包括模块设计,波形仿真以及原理图的设计。我越来越相信只有通过自己动手实践,才能发现具体问题,才能够对问题有深刻的认识,最后才能从根本上解决问题。