组成原理课程设计报告

指导教师: 学生班级: 学生姓名: 学 号:

班内序号:

课设日期:1

目录

一、设计目的 ............................................................................. 错误!未定义书签。

二、设计要求 ........................................................................................................... 3

三、设计方案 ........................................................................................................... 3

四、设计过程 ........................................................................................................... 5

4.1 实验仪基本结构

4.2 电路生成与下载步骤

4.3 汇编语言源程序的编辑、编译

五、编程与调试程序方法 ...................................................................................12

六、课设结果及分析 ............................................................................................15

七、指令执行流程 .................................................................................................16

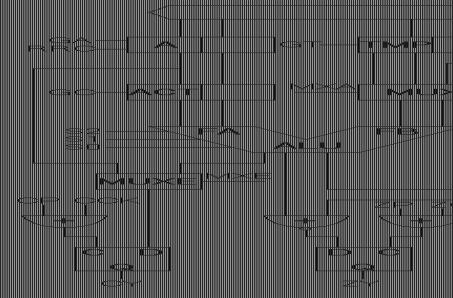

7.1模型计算机结构框图

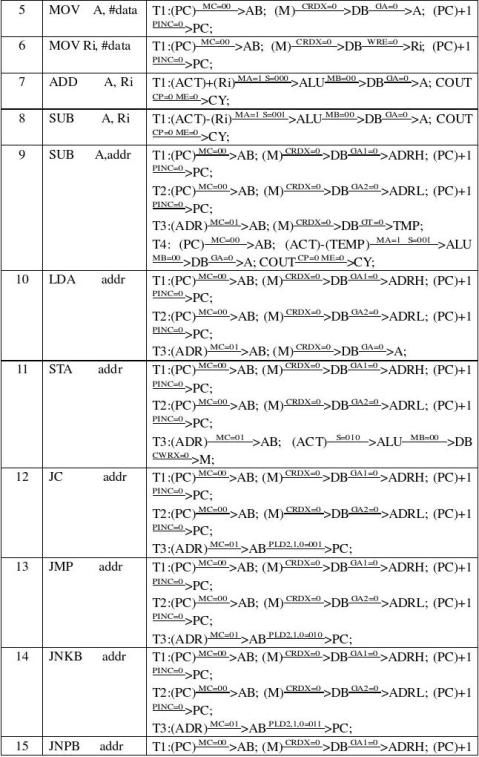

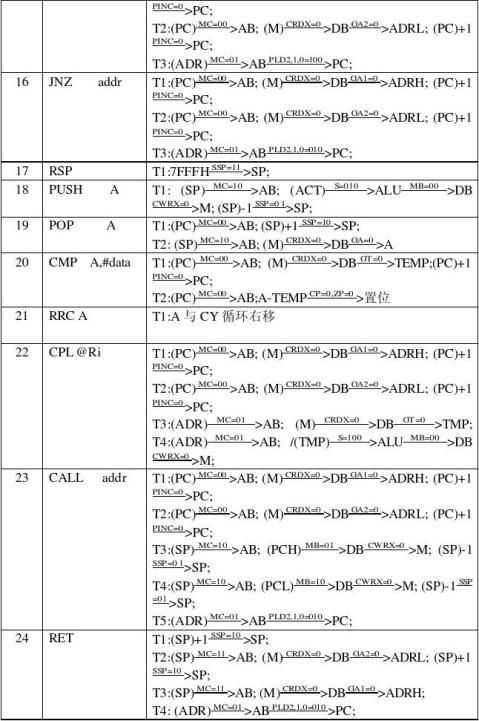

7.2指令流程定义表

八、收获体会及建议 ............................................................................................20

2

一、设计目的

1.利用《计算机组成与系统结构》、《汇编语言与微型计算机技术》、《可编程逻辑器件》课程的知识,设计一台微程序控制的模型计算机。通过本设计,主要掌握微程序控制结构计算机的设计方法,加深对计算机各部件的理解以及对整机结构的理解。

2.熟练VHDL语言在硬件设计中的应用。

二、设计要求

1.硬件设计,包括运算器、寄存器、寄存器、微程序控制器的VHDL描述。

2.软件设计,包括指令系统设计及应用程序的设计。

3.硬件和软件联合调试,利用设计的模型计算机执行应用程序,通过数码管显示结果。

三、设计方案

1.首先设计整机逻辑框图,并分析各主要部件中所使用的关键器件,彻底理解主要芯片的工作原理。

根据设计要求,对实验仪硬件模块进行逻辑剪辑组合,便可设计出该实验计算机的整机逻辑框图。为利于调试,应在逻辑框图上表明各器件的控制信号及必要的输出信号。

2.指令系统和指令执行流程设计

① 指令系统

需确定实验计算机的指令系统具体由哪里指令组成,包括哪几种类型

3

指令,指令操作数有哪几种寻址方式,以及指令编码等。

② 指令执行流程

应根据实验计算机整机逻辑图来设计指令系统中每条指令的执行流程。

一条指令从内存取出到执行完,需要若干个机器周期(节拍)。任何指令的第一个机器周期都是“取指令周期”,或称为公操作周期。而一条指令共需几个机器周期取决于指令在机内实现的复杂程度。

3.微操作控制信号和微程序设计

① 微操作控制信号及其实现方法

综合实验计算机指令系统各指令执行流程中所涉及到的微操作控制信号,统计总共需要多少个微控制信号,每个信号的有效性,决定这些信号中哪些由软件(微指令)直接产生,哪些需用硬件实现。

② 设计微指令格式,微指令由32位组成,设计出每位微操作的定义。 ③ 确定微程序控制方式

设计任务包括设计各微程序入口地址的形成方法和控存的顺序控制(即下地址形成)方法。

④ 编写各指令的微程序

根据指令流程和微指令格式仔细地逐条填写微指令各码位。

为减少填写错误,可边把本条微指令用到的微码(微操作控制信号)按预定的有效性填入,检查无误后,再对本条微指令用不到的微码(微操作控制信号)填入与预定的有效性相反的代码,核对无误后,最后将这32位微码缩写成8位十六进制微指令。

4

4.设计接线表

要仔细设计接线表,因为它是组装计算机的依据。

① 为了避免遗漏,应按模块逐个归纳整理,明确各模块中器件各控制信号的处理方法。

② 对于模块中不用的器件,也应有所处理。

四、设计过程

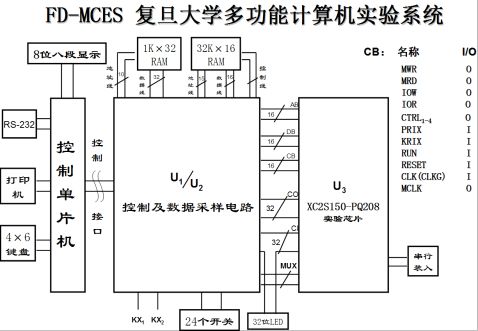

1、实验仪基本结构

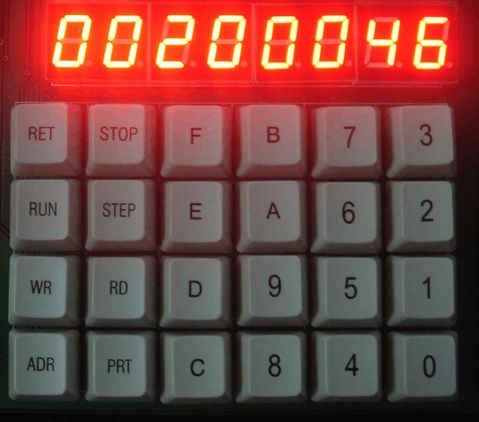

2.实验仪图片(整体)

实验仪图片(局部:开关S0-S23,24个,输入.发光二极管L0-L31,32个,输出) 实验仪图片(局部:键盘,输入.数码管,输出)

实验仪图片(局部:U1/U2,U3)

U1和U2采用XC2S50芯片,它们用于控制实验仪的工作方式,提供实验芯

5

片与存贮器和微程序存贮器的接口,控制实验计算机的运行,采集实验计算机的运行数据。(注意:掉电不丢失,厂家已写好)

U3为XC2S150-PQ208,它为Xilinx的15万门的FPGA.。用VHDL描述

的电路可通过并口线下载到U3中.(注意:掉电丢失,每次关机后要重新下载)

实验仪图片(局部:串口线,下载程序到存贮器,32Kx16.下载微程序到微程序

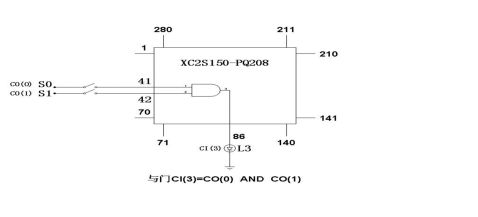

存贮器,1Kx32)3.数字逻辑基本实验实例(逻辑与门)

4、引脚配置文件ccc.ucf

#NET "clk " LOC = "P31";#号为注释

#NET "clr" LOC = "P41";

NET "CO<1>" LOC = "P42";

NET "CO<0>" LOC = "P41";

#NET "CI<9>" LOC = "P111";

6

#NET "CI<8>" LOC = "P110";

NET "CI<7>" LOC = "P90";

NET "CI<6>" LOC = "P89";

NET "CI<5>" LOC = "P88";

NET "CI<4>" LOC = "P87";

NET "CI<3>" LOC = "P86";

#NET "CI<2>" LOC = "P83";

#NET "CI<1>" LOC = "P82";

#NET "CI<0>" LOC = "P81";

5、逻辑与门的VHDL描述

-- 库引用说明

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; entity dec is --实体说明

Port (

signal CO :in std_logic_vector(0 to 1); signal CI :out std_logic_vector(3 to 7) );

end dec;

architecture Behavioral of dec is --构造体说明 7

begin

process(co)

begin

ci(3)<=co(1) and co(0); ci(4)<=co(1) or co(0); ci(5)<=co(1) nand co(0); ci(6)<=co(1) nor co(0); ci(7)<=co(1) xor co(0);

end process;

end Behavioral;

2、电路生成与下载步骤

找到桌面上的图标

D:\ks\hardware\computer

mybit

选择“下一步”,设置下载芯片参数

选择“下一步”,如果要建立新的VHDL文件,则选择“New Source…”。 如果要加载已经存在的文件,继续选择“下一步”。

选择“Add Source…”,加载已经存在的文件。

,启动.建立一个新工程

到要加载的CPU8B.VHD文件,“打开”,出现下面的窗口后,选择VHDL Design File, OK

选择“Add Source…”,加载UCF文件。

8

两个文件全部加载成功后,选择“下一步”

图列出了当前工程的信息,点击“完成”。

GCLK处理方法

XC2S150有4个全局CLK(GCLK),在综合时,如使用某些port线作时钟信号,它会把这些线用GCLK来实现,以后在实现布线时这与引脚冲突,引起错误。故必须对GCLK进行限定。本实验仪中,使用一个GCLK,它的名字为CLKG。如不使用它时,可在引脚锁定文件(*.UCF)中注释掉CLKG(在该行前加#)。这时,可定义为0个GCLK。如果使用CLKG,则定义一个GCLK。

定义GCLK的方法如下:

1)在Edit中,点击Preferences,选中Process选项卡,把Property Display设为Advanced。

2)在Process for Source窗口中,右键点击Synthesize-XST, 在Process Properties对话框内选中Xilinx Specific Options,

把Number of Clock Buffers置为1。

下载方式选择

接着是下载方式的选择,本实验仪提供2种下载方式的选择,JTAG与Slave Serial方式。

它与硬件下载线有关,如配的为Slave Serial下载线,则必须选择Slave Serial方式。

9

在Process for Source窗口中,右键点击Generate Programming File,

在Process Properties对话框中选择Startup Options选项卡,

有FPGA Start-Up Clock选项,选择CCLK则下载方式为Slave Serial方式,

选择JTAG Clock即为JTAG下载方式,也就是Boundary Scan。 在设定好下载方式以后,可以生成下载目标文件(*.bit),

双击Generate Programming File,依次进行Synthesize、

Implement Design和Generate Programming File等操作。

若在这几行前出现绿色的勾,表明没有错误,正常生成了

bit文件,若出现红色的叉,则说明出现严重错误,要根据

错误提示修改程序及设置。

电路生成结束,CPU8B.VHD+CPU8B.UCF→实体名.bit。下面的软件实现电路的下载

找到桌面上的图标,启动

选择下载配置

加载下载文件

3、汇编语言源程序的编辑、编译

找到桌面上的图标,启动

加载指令定义文件CPU8B.DEF

10

检查指令定义文件的合法性

检查指令定义文件通过

如果检查指令定义文件有问题,选择“改变参数”进行设置,见下页

建立一个新的汇编语言源文件或加载存在的文件TEST.ASM

检查语法

检查语法通过

在开始电路下载之前,必须保证:

1. 打开实验仪电源开关.

2. 找到桌面上的图标,启动.

3.注意该程序只能启动它的一个实例,否则联机通信行失败.

加载下载文件CPU8B.BIT

注意,U3芯片掉电丢失,电路下载后不要关闭实验仪器电源开关,否则要重新下载。

在开始调试之前,必须保证:

1.打开实验仪电源开关.

2.确保电路文件CPU8B.BIT已经下载到实验仪器的U3芯片.

3.确保目标文件TEST.S19已经生成.

4.找到桌面上的图标,启动.

5.注意该程序只能启动它的一个实例,

否则联机通信行失败.

设置串行口参数

11

选择工具栏”系统”按钮设置试验模式

按上页图示设置完毕后,先不加载文件,点击”确定”,会依此出现下面5个窗

再次选择工具栏”系统”按钮设置试验模式,加载三个文件.下图是加载显示配置文件

下图是加载微程序目标文件,在文件类型中选择All Files(*.*)才能找到CPU8B.M19文件

下图是加载程序目标文件

下图是加载程序目标文件

三个文件加载完毕后,点击“确定”。

等待程序和微程序目标码下载完毕

蓝色部分的11个字节是程序目标码

下图是微程序目标码

执行程序,有两种方式

1.在微机上执行(点击工具栏运行按钮)

运行结束,确定.刷新存储器

刷新存储器后,把下面窗口的滚动条移动到最上方,可看到在第10行地址为0020的单元内存放着12+34的结果46.第1行到第9行,第11行到第13行是程序机器码

运行结束,看到结果后,复位,否则不能再次运行.

五、编程与调试程序方法

12

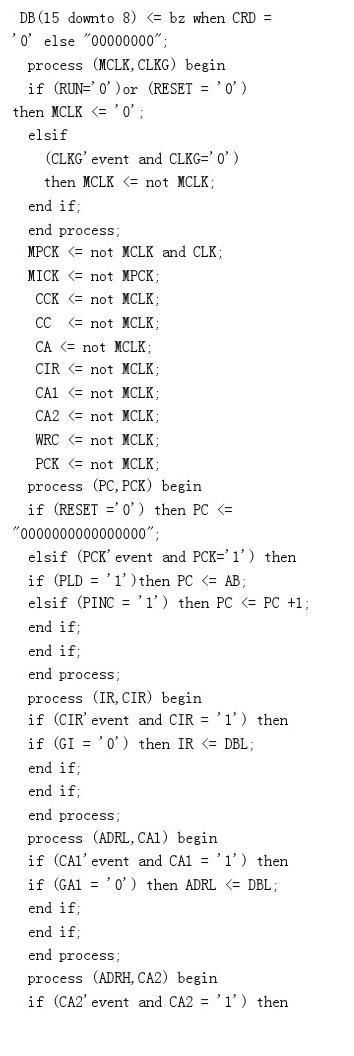

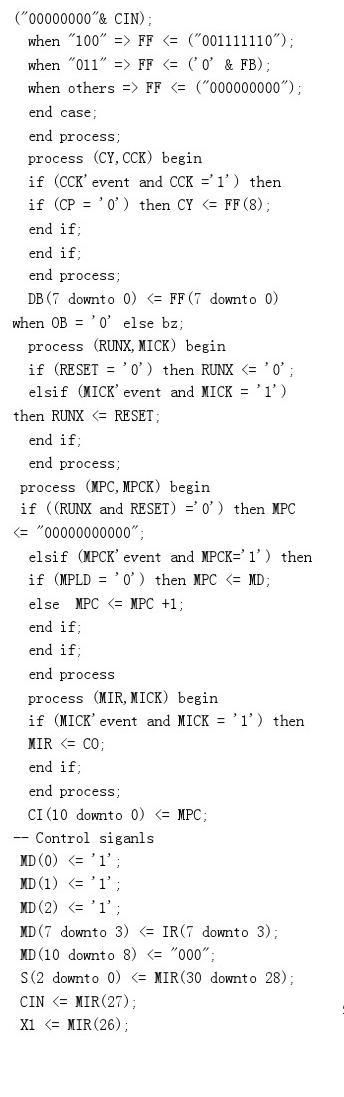

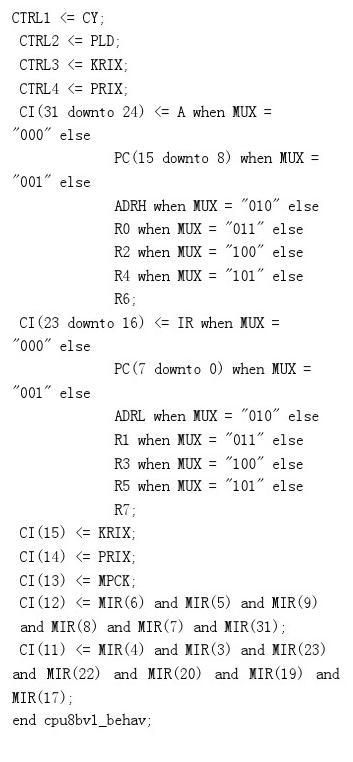

CPU8B.VHD的内容如下

Library IEEE;

use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity cpu8bv1 is Port (

DB:inout std_logic_vector(15 downto 0); MUX: in std_logic_vector(0 to 2);

CLKG,CLK,RESET,RUN: in std_logic;

CO: in std_logic_vector(31 downto 0);

MCLK: buffer std_logic;

PRIX,KRIX:in std_logic );

end cpu8bv1;

architecture cpu8bv1_behav of cpu8bv1 is

signal PC:std_logic_vector(15 downto 0);

signal A,ACT,TMP,IR,ADRL,ADRH,DBL:

std_logic_vector(7 downto 0);

signal R0,R1,R2,R3,R4,R5,R6,R7,ROUT,FB:

std_logic_vector(7 downto 0);

signal FF:std_logic_vector(8 downto 0);

signal MIR:std_logic_vector(31 downto 0); signal CC,CA,CG,SL,SR,X0,X1,CT,GT,MXB,ZD, COUT,CIN:std_logic;

signal CP,CCK,CY,P0,P1,P2,RD,WRC,WRE,RA, RB,RC,OB:std_logic;

signal GI,CIR,CA1,CA2,GA1,GA2,PINC,PCK, PLD,PRST,MXA1:std_logic;

signal MCLR,MPCK,MPINC,MPLD,MICK, RUNX:std_logic;

signal S,PL:std_logic_vector(2 downto 0); constant bz: std_logic_vector: ="ZZZZZZZZ";

constant wz: std_logic_vector: ="ZZZZZZZZZZZZZZZZ";

constant hz: std_logic_vector:= "ZZZZZZZZZZZZZZZZZZZZZZZZ";

begin

DBL <= DB(7 downto 0);

if (GA2 = '0') then ADRH <= DBL; end if; end if;

end process;

AB <= PC when (MXA1 = '0') else (ADRH & ADRL) when (MXA1 = '1') else

wz;

process (A,CA) begin

if (CA'event and CA = '1') then

if (X1 = '1') and (X0 = '1') then A

<= DBL;

elsif (X1 ='1') and (X0 = '0') then A

end if;

end if;

end process;

or A(3) or A(2) or A(1) or A(0));

process (ACT,CC) begin

if (CC'event and CC = '1') then

if (CG = '0') then ACT <= A;

end if;

end if;

end process;

process (TMP,CT) begin

if (CT'event and CT = '1') then

if (GT = '0') then TMP <= DBL;

end if;

end if;

end process;

process (R0,WRC) begin

if (WRC'event and WRC = '1') then

if (WRE = '0') then

if (RA = '0') and (RB = '0') and

(RC = '0') then R0 <= DBL;

end if;

end if;

end if;

end process;

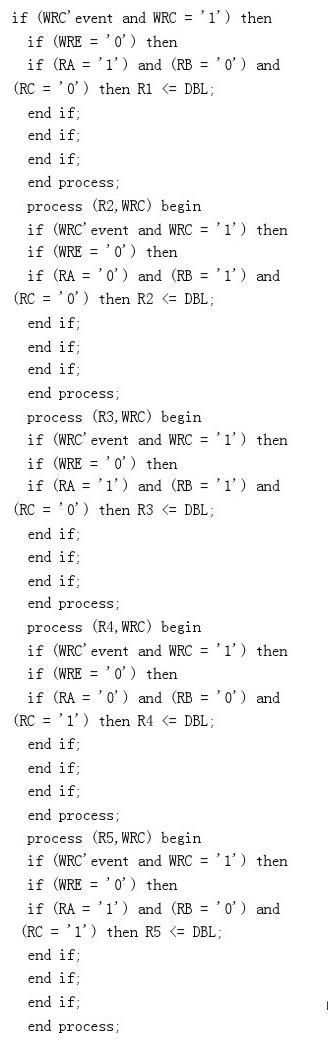

process (R1,WRC) begin

process (R6,WRC) begin if (WRC'event and WRC = '1') then if (WRE = '0') then if (RA = '0') and (RB = '1') and (RC = '1') then R6 <= DBL; end if; end if; end if; end process; process (R7,WRC) begin if (WRC'event and WRC = '1') then if (WRE = '0') then if (RA = '1') and (RB = '1') and (RC = '1') then R7 <= DBL; end if; end if; end if; end process; and (RC = '0') else (RC = '0') else (RC = '0') else (RC = '0') else (RC = '1') else (RC = '1') else (RC = '1') else R7 ; process (S)begin case S is + ("00000000"& CIN); - ("00000000"& CIN); when "010" => FF <= ('0'& ACT) +

("00000000"& CIN);

when "101" => FF <= ('0'& ACT) - X0 <= MIR(25); CG <= MIR(24); CP <= MIR(21); WRE <= MIR(18); OB <= MIR(16); GI <= MIR(15); GA1 <= MIR(14); GA2 <= MIR(13); PINC <= MIR(12); MPLD <= MIR(0); PL(2) <= MIR(11); PL(1) <= MIR(10); PL(0) <= MIR(9); MXA1 <= MIR(7);

PLD <= CY when (PL = "001")else '1' when (PL = "010")else

not KRIX when (PL = "011") else not PRIX when (PL = "100") else ZD when (PL = "101") else '0';

RA <= IR(0); RB <= IR(1); RC <= IR(2);

CWR <= MIR(2) or not MCLK or AB(15); CRD <= MIR(1) or not MCLK or AB(15);

IOW <= MIR(2) or not MCLK or not CLK or not AB(15) or not AB(1);

or not AB(0); --External watch

六、 结果及分析

1.设置启动地址0000.从键盘输入0000,按ADR键.数码管的左边4位表

示程序起始地址0000,最右边两位30是第一条指令的机器码.

2. 按RUN键,运行程序 3、STOP键,停止程序 4、按RET键,复位

16

5、从键盘输入0020,按ADR键观察结果.在内存的0020单元,存放着12+34的结果.

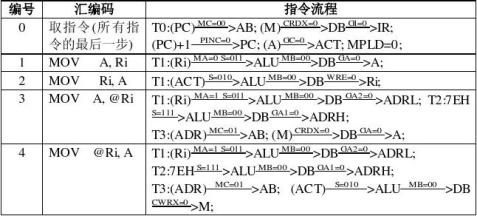

七、指令执行流程

1.模型计算机结构框图

17

2. 指令流程定义表

? T0为取指令微指令,所有指令的T0拍均相同。

? T1~T3为执行微指令。

? T0中的(A)→ACT为节省以后从累加器A输出数据的时间而增设的,它把A预先送到

暂存器ACT中,以后可直接传送到ALU中进行各种运算。

? 对于微程序控制的计算机指令流程与微指令一一对应。

18

19

20

八、收获、体会及建议

算机组成原理课程设计是在我们上完计算机组成原理课之后的硬件实践课程,是把组成原理课上的理论知识与实践相结合的过程。通过课程设计进一步加深对理论知识的理解和对计算机的工作过程的了解。

在这次课程设计过程中,我也遇到很多的问题,比如对VHDL语言的不熟悉,以及在调试过程中遇到的设备故障,但是最终通过不断的努力以及同学的帮助,我最终对那些晦涩难懂的程序又弄明白了,并且也对计算机程序指令有了更好了的了解,同时也让我对计算机的工作原理有了更深的理解。

通过两周的计算机组成原理课程设计,对计算机组成原理知识有了更加深刻的认识和理解,对计算机的工作流程有了更具体的了解和认识。诚挚的感谢指导林老师、赵老师等,老师悉心的教导使我得以通过这个组成原理的课设,从以前的理论上升到实践,真正做到学有所用,虽然在设计中我遇到了不少问题,而且往往一个小小的错误都会使我花很多的时间和精力去寻找和修正,不过做完后是发自内心的喜悦!经过了这次的设计使我学到了很多知识,给我今后在工作和学习上也提供了不少宝贵的经验.并且通过这次设计也使我也发现了自己在学习上的不足,主要是动手能力的不足,我会努力在以后的工作道路上继续充实自我,完善自我。

21