集成电路设计实验报告

目录

1 综合实验的任务与目的........................... 2

2 综合实验的内容和要求........................... 2

3设计方案对比和论证确定......................... 4

4设计实现过程................................... 5

5验证结果说明和结论............................. 7

6总结版图设计技巧............................... 9

7 参考文献..................................... 11

MOS集成运算放大器的版图设计

1 综合实验的任务与目的

集成电路设计综合实验是微电子学专业学科的实践性教学课程,其任务是向学生介绍集成电路软件设计的基本知识,基本的设计方法,学会使用专用软件进行集成电路设计,学习集成电路版图的设计及物理验证的一般方法技巧。本次集成电路设计综合实验要求学生完成对CMOS 集成运算放大器电路的版图设计及其物理验证。

2 综合实验的内容和要求

2.1 实验的内容

本次集成电路设计综合实验的内容为:CMOS 集成运算放大器的版图设计以及采用DIVA工具进行物理验证。版图设计的过程是:先进行电路分析,计算出各端点的电压及各管的电流,从而求出各管的W/L比,进而依据设计规则设计各管图形,进行布局、布线以及物理验证,最后完成整个版图设计。

2.1.1 目标电路及其性能要求

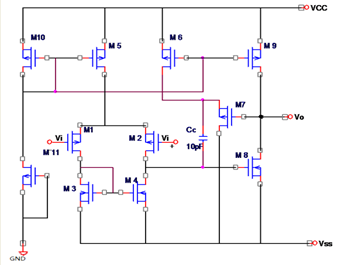

目标电路原理图如图1所示,为两级CMOS集成运算放大器,其中M1~M4构成有源负载的差分输入级;M5提供该级的工作电流;M8,M9构成共源放大电路,作为输出级;M7为源跟随器,作为增益为1的缓冲器,以克服补偿电容的前馈效应,并消除零点;M6提供M7的工作电流;M10,M11组成运放的偏置电路。

图1 CMOS集成运算放大器原理图

电路的性能要求:输出电压摆幅大于 ;最大转换速率为

;最大转换速率为 ;补偿电容Cc为10pF。

;补偿电容Cc为10pF。

2.1.2 工艺选择

本设计选择0.6um double metal double poly mixed signal technology 。

工艺信息描述:

工艺名称:6S06DPDM-CT

工艺尺寸:0.6um

多晶硅层数:2

铝的层数:2

电压类型: 3~5V

工艺参数: ,

, ,

, ,

, ,

, ,

, 。

。

假定 时,晶体管进入饱和工作状态。

时,晶体管进入饱和工作状态。

2.1.3 版图设计的一般方法和技巧

实际电路和原理图毕竟有所差别,各种非理想因素会影响电路的性能,使之偏离设计目标。因此,我们先要了解实际电路中各种非理想因素存在的原因,以及它对电路造成的影响。然后,同时从仿真和版图两个方面入手来解决这个问题。一方面,在电路设计中建立对应的模型,使原理电路更接近实际电路,从而使仿真和测试结果吻合。另一方面,画版图时使用适当的技巧,通过合理的布局、布线减小非理想因素对电路的影响。

2.2 实验要求

l 由学生独立设计、操作完成实验;要求学生掌握版图设计概念、方法、技巧,了解软件设计平台使用方法,并培养独立实验、创新能力。

l 掌握集成电路性能与版图布局布线之间的关系,能够合理进行版图规划。

l 掌握集成电路版图设计规则的含义以及消除或减小寄生效应的措施,能够正确设计集成电路版图,学会版图录入和版图设计规则检查(DRC)软件的使用。

3设计方案对比和论证确定

3.1设计方案

3.1.1.方案一

基础上既不用担心版图出错,又不用担心各种距离尺寸问题。这种方案简单易上手,而且很快就做完了,除了系统上的错误之外就是正确的,但是这种方案在实际应用时非常不可取,因为大尺寸不仅制作困难,而且很费成本,所以不可取。大尺寸的版图。即所有的器件尺寸远远超过最小值,这样在电路连接正确的。

3.1.2方案二

小尺寸的版图。即所有的器件尺寸基本接近最小值或者最小值的倍数,基本符合设计规则,在设计版图时要时刻DRC,防止出错,这需要认真计算尺寸,用标尺时刻做好度量工作,因为一个地方出问题很可能要出大错,所以这种方案能够保证设计的版图最符合要求,而且有可能还可以付诸于实际应用,但是这种方案需要花很长时间来画版图,所以比较费时费力。

3.2论证确定

因为前期在电路仿真时遇到了很多麻烦,再加上自身水平有限,所以大部分时间花在了电路测试电路的搭建上,所以后来经过组员的讨论论证,再考虑时间比较紧的缘故,我们决定采用折衷的方法,即在尽量符合设计规则的前提下,尽最大可能把版图尺寸缩小,基本上是第一种。

4设计实现过程

4.1 前期准备

画版图之前应该向电路设计者了解MOS摆放的顺序及位置,了解版图的最终面积是多少。在电路当中哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组, 每组之间各自是如何分布在版图上的,要求的工作进度与自己预估的进度有哪些出入。

4.2 全局设计

这个布局图应该和功能框图或电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的任务是焊盘的布局。焊盘的安排要便于内部信号的连接要尽量节省芯片面积以减少制作成本。焊盘的布局还应该便于测试特别是晶上测试。

4.3 分层设计

按照电路功能划分整个电路对每个功能块进行再划分每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计设计者需要建立多个单元。这一步就是自上向下的设计。

4.4 版图的检查

Design Rules Checker 运行DRC,DRC 有识别能力能够进行复杂的识别工作在生成最终送交的图形之前进行检查。程序就按照规则检查文件运行发现错误时会在错误的地方做出标记并且做出解释。 Electrical Rules Checker 检查线路短路、线路开路和floating 结点。DRC 检查到短路错误后将错误提示局限在最短的连接通路上。Layout Versus Schematic LVS 比较IC 版图和原理图报告版图连接和原理图的不一致,并进行修改直到版图和电路图完全一致。

4.5 版图修改

Label 是否正确,label 所选的layer是否正确,Power & Ground 连接得有没有问题,得到的files 是否确实可靠,检查netlist 中器件类型的命名是否符合规范,认真研究design rule,做好DRC 改错。看给出的报告有没有offgird结点多不多多的话就有断路的地方少的话就有短路的地方对照原理图看有没有连错线。

4.6 寄生与仿真

在实际电路的制作过程中会产生寄生参数它们分别为寄生电容、寄生电感和寄生电阻。

4.7 版图完成

后端数据接口处理确认芯片版图的设计和尺寸落实相关Foundry 的流片计划确认设计数据GDSII 文件大小。

5验证结果说明和结论

5.1测量输出电压范围

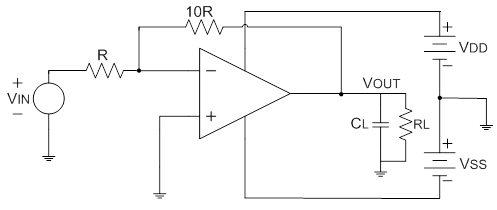

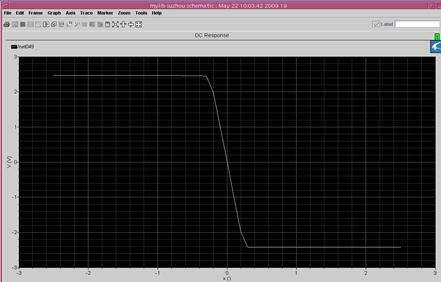

在单位增益结构中,传输曲线的线性收到ICMR限制。若采用高增益结构,传输曲线的线性部分与放大器输出电压摆幅一致,图2为反相增益为10的结构,通过RL的电流会对输出电压摆幅产生很大的影响,要注意对其的选取,这里我们选取RL=50K ,R=60K

,R=60K .图3为输出电压范围

.图3为输出电压范围

图2 测量输出电压范围的原理图

图3 输出电压的范围

5.2 运放转换速率和建立时间分析

转换速率是指输出端电压变化的极限,它由所能提供的对电容充放电的最大电流决定。一般来说,摆率不受输出级限制,而是由第一级的源/漏电流容量决定。建立时间是运算放大器受到小信号激励时输出达到稳定值(在预定的容差范围内)所需的时间。较长的建立时间意味着模拟信号处理速率将降低。

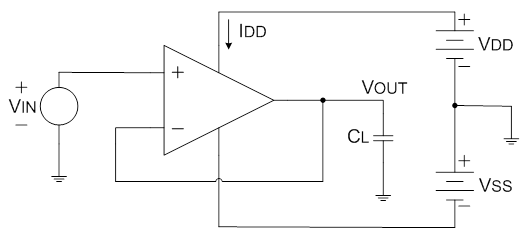

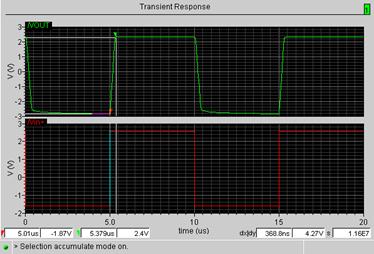

为了测量转换速率和建立时间,将运算放大器输出端与反相输入端相连,如图4所示,输出端接10pF电容,同相输入端加高、低电平分别为+3V和-3V,周期为10µs无时间延迟的方波脉冲。因为单位增益结构的反馈最大,从而导致最大的环路增益,所以能用做最坏情况测量,因此采用这种结构来测量转换速率和建立时间。得到的仿真图如5。由图5可以看出,建立时间约为0.8µs,在图中波形的上升或下降期间,由波形的斜率可以确定摆率。经计算得,上升沿的转换速率SR+为45 V/us,下降沿的转换速率SR-为45 V/us。

图4 摆率和建立时间的测量方法

图5 摆率与建立时间

5.3 版图验证

5.3.1 DRC验证

5.3.2 LVS验证

6总结版图设计技巧

通过合理的布局布线减小非理想因素对电路的影响,以下给出几条基本的布局原理:

①合理分布子电路:尽量将相关的模块放在一起,这样可以减小布线的复杂性,降低走线的长度。

②对称性:画版图时既要注意器件自身大小、位置的对称性,还要考虑他们周围环境的对称性。

③数模分开:数字电路、模拟电路应该尽量分开。最简单的方法是通过增大他们之间的距离来减弱衬底的耦合效应。

④高低频分开:工作在高频的射频电路和工作在较低频率的模拟电路尽量分开。

⑤电源和地分开:不同类型的电路各自使用独立的电源和地。

7 参考文献

[1] [美]毕查德.拉扎维. 模拟CMOS集成电路设计[M].西安:西安交通大学出版社2011.

[2]王志功.集成电路设计2009.

[3] [美] Christopher Saint,.集成电路版图设计,北京:清华大学出版社.2005.

[4] 曾庆贵.集成电路版图设计2008.

第二篇:集成电路设计实验报告