EDA实验报告书

第二篇:EDA实验报告(四位全加器的实现)

实验一 四位全加器的实现

一、 实验目的

1、掌握Quartus9.0图形编辑输入法

2、掌握Quartus环境下文件的编译、仿真及下载方法

3、了解VHDL语言的设计流程

4、掌握quartus环境下VHDL的使用方法

二、 实验内容

1、用图形/原理图法实现4位全加器。

2、用VHDL语言实现4位全加器,必须使用元件例化。

3、仿真并通过。

3、下载到实验板,并验收

三、 实验步骤

1、 图形编辑发设计4位加法器

(1) 新建图形文件,设计一位全加器,逻辑电路图如下图(图1-1)所示。

图1-1

(2) 将设计好的一位全加器进行例化,操作为fileàCreate/UpdateàCreate symbol files for currentfile,完成此操作后会在元器件符号表里找到刚刚做好的一位全加器。

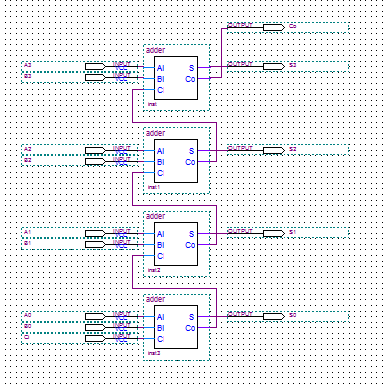

(3) 再新建一个图形文件,用四个已经做好的一位全加器级联成一个四位全加器,其逻辑原理图如图1-2所示。编辑好后保存文件,在文件列表里找到该文件,右键àSet as Top-level Entity,将其设置为顶层文件,点击编译按钮就行编译。

图1-2

(4) 新建波形文件,赋予每个输入端口某种输入信号,保存波形文件,进行功能仿真,观察输出端波形与输入信号关系是否正确。若不正确,查找问题所在并解决问题;若正确,则进行管脚分配,分配完毕后再编译一次使分配生效,连接DE2开发板到电脑,将文件下载到开发板进行验证。

2、 用VHDL语言设计4位加法器

(1) 新建一个VHDL源文件,文件名为adder1.vhd,使用VHDL实现一位全加器,其VHDL代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY adde1r IS

PORT(A,B,Ci:IN STD_LOGIC;

S,Co:OUT STD_LOGIC);

END adder1;

ARCHITECTURE qadder OF adder1 IS

BEGIN

PROCESS(A,B,Ci)

VARIABLE n1,n2,n3:STD_LOGIC;

BEGIN

n1:=A AND B;

n2:=A XOR B;

n3:=Ci AND n2;

Co<=n3 OR n1;

S<=n2 XOR Ci;

END PROCESS;

END qadder;

(2) 再新建一个VHDL源文件,命名为adder4.vhd,在这里将adder一位全加器例化并使用它,做成四位全加器,代码如下:

library ieee;

use ieee.std_logic_1164.all;

entity adder4 is

port(A,B:in std_logic_vector(3 downto 0);

S:out std_logic_vector(3 downto 0);

Co:out std_logic;

Ci:in std_logic);

end adder4;

architecture adder_4 of adder4 is

component adder

port(

A:in std_logic;

B:in std_logic;

Ci:in std_logic;

Co:out std_logic;

S:out std_logic);

end component;

signal c1,c2,c3:std_logic;

begin

u1:adder port map(A(0),B(0),Ci,c1,S(0));

u2:adder port map(A(1),B(1),c1,c2,S(1));

u3:adder port map(A(2),B(2),c2,c3,S(2));

u4:adder port map(A(3),B(3),c3,Co,S(3));

end adder_4;

(3) 保存文件后将adder4设置为顶层文件并编译,编译通过后按照与图形编辑发一样的仿真、管脚分配方式进行操作,最后下载到开发板验证

四、 实验现象

两种方式实现的四位加法器下载到DE2开发板后都可正常工作,其中使用SW0作为低位的进位,SW4~1作为数据B,SW8~5作为数据A,LDG3~0作为输出的结果,LEDG4作为输出的进位。当SW4~1闭合 SW8~5和SW0断开时,只有LEDG3~0这四个灯亮;当SW8~0全闭合时,LEDG4~0灯全亮。

中国石油大学(华东)

实 验 报 告

课题名称 EDA设计

实验项目名称 实验一四位全加器的设计

专业 计算机科学与技术

姓名 孙文吉