EDA实验报告

姓名:

学号:

班级:

实验1 4选1数据选择器的设计

一、实验目的

1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材

1.EDA开发软件 一套

2.微机 一台

3.实验开发系统 一台

4.打印机 一台

三、实验说明

本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。学会管脚锁定以及编程下载的方法等。

四、实验要求

1.完成4选1数据选择器的原理图输入并进行编译;

2.对设计的电路进行仿真验证;

3.编程下载并在实验开发系统上验证设计结果。

五、实验结果

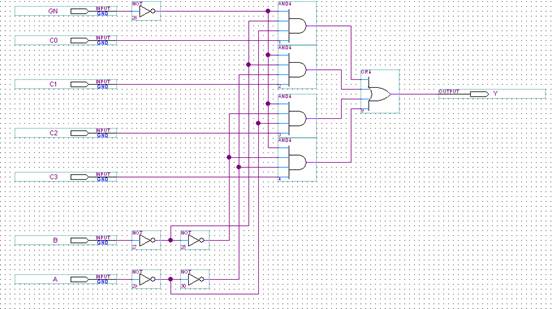

4选1数据选择器的原理图:

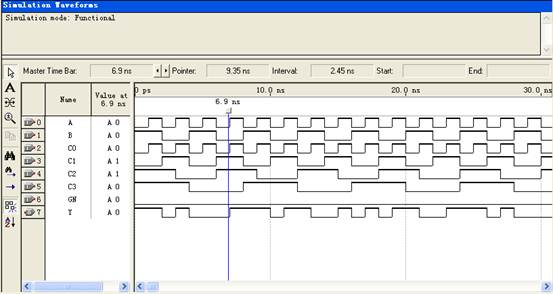

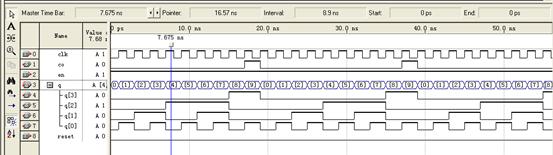

仿真波形图:

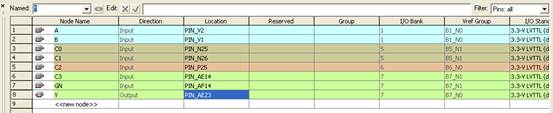

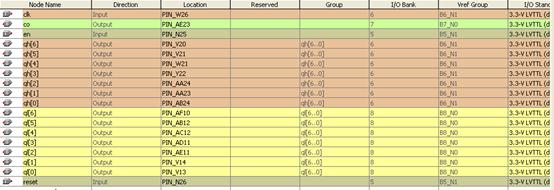

管脚分配:

实验2 四位比较器

一、实验目的

1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材

1.EDA开发软件 一套

2.微机 一台

3.实验开发系统 一台

4.打印机 一台

5.其它器件与材料 若干

三、实验说明

本实验实现两个4位二进制码的比较器,输入为两个4位二进制码 和

和 ,输出为M(A=B),G(A>B)和L(A<B)(如图所示)。用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

,输出为M(A=B),G(A>B)和L(A<B)(如图所示)。用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

四、实验要求

四、实验要求

1.用硬件描述语言编写四位二进制码

1.用硬件描述语言编写四位二进制码

比较器的源文件;

比较器的源文件;

2.对设计进行仿真验证;

2.对设计进行仿真验证;

3.编程下载并在实验开发系统上进行

3.编程下载并在实验开发系统上进行

硬件验证。

硬件验证。

四位比较器功能框图

五、实验结果

四位比较器VHDL源文件:

library ieee;

use ieee.std_logic_1164.all;

entity comp4 is

port( A3,A2,A1,A0: in std_logic;

B3,B2,B1,B0: in std_logic;

G,M,L: out std_logic);

end comp4;

architecture behave of comp4 is

begin

p1: process(A3,A2,A1,A0,B3,B2,B1,B0)

variable comb1,comb2: std_logic_vector(3 downto 0);

begin

comb1:=A3&A2&A1&A0;

comb2:=B3&B2&B1&B0;

if(comb1>com2) then G<=’1’; M<=’0’; L<=’0’;

elsif(comb1<comb2) then M<=’1’; G<=’0’; L<=’0’;

else L<=’1’; G<=’0’; M<=’0’;

end if;

end process p1;

end behave;

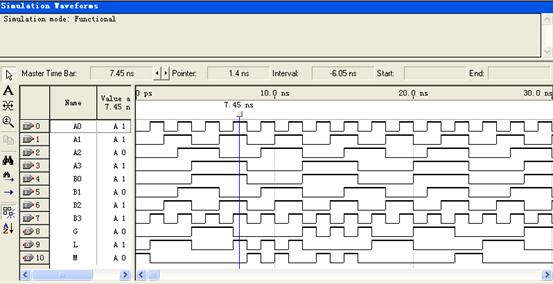

仿真波形图:

管脚分配:

试验3 并行加法器设计

一、试验目的

1.设计一个4位加法器。

2.体会用VHDL进行逻辑描述的优点。

3,熟悉层次化设计方法。

二、试验仪器与器材

1.EDA开发软件 一套

2.微机 一台

3.试验开发系统 一台

4.打印机 一台

5.其他器材和材料 若干

三、试验说明

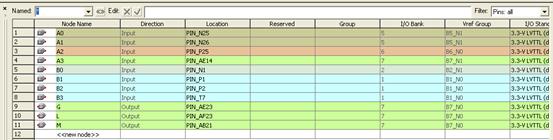

本试验实现一个4位二进制数加法器,其功能框图如图所示。试验时用高低电平开关作为输入,用数码管作为输出(或用发光二极管),管脚锁定可根据试验系统自行安排。

本试验实现一个4位二进制数加法器,其功能框图如图所示。试验时用高低电平开关作为输入,用数码管作为输出(或用发光二极管),管脚锁定可根据试验系统自行安排。

四、实验要求

1.用硬件描述语言编写4位二进制数全加器的源文件;

2.对设计文件进行编译;

3.仿真设计文件;

4.编程下载并进行试验验证。

五、试验结果

4位二进制全加器的源文件:

library ieee;

use ieee.std_logic_1164.all;

entity adder4 is

port(a,b: in std_logic_vector(3 downto 0);

cin: in std_logic_vector(3 downto 0);

sum: out std_logic_vector(3 downto 0);

count: out std_logic);

end adder4;

architecture behavioral of adder4 is

begin

p1:process(a,b,cin)

variable vsum: std_logic_vector(3 downto 0);

variable carry: std_logic;

begin

carry:=cin;

for i in 0 to 3 loop

vsum(i):=(a(i) xor b(i)) xor carry;

carry:=(a(i) and b(i)) or (carry and (a(i) or b(i)));

end loop;

sum<=vsum;

count<=carry;

end process p1;

end behavioral;

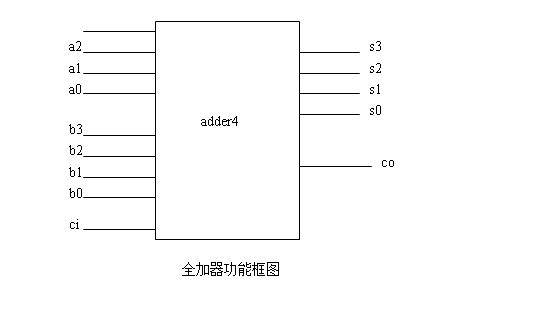

仿真波形图:

管脚分配:

实验4 计数器设计

一、实验目的

计数器是实际中最为常用的时序电路模块之一,本实验的主要目的是掌握使用HDL描述计数器类型模块的基本方法。

二、实验仪器与器材

1.EDA开发软件 一套

2.微机 一台

3.实验开发系统 一台

4.打印机 一台

5.其他器材与材料 若干

三、实验说明

计数器是数字电路系统中最重要的功能模块之一,设计时可以采用原理图或HDL语言完成。下载验证时的计数时钟可选连续或单脉冲,并用数码管显示计数值。

四、实验要求

1.设计一个带有计数允许输入端、复位输入端和进位输入端的十进制计数器。

2.编制仿真测试文件,并进行功能仿真。

3.下载并验证计数器功能。

4.为上述设计建立元件符号。

5.在上述基础上分别设计按8421BCD码和二进制计数的100进制同步计数器。

五、实验结果

十进制计数器程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter10 is

port(en,reset,clk:in std_logic;

q:buffer std_logic_vector(3 downto 0);

co:out std_logic);

end counter10;

architecture behav of counter10 is

begin

process(clk,en)

begin

if clk'event and clk='1' then

if reset='1' then q<="0000";

elsif en='1' then

if q<"1001" then q<=q+'1';

else q<="0000";

end if;

end if;

end if;

end process;

co<='1' when q="1001" else '0';

end behav;

仿真波形图:

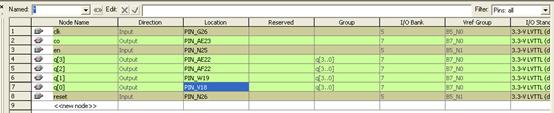

管脚分配:

4_7译码器程序:

library ieee;

use ieee.std_logic_1164.all;

entity decoder4_7 is

port( insign: in std_logic_vector (3 downto 0);

outsign: out std_logic_vector (6 downto 0));

end decoder4_7;

architecture behave of decoder4_7 is

begin

process(insign)

begin

case insign is

when"0000"=>outsign<="0000001";

when "0001"=>outsign<="1001111";

when "0010"=>outsign<="0010010";

when "0011"=>outsign<="0000110";

when "0100"=>outsign<="1001100";

when "0101"=>outsign<="0100100";

when "0110"=>outsign<="1100000";

when "0111"=>outsign<="0001111";

when "1000"=>outsign<="0000000";

when "1001"=>outsign<="0001100";

when OTHERS=>outsign<="1111111";

end case;

end process;

end behave ;

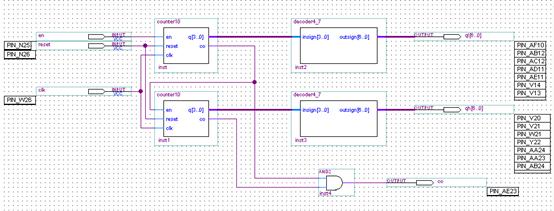

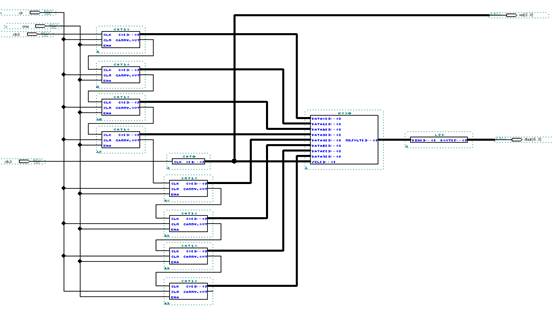

100进制计数器原理图:

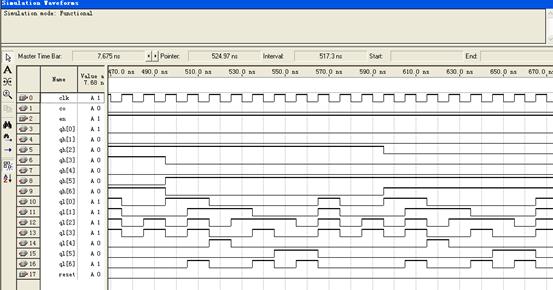

仿真波形图:

管脚分配:

实验5 巴克码发生器

一、实验目的

1.实现一个在通信领域中经常使用的巴克码发生器。

2.掌握用大规模可编程逻辑器件实现时序电路的方法。

二、实验仪器与器材

1.EDA开发软件 一套

2.微机 一台

3.实验开发系统 一台

4.打印机 一台

5.其它器件与材料 若干

三、实验说明

巴克码发生器在数据通信、雷达和遥控领域有相当广泛的应用。它能自动产生周期性的序列码。本实验要求产生的序列码信号为(1110010),可以用寄存器或同步时序电路实现。为了能够通过实验开发系统验证试验结果,可以使用两个输入端,其中一个输出端同时输出巴克码,另一个输出端输出节拍。巴克码发生器的功能框图如图所示。

四、实验要求

1.写出全部设计文件。

2.编写测试向量,进行功能仿真。

3.下载并用实验板验证。

五、实验结果

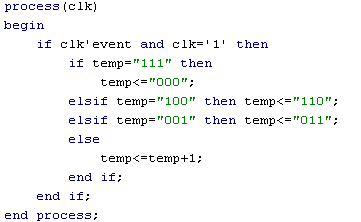

巴克码发生器程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity back is

port(clk,reset:in std_logic;

dout1,dout2:out std_logic);

end back;

architecture behave of back is

signal count7:integer range 0 to 6;

begin

process(clk,reset)

begin

if reset='1' then count7<=0;

elsif clk'event and clk='1' then

if count7<6 then

count7<=count7+1;

else count7<=0;

end if;

end if;

dout2<=clk;

end process;

process(count7)

begin

case count7 is

when 0=>dout1<='1';

when 1=>dout1<='1';

when 2=>dout1<='1';

when 3=>dout1<='0';

when 4=>dout1<='0';

when 5=>dout1<='1';

when 6=>dout1<='0';

when others=>dout1<='0';

end case;

end process;

end behave;

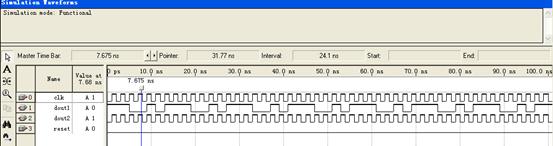

仿真波形图:

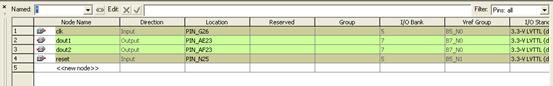

管脚分配:

第二篇:EDA实验报告 实验五:计数器

EDA实验报告| 实验五:计数器

一.实验目的:

1 进一步学习层次设计法设计电路

2 进一步学习混合原理图及程序法设计法

二.实验内容

1 设计8位十进制计数器

2 要求用CLK5时钟源做计计数时钟输入,计数结果用实验板上8个数码管显示

3 计数器要求有清零端(CLK,用SW1控制)和使能端(ENG,用SW2控制),都是高电平有效,用实验板SW1,SW2设置

三.实验现象

数码依次按十进制增1计数。上拨SW1则清零,下拨SW2停止计数。改变CLK5的频率可以观看计数快慢。

四.连线与跳线

1 数码显示数据、控制及频率源的PIN脚对应关系见实验一

2 SW1,SW2与芯片PIN脚对应关系:SW1-PIN30,SW2-PIN35

3 最高位计数器进位输出可自行设计,可以引出,也可以不引出

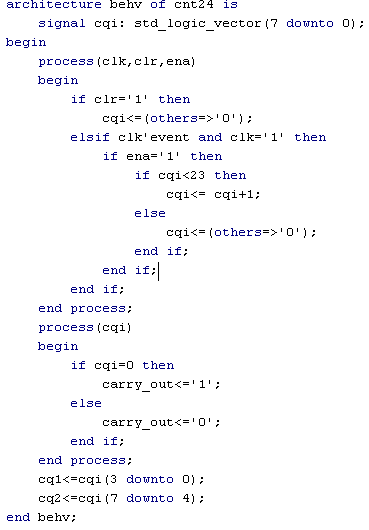

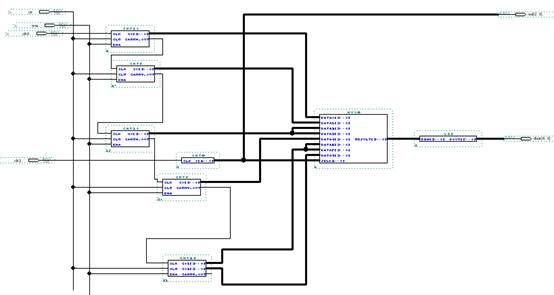

五.实验内容和步骤(整个设计采用层次法,包括以下文件)

1. CNT8.VHD(产生三个译码器的输入信号,以控制哪个数码管工作);

2. MUX8.VHD (2选1多路复用电路,用于顺序输入2位数码管的显示数据);

3. LED.VHD(数据与7段数码管显示转换电路);

4. cnt10.vhd (十进制计数器程序);

5. 形成顶层图形文件king8.gdf:

六.思考题(扩展以上方法实现时钟24hour-60miniter-60second)

6. 首先修改CNT8.VHD,使得只有六个LED灯循环(最左两盏表示hour、正中间两盏表示miniter、最右两盏表示second):

7. cnt6.vhd (六进制计数器程序):

8. king8.gdf (二十四进制计数器程序,是用十六进制显示hour部分的):

9. 形成顶层图形文件king8.gdf:

七.实验心得:

好好作图,用手可以勾画出神奇的硬件世界;

进一步熟悉了混合原理图以及程序法设计,又学到了好东西。