北京科技大学计算机与通信工程学院

实 验 报 告

实验名称: Cache控制器、简单模型机设计实验

学生姓名:

专 业:

班 级:

学 号:

指导教师:

实验成绩:

实验地点:

实验时间: 年 月 日

一、实验目的与实验要求

1、实验目的

(1) 掌握一个简单CPU 的组成原理;在掌握部件单元电路的基础上,进一步将其构造一台基本模型计算机;为其定义五条机器指令,编写相应的微程序,并上机调试。

(2) 掌握Cache 控制器的原理及其设计方法;熟悉FPGA应用设计及EDA 软件的使用;熟悉QuartusII软件的使用及FPGA应用设计。

2、实验要求

(1) 用画图方式给出简单模型机实验接线图。利用5条机器指令编写程序,在简单模型机上运行,并观察执行过程和结果。更改指令,使其执行一次后能够停机。

(2)利用QuartusII软件中完成Cache控制器的设计,编译、仿真、下载并观察执行结果。

二、实验设备(环境)及要求

CM3+实验环境、QuartusⅡ8.0环境

三、实验内容与步骤

1、实验一

(1)实验原理

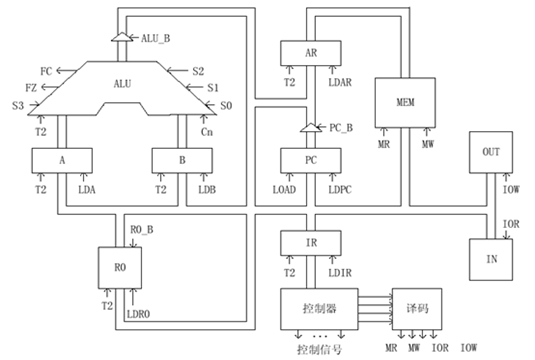

本实验要实现一个简单的CPU,并且在此CPU的基础上,继续构建一个简单的模型计算机。CPU由运算器(ALU)、微程序控制器(MC)、通用寄存器(R0),指令寄存器(IR)、程序计数器(PC)和地址寄存器(AR)组成。这个CPU在写入相应的微指令后,就具备了执行机器指令的功能,但是机器指令一般存放在主存当中,CPU必须和主存挂接后,才有实际的意义,所以还需要在该CPU的基础上增加一个主存和基本的输入输出部件,以构成一个简单的模型计算机。

PC_B为三态门的输出使能端,CLR连接至CON单元的总清端CLR,按下CLR按钮,将使PC清零,LDPC和T2相与后作为计数器的计数时钟,当LOAD为低时,计数时钟到来后将CPU内总线上的数据打入PC。 本模型机共有五条指令:IN(输入)、ADD(二进制加法)、OUT(输出)、JMP(无条件转移),HLT(停机),其指令格式如下表3.12所示。

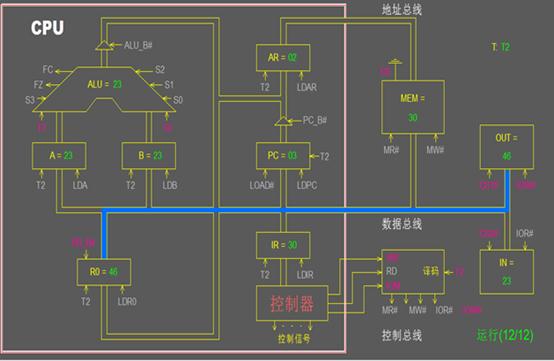

数据通路图

其中,JMP为双字节指令,其余均为单字节指令,********为addr对应的二进制地址码。微程序控制器实验的指令是通过手动给出的,现在要求CPU自动从存储器读取指令并执行。本实验在微程序控制器实验的基础上增加了三个部件即程序计数器PC,地址寄存器AR,存储器MEM。

当拟定“取指”微指令时,该微指令的判别测试字段为P<1>测试。由于“取指”微指令是所有微程序都使用的公用微指令,因此P<1>的测试结果出现多路分支。本机用指令寄存器的高6 位(IR7~IR2)作为测试条件,出现5路分支,占用5 个固定微地址单元,剩下的其它地方就可以一条微指令占用控制存储器一个微地址单元随意填写,微程序流程图上的单元地址为16进制。

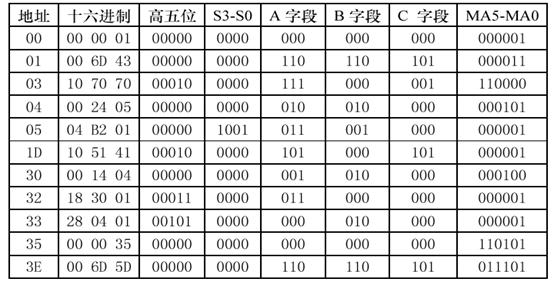

当全部微程序设计完毕后,应将每条微指令代码化,下表即为将图3.34的微程序流程图按微指令格式转化而成的“二进制微代码表”。

简单模型机微程序流程图

设计一段机器程序,要求从IN 单元读入一个数据,存于R0,将R0和自身相加,结果存于R0,再将R0的值送OUT单元显示。根据要求可以得到如下程序,地址和内容均为二进制数,地址内容助记符说明:

00000000 00100000 ; START: IN R0 从IN 单元读入数据送R0

00000001 00000000 ; ADD R0,R0 R0 和自身相加,结果送R0

00000010 00110000 ; OUT R0 R0 的值送OUT 单元显示

00000011 11100000 ; JMP START 跳转至00H 地址

00000100 00000000 ;

00000101 01010000 ; HLT停机

(2)实验步骤

①联机写入和校验

编写实验程序,将其导入到CM3+实验环境中,校验运行。

②按照下图将实验箱连线

③联机运行

利用软件环境里的简单模型机数据通路图。操作实验箱,观测指令的执行过程,并观测软件中地址总线、数据总线以及微指令显示和下位机是否一致。

2、实验二

(1)实验原理

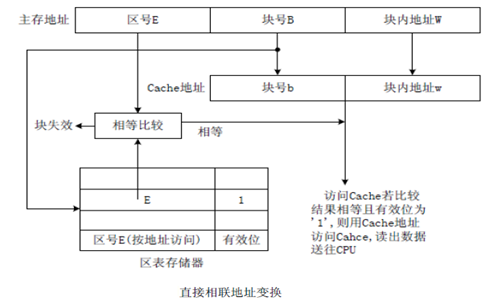

本实验采用的是直接方式,这种变换方式简单而直接,硬件实现很简单,访问速度也比较快,但是块的冲突率比较高。其主要原则是:主存中一块只能映象到Cache的一个特定的块中。 假设主存的块号为B,Cache的块号为b,则它们之间的映象关系可以表示为:b = B mod Cb其中,Cb是Cache的块容量。设主存的块容量为Mb,区容量为Me,则直接映象方法的关系如图3.19所示。把主存按Cache的大小分成区,一般主存容量为Cache容量的整数倍,主存每一个分区内的块数与Cache的总块数相等。直接映象方式只能把主存各个区中相对块号相同的那些块映象到Cache中同一块号的那个特定块中。例如,主存的块0只能映象到Cache 的块0中,主存的块1只能映象到Cache的块1中,同样,主存区1中的块Cb(在区1中的相对块号是0)也只能映象到Cache 的块0中。根据上面给出的地址映象规则,整个Cache 地址与主存地址的低位部分是完全相同的。

直接映象方式的地址变换过程如图所示,主存地址中的块号B 与Cache 地址中的块号b 是完全相同的。同样,主存地址中的块内地址W 与Cache 地址中的块内地址w 也是完全相同的,主存地址比Cache 地址长出来的部分称为区号E。

在程序执行过程中,当要访问Cache 时,为了实现主存块号到Cache 块号的变换,需要有一个存放主存区号的小容量存储器,这个存储器的容量与Cache 的块数相等,字长为主存地址中区号E 的长度,另外再加一个有效位。

在主存地址到Cache 地址的变换过程中,首先用主存地址中的块号去访问区号存储(按地址访问)。把读出来的区号与主存地址中的区号E 进行比较,根据比较结果和与区号在同一存储字中的有效位情况作出处理。如果区号比较结果相等,有效位为‘1’,则Cache 命中,表示要访问的那一块已经装入到Cache 中了,这时Cache 地址(与主存地址的低位部分完全相同)是正确的。用这个Cache 地址去访问Cache,把读出来的数据送往CPU。其他情况均为Cache 没有命中,或称为Cache 失效,表示要访问的那个块还没有装入到Cache 中,这时,要用主存地址去访问主存储器,把读出来的一个字送往CPU,同时,把包括被访问字在内的一块都从主存储器中读出来,送往Cache 的相应块。Cache 和CPU 以及存储器的连接如图3.21 所示,本实验要在FPGA 中实现Cache 及其地址变换逻辑(也叫Cache 控制器),采用直接相联地址变换,只考虑CPU 从Cache 读数据,不考虑CPU 写回数据的情况。

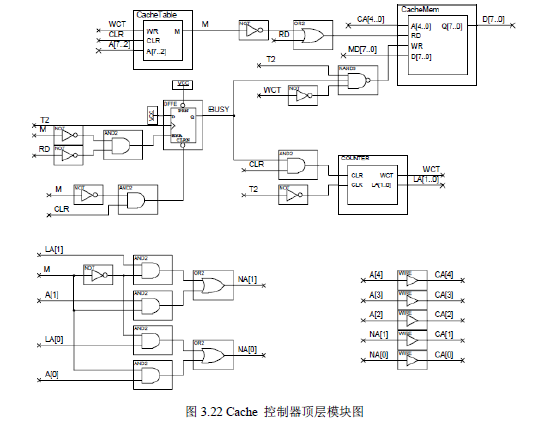

Cache 控制器顶层模块如图3.22 所示,主存地址为A7…A0,共8 位,区号E 取3 位,这样Cache 地址还剩5 位,所以Cache 容量为32 个单元,块号B 取3 位,那么Cache 分为8块,块内地址W 取2 位,则每块为4 个单元。图3.22 中,WCT 为写Cache 块表信号,CLR为系统总清零信号,A7…A0 为CPU 访问内存的地址,M 为Cache 失效信号,CA4…CA0 为Cache地址,MD7…MD0 为主存送Cache 的数据,D7…D0 为Cache 送CPU 数据,T2 为系统时钟,RD 为CPU 访问内存读信号,LA1 和LA0 为块内地址。

(2)主要步骤

①利用Quartus II软件完成对Cache控制器的设计,并且将其编译运行仿真。

②连接实验箱,并完成实验连线。

③将编译仿真成功的文件,下载到实验箱内,测试运行,并观察实验现象。

四:实验结果与分析

1、实验一

(1)停机指令文件

; //*************************************//

; // //

; // CPU与简单模型机实验指令文件 //

; // //

; // By TangDu CO.,LTD //

; // //

; //*************************************//

; //***** Start Of Main Memory Data *****//

$P 00 20 ; START: IN R0 从IN单元读入数据送R0

$P 01 00 ; ADD R0,R0 R0和自身相加,结果送R0

$P 02 30 ; OUT R0 R0的值送OUT单元显示

$P 03 E0 ; JMP START 跳转至00H地址

$P 04 05 ;

$P 05 50 ; HLT 停机

; //***** End Of Main Memory Data *****//

; //** Start Of MicroController Data **//

$M 00 000001 ; NOP

$M 01 006D43 ; PC->AR,PC加1

$M 03 107070 ; MEM->IR, P<1>

$M 04 002405 ; R0->B

$M 05 04B201 ; A加B->R0

$M 1D 105141 ; MEM->PC

$M 30 001404 ; R0->A

$M 32 183001 ; IN->R0

$M 33 280401 ; R0->OUT

$M 35 000035 ; NOP

$M 3C 006D5D ; PC->AR,PC加1

; //** End Of MicroController Data **//

(2)CM3+环境显示

2、实验二

(1)Cache控制器设计原理图及其仿真波形

(2)实验箱运行

五:结论(讨论)

1、实验结论

(1)通过更改指令,能够使其执行一次运行后停机,并且观察到来程序的执行过程和结果。掌握了简单CPU 的组成原理,并在此基础上构造出了简单的模型计算机,并且能够运行成功。

(2) 利用QuartusII软件完成了Cache控制器的设计,编译仿真通过,下载到了实验现象,进而掌握了Cache 控制器的基本原理及其设计方法。

2、讨论

此次实验比上次的实验连线更加复杂,在经历过上次连线失败后,我吸取了教训,并且在此次实验中一次就把线连接成功。在Cache 控制器的实验过程,我一直对实验原理不够理解,但是老师通过结合实验箱运行过程的讲解,帮我解决了我的疑问。希望自己在以后的实验过程中,可以加强预习;也建议老师以后可以多结合实验箱操作讲解,这样同学们理解起来比较直观、印象比较深刻。

六、教师评审