实验一 MaxplusⅡ软件的安装与使用

一、实验目的:

学习MaxplusⅡ软件的使用,包括软件安装及基本的使用流程。

本次实验是以半加器的原理图输入法设计为例,学习MaxplusⅡ软件的使用,体会用原理图输入法设计简单组合电路的方法和详细设计流程。掌握层次化设计的方法,并通过一位全加器的设计把握利用EDA软件进行原理图输入法进行电子线路设计的详细流程。为后续原理图的层次化设计打下基础。

本次实验不要求下载。

二、实验原理:

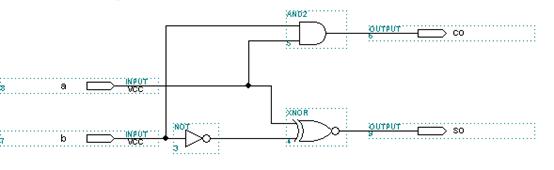

半加器可以通过调用基本的与、或、非门来实现。按照课本5.4节介绍的方法用原理图输入法设计一个半加器,然后将其封装成模块以备下次实验调用。

三、实验内容和步骤:

1、打开原理图编辑器,完成半加器的设计。

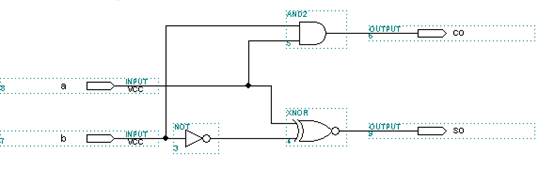

半加器原理图如下:

2、完成1位半加器的设计输入、目标器件选择、编译和仿真各步骤,详细的过程见教材5.4节相关内容。

仿真结果如下:

3、正确完成之后,选择File\create\Create Symbol file for current file,将文件变成一个包装好的单一元件模块待调用。

四、实验结果与总结:

实验二 用原理图输入法设计一位全加器

一、实验目的:

熟悉MaxplusⅡ软件的原理图输入法的层次化设计方法,并通过一位全加器的设计把握利用EDA软件进行原理图输入法进行电子线路层次化设计的详细流程。

本次实验要求进行下载验证。

二、实验原理:

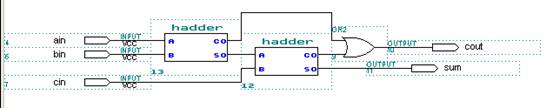

一位全加器可以由两个半加器构成。可以利用上次实验设计的半加器模块,完成本次全加器的设计。本次全加器原理图文件是顶层文件。

三、实验内容和步骤:

1、打开原理图编辑器,调用上次实验包装好的1位半加器可画以下1 位全加器:

保存并完全编译,进行仿真,结果如下:

2、引脚锁定并下载:

ain=> 对应实验箱上的

bin=> 对应实验箱上的

cin=> 对应实验箱上的

sun=> 对应实验箱上的

cout=> 对应实验箱上的

3、引脚锁定后再重新进行编译,连接实验箱并进行下载。详细下载步骤见书上相关内容。注意第一次下载时的一些设定。

四、实验结果与总结:

实验三 用原理图输入法设计较复杂数字系统

一、实验目的:

熟悉原理图输入法中74系列等宏功能模块的使用方法,掌握更复杂的原理图层次化设计技术和数字系统设计方法。利用74248芯片模块完成BCD-7段码译码显示电路的设计。

二、实验原理:

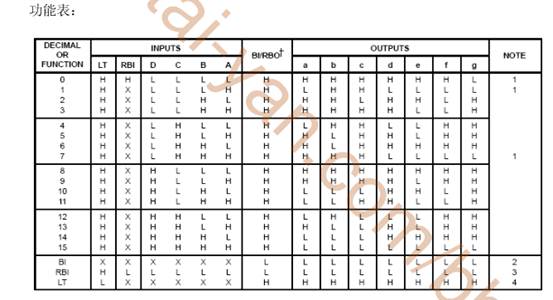

该实验用到了74248芯片,该芯片主要为共阴极数码管提供七段码。74248芯片真值表及对应显示符号如下所示:L为低电平,H为高电平,X为任意态(H或L)。

BI/RBO灭灯输入:做输入端使用时,若BI为0,则无论其他输入端是什么电平,所有各段输出a——g均为0,字型熄灭。

LT试灯输入:当LT为0时,BI /RBO是输出端,且RBO=1,此时无论其他输入端是什么电平,所有各段输出a——g均为1,显示字型8。该输入端常用于检查74248本身及数码管的好坏。

RBI动态灭零输入:当LT=1时,若RBI=0,则当输入代码为0000时,各段输出均为低电平,对应的字型0熄灭,故成灭零端。此时BI/RBO时输出端,且RBO=0。当输入为其他代码时各段输出能正常显示对应字型。

LT=1且RBI=0,DCBA=0000时,RBO=0

LT=0或者LT=1且RBI=1,则RBO=0

因此,对输入的0000,要想正常显示,要求LT和RBO都为1,而对其他代码,只要求LT=1即可。

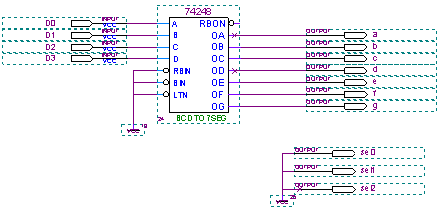

在BCD-7段译码器原理图中,74248芯片的RBON脚(数码管的H脚即小数点)悬空没有用,故本实验所显示的符号不含有小数点。另外由于试验箱上数码管有8个(SM1-SM8),sel2-sel0作为选择数码管的位选信号。

三、实验内容与步骤:

1、打开原理图编辑器,完成BCD-七段译码显示电路的设计。包括原理图输入、编译、综合、适配、仿真。

实验原理图如下:

仿真结果如下:

2、引脚锁定并下载:

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

。。。。。。。。

引脚锁定后再重新进行编译,连接实验箱并进行下载。

四、实验结果与总结:

实验四 用波形图输入法设计简单数字电路

一、实验目的:

掌握MaxplusⅡ软件的波形图输入法设计方法,并通过一位热码循环电路的设计把握利用EDA软件进行波形图输入法设计电子线路的详细流程。

二、实验原理:

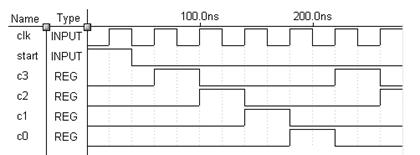

本次实验要设计一个一位热码循环电路,原理:clk为时钟信号,start为编码有效信号,低电平时有效,c3——c0为四个输出信号。当start信号有效时, c3-c0从1000-0100-0010-0001-1000循环显示,保持一位热码循环显示,如下图所示:

图1

三、实验内容与步骤:

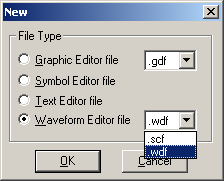

1、选择MAX+plus II的菜单“File”中“New”对话框如下图2所示:选择“Waveform Editor file”。注意要选“WDF”文件类型。

图2 图3

2、选择菜单“Node”中的 “Insert Node….”选项,弹出“Insert Node”对话框,如图3所示。在接点名中填入需要增加的节点,选择节点类型。输完所有的节点,就可以把波形输进去了。

注意:c3-c0引脚的变化与时钟的上升沿是严格一致的,不能有延迟。参照图1输入好相关波形并存盘。具体步骤课参看教材6.3节相关内容。

3、完成项目的编译与仿真,仿真结果如下:

4、仿真通过后进行引脚锁定。引脚锁定信息如下:

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

。。。。。。。。

引脚锁定后再重新进行编译,连接实验箱并进行下载。

四、实验结果与总结:

实验五 用VHDL输入法设计七段译码器电路

一、实验目的:

熟悉VHDL程序的一般结构以及用VHDL语言设计组合逻辑电路的一般方法。要求用VHDL语言设计一个7段译码器,能实现四位二进制数到对应的十六进制数的译码功能,并完成设计输入、编译、仿真、硬件测试等过程。

二、实验原理:

VHDL程序通常包含库、程序包、实体、结构体、配置5个组成部分,其中实体和结构体是VHDL程序中不可缺少的最基本的两个组成部分。

组合电路的特点是电路任一时刻的输出仅与当时的输入有关,而与当前的状态无关。组合电路的设计只须注意如果采用条件语句,一定要采用完整的条件语句。

三、实验内容与步骤:

1、打开VHDL编辑器,完成七段译码器的设计。包括VHDL程序输入、编译、综合、适配、仿真。

实验程序如下(CASE语句实现):

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY DECODER IS

PORT(INP:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

OUTP:OUT BIT_VECTOR (6 DOWNTO 0);

SELIN:IN BIT_VECTOR(2 DOWNTO 0);

SELOUT:OUT BIT_VECTOR(2 DOWNTO 0));

END DECODER;

ARCHITECTURE ART4 OF DECODER IS

BEGIN

process(inp)

begin

CASE INP IS

WHEN "0000"=>OUTP<= "0111111";

WHEN "0001"=>OUTP<= "0000110";

WHEN "0010"=>OUTP<= "1011011";

WHEN "0011"=>OUTP<= "1001111";

WHEN "0100"=>OUTP<= "1100110";

WHEN "0101"=>OUTP<= "1101101";

WHEN "0110"=>OUTP<= "1111101";

WHEN "0111"=>OUTP<= "0000111";

WHEN "1000"=>OUTP<= "1111111";

WHEN "1001"=>OUTP<= "1101111";

WHEN "1010"=>OUTP<= "1110111";

WHEN "1011"=>OUTP<= "1111100";

WHEN "1100"=>OUTP<= "0111001";

WHEN "1101"=>OUTP<= "1011110";

WHEN "1110"=>OUTP<= "1111001";

WHEN "1111"=>OUTP<= "1110001";

WHEN OTHERS=>NULL;

END CASE;

end process;

SELOUT<=SELIN;

END ART4;

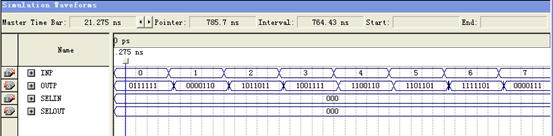

仿真结果如下:

2、引脚锁定并下载:

提示:在七段显示译码器实验时,可用拨码开关作为输入,一个数码管进行显示。

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

四、实验结果与总结:

实验六 用VHDL输入法设计计数器

一、实验目的:

熟悉VHDL程序的一般结构以及用VHDL语言设计计数器类型模块的描述方法。要求用VHDL语言设计设计实现一个异步清零、同步使能的16进制计数器,并完成设计输入、编译、仿真、硬件测试等过程。

二、实验原理:

计数器是在数字系统中使用最多的时序电路,它不仅能用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲和脉冲序列以及进行数字运算等。本实验设计实现16进制要求计数器有同步计数允许(/ENA低电平有效)和异步复位(/RESET低电平有效)输入及进位输出功能。计数器输入时钟可以用1MHZ或2HZ信号,显示计数值可以采用7段数码LED显示。

三、实验内容与步骤:

1、打开VHDL编辑器,完成16进制计数器的设计。包括VHDL程序输入、编译、综合、适配、仿真。

实验程序如下:16进制计数器程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT16 IS

PORT(CLK:IN STD_LOGIC;

RST:IN STD_LOGIC;

ENB:IN STD_LOGIC;

LD:IN STD_LOGIC;

DATA:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE behave OF CNT16 IS

SIGNAL q1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,RST,ENB,LD)

BEGIN

IF RST='0' THEN

Q1<="0000";

ELSIF CLK'EVENT AND CLK='1' THEN

IF LD='1' THEN

Q1<=DATA;

ElSIF ENB='1' THEN

Q1<=Q1+1;

END IF;

END IF;

END PROCESS;

Q<=Q1;

END BEHAVE;

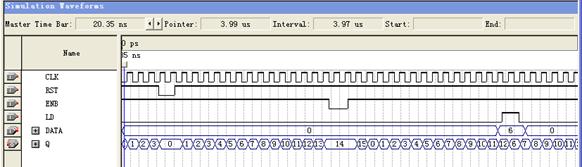

仿真结果如下:

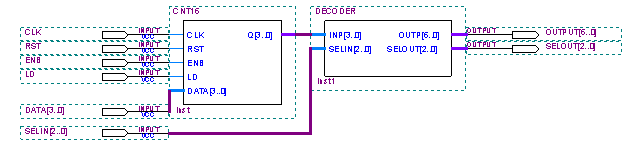

将计数器封装成模块,在顶层设计文件中调用计数器模块和上一实验中的译码器模块,完成计数显示功能,顶层原理图如下:

2、引脚锁定并下载:

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

=> 对应实验箱上的

四、实验结果与总结:

实验七 硬件电子琴电路验证实验

一、实验目的:

了解一般乐曲演奏电路设计方法;

通过本次实验熟悉VHDL语言的复杂系统的开发方法。

二、实验原理:

组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能够连续演奏所需的两个基本要素,设计演奏电路的关键就是获得这两个要素所对应的数值以及通过纯硬件的手段来利用这些数值实现所希望乐曲的演奏效果。

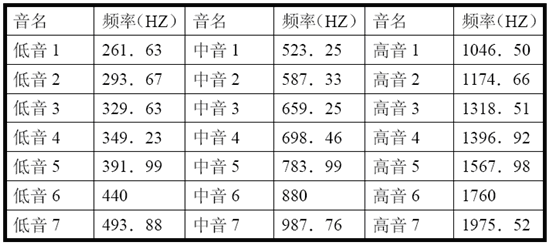

音名与频率的关系:

音乐的十二平均率规定:每两个八度音(如简谱中的中音1 与高音1)之间的频率相差一倍。在两个八度音之间,又可分为十二个半音,每两个半音的频率比为 。另外,音名A(简谱中的低音6)的频率为440Hz,音名B到C之间、E到F之间为半音,其余为全音。由此可以计算出简谱中从低音1至高音1之间每个音名的频率,如下表所示。

简谱中音名与频率的关系:

由于音阶频率多为非整数,而分频系数又不能为小数,故必须将计算得到的分频 数四舍五入取整。若基准频率过低,则由于分频系数过小,四舍五入取整后的误差较大。若基准频率过高,虽然误码差变小,但分频结构将变大。实际的设计应综合考虑两方面的因素,在尽量减小频率误差的前提下取合适的基准频率。

三、实验步骤及实验现象:

1、 启动QuartusII7.0软件,打开工程Test27/songer文件,下载songer.sof程序。

2、 将8位拨码开关CTRL的(1)档设置为“ON”,短接主板上的SK2。

3、 将TJ1频率段设置为4Hz档,TJ5频率段设置为32768Hz档,TJ9频率段设置为12MHz档,其余的频率段不加以设置。

实验现象:实验下载完毕,接通电源后,扬声器就开始连续演奏“梁祝”乐曲,并且可以通过电位器SW1来调节喇叭声音的大小。其中数码管SM1显示乐曲演奏的音符(高、中、低1~7音符);数码管SM4显示乐曲音符的高、中、低音(‘0’代表低音,‘1’代表中音,‘2’代表高音);数码管SM2~SM3显示常零。本设计得到的电路可以作为一个乐曲演奏模块,如果要演奏出另外一首曲子,只需将该曲子出现的简谱分频预置数写入ToneTaba.VHD,再将该曲子的节拍表输入到NoteTabs.VHD中,编译后,编程下载即可。

实验一 MaxplusⅡ软件的安装与使用

一、实验目的:

学习MaxplusⅡ软件的使用,包括软件安装及基本的使用流程。

本次实验是以半加器的原理图输入法设计为例,学习MaxplusⅡ软件的使用,体会用原理图输入法设计简单组合电路的方法和详细设计流程。掌握层次化设计的方法,并通过一位全加器的设计把握利用EDA软件进行原理图输入法进行电子线路设计的详细流程。为后续原理图的层次化设计打下基础。

本次实验不要求下载。

二、实验原理:

半加器可以通过调用基本的与、或、非门来实现。按照课本5.4节介绍的方法用原理图输入法设计一个半加器,然后将其封装成模块以备下次实验调用。

三、实验内容和步骤:

1、打开原理图编辑器,完成半加器的设计。

半加器原理图如下:

2、完成1位半加器的设计输入、目标器件选择、编译和仿真各步骤,详细的过程见教材5.4节相关内容。

仿真结果如下:

3、正确完成之后,选择File\create\Create Symbol file for current file,将文件变成一个包装好的单一元件模块待调用。

四、实验结果与总结: