实验七:寄存器实验

实验题目:寄存器实验

实验类型:设计性

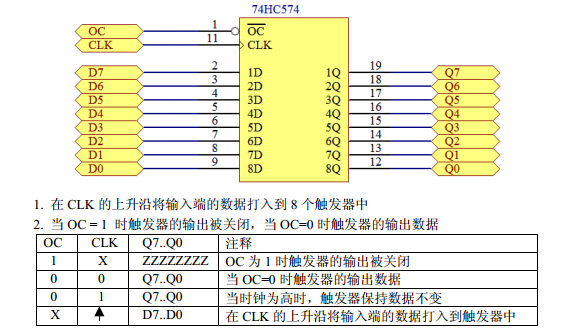

一、实验目的:掌握74HC574寄存器使用方法;掌握component语句和port map语句使用方法;掌握cop2000计算机组成原理实验仪的寄存器组实现方法;能用VHDL语言完成寄存器组的设计与仿真验证。

二、实验仪器设备及实验环境:计算机组成原理实验室,微机一台,quartus II软件。

三、总的设计思想、实验原理:

Cop2000计算机组成原理实验仪是南京伟福实业有限公司开发的实验设备,为配合讲授与学习计算机组成原理课程而研制。

Cop2000具有8位字长结构,实现了8种运算功能的ALU和4个8位字长的通用寄存器,同时ALU使用两个暂存器A和W,从硬件构成上来说,其用74HC574来构成寄存器,对于A、W和4个通用寄存器R0、R1、R2、R3都是用该芯片来实现。为了实现通用寄存器写入和读出的选择,使用了两个2:4译码器。

现在要求在quartusII环境下完成cop2000寄存器组的设计与仿真,可以先分别设计出8位寄存器74HC574和2:4译码器,然后使用component语句和port map语句完成整体设计。

四、实验步骤设计:

(1)完成8位寄存器74HC574的设计。设计程序如下:

程序源代码

ENTITY shifter IS

PORT (

data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入的数据

n : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位的数量

dir : IN STD_LOGIC; --移动的方向 0:左 1:右

kind : IN STD_LOGIC_VECTOR(1 DOWNTO 0);

clock : IN BIT; --手动时钟PULSE

data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --移位的结果

);

END shifter;

ARCHITECTURE behav of shifter IS

BEGIN

PROCESS (data_in, n, dir, kind)

VARIABLE x,y : STD_LOGIC_VECTOR(7 DOWNTO 0);

VARIABLE ctrl0,ctrl1,ctrl2 : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF (clock'EVENT AND clock = '1')THEN --产生控制向量ctrl

ctrl0 := n(0) & dir & kind(1) & kind(0);

ctrl1 := n(1) & dir & kind(1) & kind(0);

ctrl2 := n(2) & dir & kind(1) & kind(0);

CASE ctrl0 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => x := data_in; --n=0时不移动

WHEN "1000" => x := data_in(6 DOWNTO 0) & data_in(0); --算术左移1位

WHEN "1001" => x := data_in(6 DOWNTO 0) & '0'; --逻辑左移1位

WHEN "1010" => x := data_in(6 DOWNTO 0) & data_in(7); --循环左移1位

WHEN "1100" => x := data_in(7) & data_in(7 DOWNTO 1); --算术右移1位

WHEN "1101" => x := '0' & data_in(7 DOWNTO 1); --逻辑右移1位

WHEN "1110" => x := data_in(0) & data_in(7 DOWNTO 1); --循环右移1位

WHEN others => null;

END CASE;

CASE ctrl1 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => y := x; --n=0时不移动

WHEN "1000" => y := x(5 DOWNTO 0) & x(0) & x(0); --算术左移2位

WHEN "1001" => y := x(5 DOWNTO 0) & "00"; --逻辑左移2位

WHEN "1010" => y := x(5 DOWNTO 0) & x(7 DOWNTO 6); --循环左移2位

WHEN "1100" => y := x(7) & x(7) & x(7 DOWNTO 2); --算术右移2位

WHEN "1101" => y := "00" & x(7 DOWNTO 2); --逻辑右移2位

WHEN "1110" => y := x(1 DOWNTO 0) & x(7 DOWNTO 2); --循环右移2位

WHEN others => null;

END CASE;

CASE ctrl2 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => data_out <= y; --n=0时不WHEN "1000" => data_out <= y(3 DOWNTO 0) & y(0) & y(0) & y(0) & y(0); --算术左移4位

WHEN "1001" => data_out <= y(3 DOWNTO 0) & "0000"; --逻辑左移4位WHEN "1010" | "1110" => data_out <= y(3 DOWNTO 0) & y(7 DOWNTO 4); --循环左(右)移4位

WHEN "1100" => data_out <= y(7) & y(7) & y(7) & y(7) & y(7 DOWNTO 4); --算术右移4位

WHEN "1101" => data_out <= "0000" & y(7 DOWNTO 4); --逻辑右移4位

WHEN others => null;

END CASE;

END IF;

END PROCESS;

END behav;

(2)完成2:4译码器的设计。设计程序如下:

LIBRARY IEEE

USE IEEE STD_LOGIC_1164 ALL

EN TITY decode 2_to_4_t IS

PART(sel IN STD_LOGIC_VECTOR(1DOWNTO 0);

Sel 00,sel10,sel10,sel11 OUT STD_LOGIC);

END EN TITY decode 2_to_4_t

ARCHITE CUTURE dec OF decoder 2_to_4_t IS

BEGIN

PROCESS (sel)

BEGIN

CASE(sel) IS

WHEN ‘00’=>sel00<=‘I’,sel01<=‘0’;sel10<=‘0’;sel11<=‘0’;

WHEN ‘01’=>sel00<=‘0’,sel01<=‘1’;sel10<=‘0’;sel11<=‘0’;

WHEN ‘10’=>sel00<=‘0’,sel01<=‘0’;sel10<=‘1’;sel11<=‘0’;

WHEN ‘11’=>sel00<=‘0’,sel01<=‘0’;sel10<=‘0’;sel11<=‘1’;

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END ARCHITECTURE dec;

(3)完成顶层寄存器组的设计,设计程序如下:

library ieee;

use ieee.std_logic_1164.all;

entity registers is

port(

clk,reset,DRWr:in std_logic;

DR,SR:in std_logic_vector(1 downto 0);

d_input:in std_logic_vector(3 downto 0);

DR_data,SR_data:out std_logic_vector(3downto 0)

);

end entity;

architecture behav of registers is

signal sel00,sel01,sel10,sel11:std_logic;

signal inp0,inp1,inp2,inp3:std_logic_vector(3 downto 0);

component reg is

port(

clock,sel,w,clr : in std_logic;

D:in std_logic_vector(3 downto 0);

Q:out std_logic_vector(3 downto 0)

);

end component;

component t2_4 is

port(

sel:in std_logic_vector(1 downto 0);

sel00,sel01,sel10,sel11:out std_logic

);

end component;

component R4_to_1 is

port(

input0,input1,input2,input3:in std_logic_vector(3 downto 0);

sel:in std_logic_vector(1 downto 0);

R_data:out std_logic_vector(3downto 0)

);

end component;

begin

R0:reg port map (

clock=>clk,

sel=>sel00,

w=>DRWr,

clr=>reset,

D=>d_input,

Q=>inp0

);

R1:reg port map (

clock=>clk,

sel=>sel01,

w=>DRWr,

clr=>reset,

D=>d_input,

Q=>inp1

);

R2:reg port map (

clock=>clk,

sel=>sel10,

w=>DRWr,

clr=>reset,

D=>d_input,

Q=>inp2

);

R3:reg port map (

clock=>clk,

sel=>sel11,

w=>DRWr,

clr=>reset,

D=>d_input,

Q=>inp3

);

trans:t2_4 port map(

sel=>DR,

sel00=>sel00,

sel01=>sel01,

sel10=>sel10,

sel11=>sel11

);

DR_d:R4_to_1 port map(

input0=>inp0,

input1=>inp1,

input2=>inp2,

input3=>inp3,

sel=>DR,

R_data=>DR_data

);

SR_d:R4_to_1 port map(

input0=>inp0,

input1=>inp1,

input2=>inp2,

input3=>inp3,

sel=>SR,

R_data=>SR_data

);

end architecture;

(4)进行编译,通过后建立仿真波形文件,然后进行功能仿真。

(5)获得功能仿真波形图,对照查看,检查是否满足设计要求。

五、实验结果及分析:

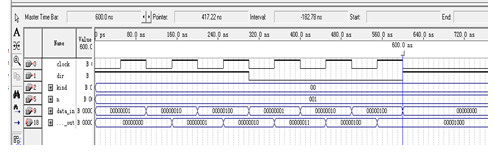

功能仿真波形图如下:

分析说明如下:

完成时序仿真之后在Assignment的Settings中选定仿真类型为Function(功能仿真),对波形图进行保存然后运行,即生成功能仿真图。从图中可以看到,延迟现象得到解决,各个波段输入对应输出更加清楚。在时序仿真中弄不太明白的clock的作用也在这里得到解决:clock=1左/右移功能实现,clock=0功能未执行,输出保留为上一个波段的结果。

六、自我评价与总结:

通过这次的实验,我移位寄存器无论从功能还是原理方面都有了较为系统的了解和学习。

这次实验没有给现成的代码,不过在网上可以找到对应的源代码,而且源代码附着较为详细的注释,方便了我的学习。找到源代码之后的编译、仿真部分因为熟能生巧,都较为顺利。但一开始仿真时候波段的值没有选好,乱七八糟的找不到对比,这对理解分析功能造成了一定的困惑。多次重复试验之后,终于画出来可以帮助我更好理解左/右移意义的仿真图。虽然有点繁琐,但是所幸有所收获。

在不知不觉中,我们已经完成了七个实验。随着实验越做越多,一方面我们自身对软件的熟悉度越来越高,另一方面实验的题目越来越“抽象”,功能也是越来越复杂。这次实验只有题目,没有细节的真值表功能表等等,但在自己研究摸索的过程中,收获得更多。实验不是照本宣科敲代码,更重要是有自己的思考和收获,这种在不断研究和探索的过程中培养出来的学习能力,才是实验带给我们最宝贵的财富(当然实验结果也是很重要滴~)!

实验所需资料:

(1)74HC574情况。

(2)COP2000的寄存器组情况。

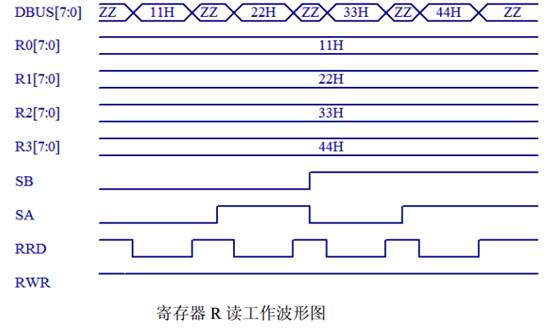

下面的波形图不是quartus II 上仿真出来的波形,只是说明该寄存器组应具有的读/写功能情况。

第二篇:通用寄存器实验

黄河科技学院信息工程类实验报告

院系: 专业: 班级:

姓名: 学号: 实验课程:

实验项目名称: 实验时间:

指导教师签字: 成绩:

实验一 通用寄存器组实验

1.实验目的和要求

⒈ 熟悉通用寄存器概念。

⒉ 熟悉通用寄存器的组成和硬件电路。

3. 完成3个通用寄存器的数据写入与读出。

2.实验原理

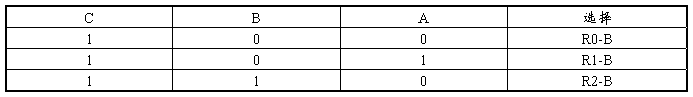

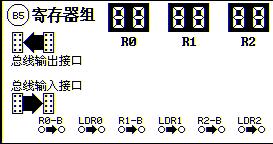

实验中所用的通用寄存器数据通路如图1-1所示。由三片8位字长的74LS374组成R0、R1、R2寄存器组成。三个寄存器的输入接口用一8芯扁平线连至BUS总线接口,而三个寄存器的输出接口用一8芯扁平线连至BUS总线接口。图中R0-B、R1-B、R2-B经CBA二进制控制开关译码产生数据输出选通信号(详见表1-1),LDR0、LDR1、LDR2为数据写入允许信号,由二进制控制开关模拟,均为高电平有效;T4信号为寄存器数据写入脉冲,上升沿有效。在手动实验状态(即“L”状态)每按动一次【单步】命令键,产生一次T4信号。

图1-1 通用寄存器单元电路

表1-1 通用寄存器单元选通真值表

3.主要仪器设备(实验用的软硬件环境)

1、Dais-cmh+计算机组成原理实验箱 一台

2、导线若干

4.操作方法与实验步骤

l、按图1-2连接实验线路,仔细检查无误后,接通电源。(图中箭头表示需要接线的地方,接总线和控制信号时要注意高低位一一对应,可用彩排线的颜色来进行区分)

图1-2 实验连线示意图

按图7-2-2所示,连接实验电路:

① 总线接口连接:用8芯扁平线连接图1-2中所有标明“ ”或“

”或“ ”图案的总线接口。

”图案的总线接口。

② 控制线与时钟信号“ ”连接:用双头实验导线连接图1-2中所有标明“

”连接:用双头实验导线连接图1-2中所有标明“ ”或“

”或“ ”图案的插孔(注:Dais-CMH的时钟信号已作内部连接)。

”图案的插孔(注:Dais-CMH的时钟信号已作内部连接)。

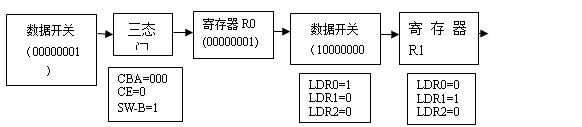

2、通用寄存器的写入

拨动二进制数据开关向R0和R1寄存器置数,具体操作步骤如下:

注:【单步】键的功能是启动时序电路产生T1~T4四拍单周期脉冲

3、通用寄存器的读出

关闭数据输入三态(SW-B=0),存储器控制端CE=0,令LDR0=0、LDR1=0、LDR2=0,分别打开通用寄存器R0、R1、R2输出控制位,置CBA=100时,按【单步】键,数据总线单元显示R0中的数据01H;置CBA=101时,按【单步】键。数据总线单元显示R1中的数据80H;置CBA=110时,按【单步】键,数据总线单元显示R2中的数据。

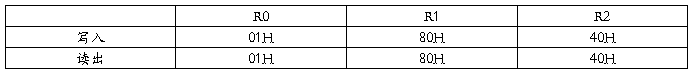

5.实验内容及实验数据记录

通过以上的步骤我们已经在通用寄存器组的三个寄存器中分别存入了一下数据,同时也读出了三个寄存器中存放的数据,具体数据如下表所示:

6.实验数据处理与分析

按照实验步骤对通用寄存器组进行了数据的写入和读出,两组数据完全对照,

说明了存入数据的正确性,在整个过程中也对寄存器组的构成和硬件电路有了更深层次的理解。

7.实验思考

试利用该实验的硬件电路,用最简便的方法在三个寄存器中存入三个相同的内容。