实验报告

实验名称_______________

姓名__________学号___________

同组同学姓名__________学号__________

实验日期______________

实验完成日期______________

1.实验题目名称: 寄存器实验

2.实验目的:1)掌握QuartusII 5.0软件的图形编辑、编译、 仿真的设计流程。

2)学习74670三态输出寄存器堆的使用。

3)了解寄存器组的使用,设计出完善的寄存器组。

3.实验内容:设计出功能完善的寄存器组,并对设计的正确性进行验证。具体要求如下:

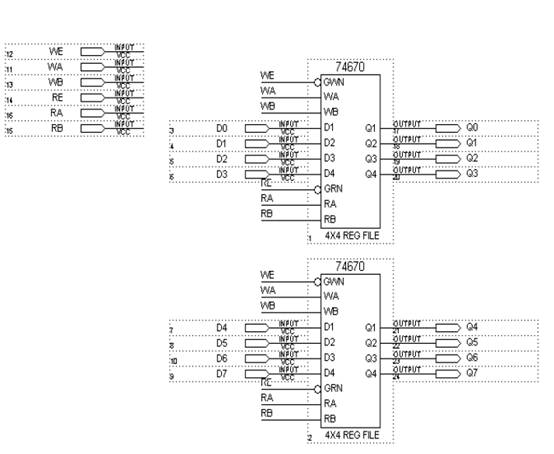

1)用图形方式设计出寄存器组的电路原理图。

2)测试波形要用时序仿真实现,现将不同的数据连续写入4个寄存器后,在分别读出。

3)将设计文件封装成器件符号。

4)数据的宽度最好为16位。

4.实验设计思想:

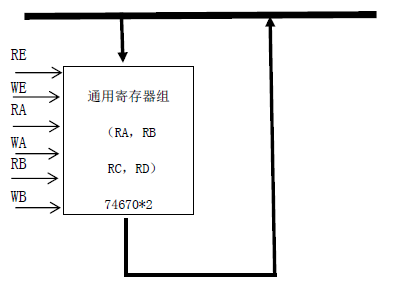

在主机系统中,寄存器组用于暂存程序运行过程中所需要的各种数据。可以采用具有三态功能的两片4位片的74LS760芯片进行设计。构成4字*8位的寄存器组。通用寄存器组的设计原理图如下:

通用寄存器组的设计原理图

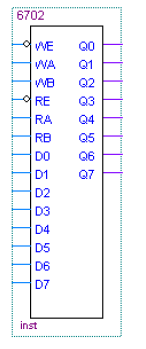

5. 芯片封装图

通用寄存器组芯片封装图

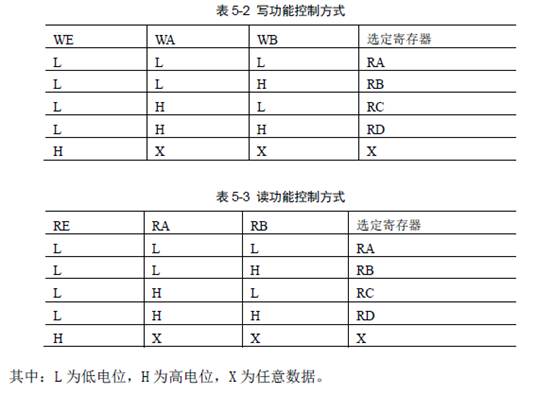

图中RA,RB输出控制管脚接收需要读出信息的通用寄存器地址,在RE读控制信号的作用下,输出相应寄存器中的数据到输出管脚Q0~Q7端。WA,WB输入控制管脚接收需要写入信息的通用寄存器的地址,在WE写控制信号的作用下,把输入管脚D0~D7的输入数据写入到相应的寄存器中。其通用寄存器的“写”“读”功能控制方式可参见表

5-2,5-3.

6.逻辑电路图

6.实验结果:

7.实验小结:

1)实验过程中所遇到的问题及其分析:

2)解决的方法:

3)实验收获:

4)对实验的意见和建议:

第二篇:通用寄存器组实验报告

通用寄存器组

学号:2010434096 姓名:贾雨飞 专业:软件工程

一、 实验目的

(1) 了解通用寄存器组的用途及对CPU的重要性。

(2) 掌握通用寄存器组的设计方法。

二、 实验原理

通用寄存器组是CPU的重要组成部分。从存储器取来的数据要放在通用寄存器中;从外部设备取来的数据除DMA方式外,要放在通用寄存器中。向存储器输出的数据也是从通用寄存器中取出;向外部设备输出的数据除DMA方式外也是从通用寄存器中取出来的。由于从通用寄存器组中取数据比从存储器或者外部设备取数据快得多,因此参加算术运算和逻辑运算的数据一般是从通用寄存器组中取出,它向算术逻辑单元ALU提供了进行算术运算和逻辑运算所需要的两个操作数,同时又是运算结果的暂存地。通用寄存器组内寄存器的数目与CPU性能有关,CPU性能预告,通用寄存器组内的寄存器数目越多。由于算术逻辑运算需要两个操作数,因此通用寄存器组有两个读端口,负责提供进行算术逻辑单元需要的源操作数和目的操作数。通用寄存器组有1个写端口,负责将运算结果保存到指定的寄存器内。根据通用寄存器组的功能要求,一个只有4个16位寄存器的通用寄存器组的框图如下图所示。

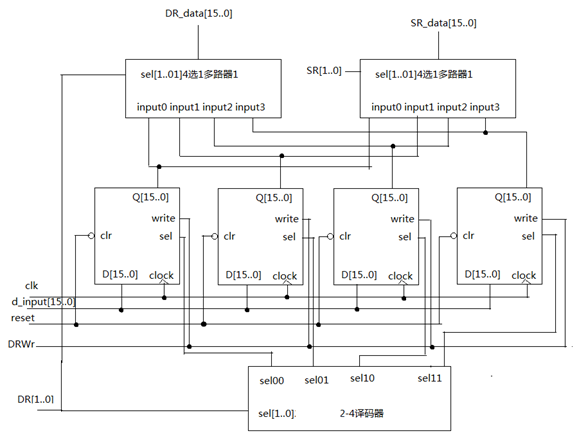

在上图所示的电路中,当reset为低电平时,将4个16位寄存器R0~R3复位为0。当寄存器的write和sel为高电平时,在时钟信号clk的上升沿将D端的输入D[15..0]写入寄存器,然后送到寄存器的输出Q[15..0]。4个寄存器的允许写信号write和外部产生的目的寄存器写信号DRWr直接相连。每个寄存器还有另一个选择信号sel,它决定哪一个寄存器进行写操作。4个寄存器的选择信号分别和2-4译码器产生的sel00、sel01、sel10和sel11相连。只有当1个寄存器被选中时,才允许对该寄存器进行写操作。2-4译码器的输入sel[1..0]接DR[1..0],2-4译码器对2位的输入信号sel[1..0]进行2-4译码,产生4个输出sel00、sel01、sel10和sel11,分别送往4个寄存器R0、R1、R2、R3的选择端4选1多路选择器1从4个寄存器R0、R1、R2、R3的输出Q[15..0]选择1路送到DR_data[1..0],给算术逻辑单元提供目的操作数;选择信号sel[1..0]接DR[1..0]。4选1多路选择器2从4个寄存器R0、R1、R2、R3的输出Q[15..0]选择一路送到SR_data[1..0],给算术逻辑单元提供源操作数;选择信号sel[1..0]接SR[1..0]。

三、实验要求

1、实验设计目标

设计一个通用寄存器组,满足以下要求:

(1) 通用寄存器组有4个16位的寄存器。

(2) 当复位信号reset=0时,将通用寄存器组中的4个寄存器清零。

(3) 通用寄存器组中有1个写入端口,当DRWr=1时,在时钟clk的上升沿将数据总线上的数写入DR[1..0]指定的寄存器。

(4) 通用寄存器组中有两个读出端口,一个对应算术逻辑单元的目的操作数DR,另一个对应算术逻辑单元的源操作数SR。DR[1..0]选择目的操作数;SR[1..0]选择源操作数。

(5) 设计要求层次设计。底层的设计实体有3个:16位寄存器,具有复位功能和允许写功能;一个2-4译码器,对应寄存器写选择;一个4选1多路开关,负责选择寄存器的读出。顶层设计构成一个完整的通用寄存器组。

2、顶层设计实体的引脚要求

引脚要求对应关系如下

(1) clk对应实验台上的时钟(单脉冲)。

(2) reset对应试验台上的CPU复位信号CPU-RST。

(3) SR[1...0]对应试验台开关SA1,SA0。

(4) DR[1..0]对应试验台开关SA3,SA2。

(5) DRWr对应试验台开关SA5。

(6) 目的操作数用实验台上的指示灯A15~A0显示,源操作数用试验台上的指示灯R15~R0显示。

(7) d-input接开关SD15~SD0。

四、实验主要代码

library ieee;

use ieee.std_logic_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity to2_4 is

port

(

sel:in std_logic_vector(1 downto 0);

sel00,sel01,sel02,sel03: out std_logic

);

end entity;

architecture rtl of to2_4 is

begin

sel00<=(not sel(1))and(not sel(0));

sel01<=(not sel(1))and sel(0) ;

sel02<=sel(1) and (not sel(0)) ;

sel03<=sel(1) and sel(0) ;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity to4_1 is

port

(

input0,input1,input2,input3:in std_logic_vector(15 downto 0);

sel:in std_logic_vector(1 downto 0);

cout :out std_logic_vector(15 downto 0) );

end entity;

architecture rtl of to4_1 is

begin

process(sel, input0, input1, input2, input3)

begin

case sel is

when "00" =>

cout<=input0;

when "01" =>

cout<=input1;

when "10" =>

cout<=input2;

when "11" =>

cout<=input3;

end case;

end process;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

entity reg is

port

(

clr: in std_logic;

D: in std_logic_vector(15 downto 0);

clock,w,sel: in std_logic;

Q: out std_logic_vector(15 downto 0) );

end reg;

architecture rtl of reg is

begin

process(clr,clock)

begin

if clr = '0' then

Q <= x"0000";

elsif (clock'event and clock = '1') then

if sel = '1' and w = '1' then

Q <= D;

end if;

end if;

end process;

end rtl;

library ieee;

use ieee.std_logic_1164.all;

entity jicunqi is

Port ( DR: in std_logic_vector(1 downto 0);

SR: in std_logic_vector(1 downto 0);

reset: in std_logic;

DRWr: in std_logic;

clk: in std_logic;

d_input: in std_logic_vector(15 downto 0);

DR_data: out std_logic_vector(15 downto 0);

SR_data: out std_logic_vector(15 downto 0) );

end jicunqi;

architecture rtl of jicunqi is

component reg

port (

clr: in std_logic;

D: in std_logic_vector(15 downto 0);

clock,w,sel: in std_logic;

Q: out std_logic_vector(15 downto 0)

);

end component;

component to2_4

port(

sel:in std_logic_vector(1 downto 0);

sel00,sel01,sel02,sel03: out std_logic

);

end component;

component to4_1

port (

input0,input1,input2,input3: in std_logic_vector(15 downto 0);

sel: in std_logic_vector(1 downto 0);

cout: out std_logic_vector(15 downto 0));

end component;

signal reg00, reg01, reg02, reg03

:std_logic_vector(15 downto 0);

signal sel00 ,sel01 ,sel02 ,sel03

: std_logic;

begin

Areg00: reg port map(reset,d_input ,clk ,DRWr ,sel00 ,reg00);

Areg01: reg port map(reset,d_input ,clk ,DRWr ,sel01 , reg01);

Areg02: reg port map(reset,d_input ,clk ,DRWr ,sel02 ,reg02);

Areg03: reg port map(reset,d_input ,clk ,DRWr ,sel03 ,reg03);

decoder: to2_4 port map(DR,sel00 , sel01 , sel02 ,sel03 );

mux1: to4_1 PORT MAP( reg00 , reg01 ,reg02 ,reg03 ,DR ,DR_data);

mux2: to4_1 PORT MAP( reg00 ,reg01 , reg02 , reg03 , SR ,SR_data);

end rtl;

五、实验步骤

(1)将实验台设置成FPGA-CPU独立调试模式,REGSEL=0、CLKSEL=1、FDSEL=0。使用试验台上的单脉冲,即DTEP_CLK短路子短接,短路子RUN_CLK断开。

(2)将涉及在QuartusII下输入,编译后下载到TEC_CA上的FPGA中。

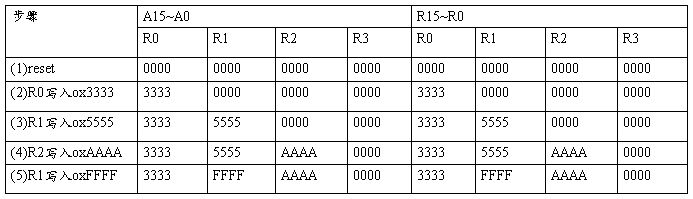

(3)将下列数据存入寄存器:

R0 0x3333

R1 0x5555

R2 0xAAAA

R3 oxFFFF

(4)在试验台指示灯A15~A0和R15~R0上观察各寄存器的值,并填入下表。

六、实验收获

通过这次实验了解了通用寄存器组对于CPU的重要性,了解了通用寄存器的使用方法。熟悉了VHDL语言描述通用寄存器的方法。