南京信息工程大学

数字电路

实验报告

学号:20111305062

班级:11电信2班

姓名:杨天星

第一章

一、引言

计数器电路是一种随时钟输入CP的变化,其输出按一定的顺序变化的时序电路,其变化的特点不同可将计数器电路按以下几种进行分类:

按照时钟脉冲信号的特点分为同步计数器和异步计数器两大类,其中同步计数中构成计数器的所有触发器在同一个时刻进行翻转,一般来讲其时钟输入端全连在一起;异步计数器即构成计数器的触发器的时钟输入CP没有连在一起,其各触发器不在同一时刻变化。一般来讲,同步计数器较异步计数器具有更高的速度。

按照计数的数码变化升降分为加法计数器和减法计数器,也有一些计数器既可实现加计数又可实现减计数器,这类计数器为可逆计数器。按照输出的编码形式可分为:二进制计数器、二—十进制计数器、循环码计数器等。

按计数的模数(或容量)分:十进制计数器、十六进制计数、六十进制计数器等。

二、主要设计要求

利用74LS163设计模为100的计数器

第二章

一、电路设计和分析

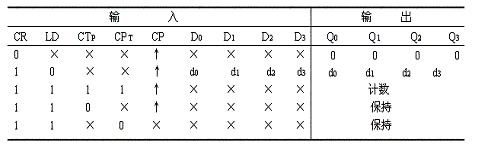

1、74LS163逻辑功能表

2、芯片特性

74LS163为二进制四位并行输出的计数器,它有并行装载输入和同步清零输入端。

74LS00为四二输入与非门。

74LS20为四输入与非门。

3、设计思路

用两个模为10的计数器构成模为100的计数器。模为10的计数

器实现方法:用一个与非门,两个输入取自QA和QD,输出接清零段CLR。当第9个脉冲结束时,QA和QD都为“1”,则与非门输出为“0”,并加到CLR端,因CLR为同步清零端,此时虽已建立清零信号,但并不执行,只有第10个时钟脉冲到来后74LS163才被清零。

器实现方法:用一个与非门,两个输入取自QA和QD,输出接清零段CLR。当第9个脉冲结束时,QA和QD都为“1”,则与非门输出为“0”,并加到CLR端,因CLR为同步清零端,此时虽已建立清零信号,但并不执行,只有第10个时钟脉冲到来后74LS163才被清零。

4、电路仿真

第三章

一、实验结果分析

1、设计结果

该设计可以实现0到99循环计数。

2、遇到的问题

一开始设计时,只简单完成了2个10位计数器功能,以至于没有考虑到十位清零问题,做出来的是90进制的计数器。

3、解决方法

将十位163芯片的ENT引脚与QA和QD一起通过与非门接到CLR,这样当计数器到99时就会给CLR一个低电平,使十位清零。

将十位163芯片的ENT引脚与QA和QD一起通过与非门接到CLR,这样当计数器到99时就会给CLR一个低电平,使十位清零。

第四章

1、设计优缺点

能实现0到99任意置数并计数。缺点是所用芯片较多,连线复杂。

2、课程总结

数电实验课程是数字电路学习的实践课程,通过该课程的学习,我体会到理论要与实践结合才能发挥作用,只学习理论并不一定能完成一些实际的设计。看似很简单的题目到真正来做的时候就会出现各种错误,这也提醒我在以后的学习中要多多实践,将学到的理论知识灵活地运用到实践中去,不断提高自己的动手能力。另外在实践中不能想当然的去猜想,一定要通过实践来检测设计的电路是否正确。对于本课程,我希望能在多增加一点课时,熟能生巧,多思考,多动手,才会有真正的收获。

第二篇:100进制同步计数器设计报告

浙江万里学院实验报告

课程名称:可编程逻辑器件应用

实验名称: 100进制同步计数器设计

专业班级:电子103姓名:徐强 学号: 2010014092 实验日期:2011.5.10

一、实验目的:

1、掌握计数器的原理及设计方法;

2、设计一个0~100的计数器;

3、利用实验二的七段数码管电路进行显示;

二、实验要求:

1、用VHDL 语言进行描写;

2、有计数显示输出;

3、有清零端和计数使能端;

三、实验结果:

1. VHDL程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

PACKAGE my_pkg IS

Component nd2 -- 或门

PORT (a,b: IN STD_LOGIC;

c: OUT STD_LOGIC);

END Component;

Component led_decoder

PORT (din:in std_logic_vector(3 downto 0 ); --四位二进制码输入

seg:out std_logic_vector(6 downto 0) ); --输出LED七段码

END Component;

Component CNT60 --2位BCD码60进制计数器

PORT

( CR:IN STD_LOGIC;

EN:IN STD_LOGIC;

CLK:IN STD_LOGIC;

OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END Component;

Component CNT100 --带使能和清零信号的100进制计数器

PORT

(

CLK:IN STD_LOGIC;

EN:IN STD_LOGIC;

CLR:IN STD_LOGIC;

OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) );

END Component;

Component freq_div --50MHZ时钟分频出1Hz

PORT

(

clkinput : IN STD_LOGIC;

output : OUT STD_LOGIC

);

END Component;

Component jtd --交通灯控制器

PORT

(

CLKIN:IN STD_LOGIC; --50MHZ

R1,G1,R2,G2,R3,G3,R4,G4:OUT STD_LOGIC; --红绿灯信号输出

GAO,DI:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0) --倒计时输出

);

END Component;

END my_pkg;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE work.my_pkg.ALL; --打开程序包

ENTITY Demo3 IS

PORT (CRl:IN STD_LOGIC;

ENl:IN STD_LOGIC;

CLKIN: IN STD_LOGIC;

LEDLOW,LEDHIGH: OUT STD_LOGIC_VECTOR(6 downto 0));

END Demo3;

ARCHITECTURE behv OF Demo3 IS

SIGNAL CLKTEMP: STD_LOGIC; --定义中转信号

SIGNAL LEDLOWTEMP,LEDHIGHTEMP:STD_LOGIC_VECTOR(3 downto 0);

BEGIN

u1:freq_div PORT MAP(CLKIN,CLKTEMP); --位置关联方式

u2:CNT60 PORT MAP(CR=>CRl,EN=>ENl,CLK=>CLKTEMP,OUTLOW=>LEDLOWTEMP,OUTHIGH=>LEDHIGHTEMP); --名字关联方式

u3:led_decoder PORT MAP(LEDLOWTEMP,LEDLOW); --低位数码管输出

u4:led_decoder PORT MAP(LEDHIGHTEMP,LEDHIGH); --高位数码管输出

END behv;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY freq_div IS

PORT

(

clkinput : IN STD_LOGIC;

output : OUT STD_LOGIC

);

END freq_div;

ARCHITECTURE rt OF freq_div IS

SIGNAL count_signal : INTEGER RANGE 0 TO 25000000;

signal mid1 : STD_LOGIC ;

BEGIN

PROCESS (clkinput)

BEGIN

IF (clkinput'EVENT AND clkinput = '1') THEN

if count_signal=24999999 then --50MHz division to 1Hz

count_signal <= 0;

mid1<= not mid1;

else

count_signal <= count_signal + 1;

end if;

output <= mid1;

end if;

END PROCESS;

end rt;

--文件名:decoder.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity led_decoder is

Port (din:in std_logic_vector(3 downto 0 ); --四位二进制码输入

seg:out std_logic_vector(6 downto 0) ); --输出LED七段码

end led_decoder;

architecture Behavioral of led_decoder is

begin

process(din)

begin

case din is

when "0000" =>

seg<="1000000";--0

when "0001" => seg<="1111001";--1

when "0010" => seg<="0100100";--2

when "0011" => seg<="0110000";--3

when "0100" => seg<="0011001";--4

when "0101" => seg<="0010010";--5

when "0110" => seg<="0000010";--6

when "0111" => seg<="1011000";--7

when "1000" => seg<="0000000";--8

when "1001" => seg<="0010000";--9

when others => seg<="0000110";--E

end case;

end process;

end Behavioral;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT60 IS

PORT

(

CR:IN STD_LOGIC;

EN:IN STD_LOGIC;

CLK:IN STD_LOGIC;

OUTLOW:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);

OUTHIGH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)

);

END CNT60;

ARCHITECTURE behav OF CNT60 IS

BEGIN

PROCESS(CLK,CR,EN)

BEGIN

if CR='1' then

OUTHIGH<="0000";

OUTLOW<="0000";

elsif EN ='1'then

IF CLK'EVENT AND CLK='1' THEN

IF OUTHIGH="1001" AND OUTLOW="1001" THEN

OUTHIGH<="0000";

OUTLOW<="0000";

ELSIF OUTLOW="1001" THEN

OUTHIGH<=OUTHIGH+1;

OUTLOW<="0000";

ELSE OUTLOW<=OUTLOW+1;

END IF;

END IF;

END IF;

END PROCESS;

END behav;

2. 仿真结果以及说明

3. 程序下载及运行情况说明

四、实验总结: