四位全加器

11微电子 黄跃 1117426021

【实验目的】

采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

【实验内容】

加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).

【实验原理】

全加器

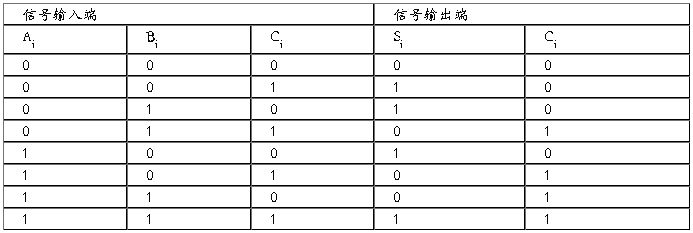

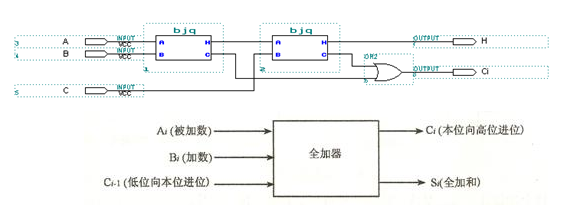

除本位两个数相加外,还要加上从低位来的进位数,称为全加器。图4为全加器的方框图。图5全加器原理图。被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci作为电路的输出。能实现全加运算功能的电路称为全加电路。全加器的逻辑功能真值表如表2中所列。

表2 全加器逻辑功能真值表

图4 全加器方框图

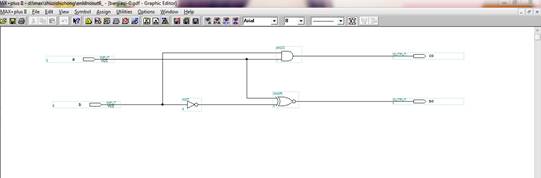

图5 全加器原理图

多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。

四位全加器

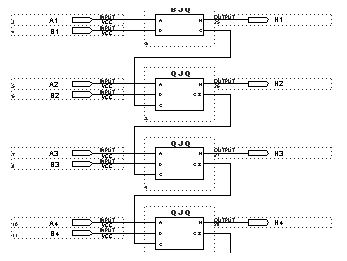

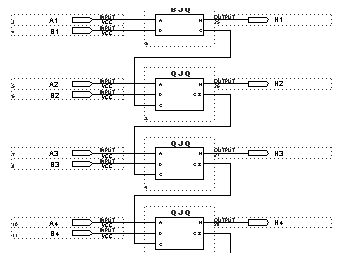

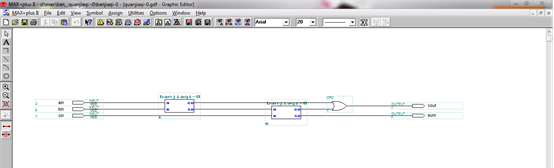

如图9所示,四位全加器是由半加器和一位全加器组建而成:

图9 四位全加器原理图

【实验步骤】

(1)建立新工程项目:

打开modelsim软件,进入集成开发环境,点击File→New project建立一个工程项目adder_4bit。

建立文本编辑文件:

点击File→New在该项目下新建Verilog源程序文件adder_4bit.v

并且输入源程序。

(2)编译和仿真工程项目:

在verilog主页面下,选择Compile— Compile All或点击工具栏上的按钮启动编译,直到project出现status栏全勾,即可进行仿真。

选择simulate - start simulate或点击工具栏上的按钮开始仿真,在跳出来的 start simulate框中选择work-test_adder_4bit测试模块,同时撤销Enable Optimisim前的勾,之后选择ok。

在sim-default框内右击选择test_adder_4bit,选择Add Wave,然后选择simulate-run-runall,观察波形,得出结论,仿真结束。

四位全加器

1、 原理图设计

如图9所示,四位全加器是由半加器和一位全加器组建而成:

图9 四位全加器原理图

【仿真和测试结果】

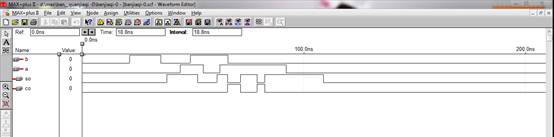

下图为四位全加器的仿真图:

图10 仿真图

【程序源代码】

1位全加器程序代码如下:

module f_adder(a,b,cin,sum,cout);

output sum,cout;

input a,b,cin;

wire s1,c1,c2;

xor(s1,a,b);

and(c1,a,b);

or(sum,s1,cin);

and(c2,s1,cin);

xor (cout,c2,c1);

endmodule

四位全加器程序代码如下:

module adder_4bit(s,co,a,b,ci);

output[3:0] s;

output co;

input[3:0] a,b;

input ci;

wire ci1,ci2,ci3;

f_adder f0(a[0],b[0],ci,s[0],ci1);

f_adder f1(a[1],b[1],ci1,s[1],ci2);

f_adder f2(a[2],b[2],ci2,s[2],ci3);

f_adder f3(a[3],b[3],ci3,s[3],co);

Endmodule

四位全加器测试程序代码如下:

module test_adder_4bit;

reg [3:0] A,B;

reg CI;

wire [3:0] S;

wire CO;

adder_4bit A1(S,CO,A,B,CI);

initial

begin

$monitor($time,"A=%b,B=%b,CI=%b,CO=%b,S=%b\n",A,B,CI,CO,S);

end

initial

begin

A=4'd0;B=4'd0; CI=1'B0;

#5 A=4'd3;B=4'd4;

#5 A=4'd2;B=4'd5;

#5 A=4'd9;B=4'd9;

#5 A=4'd10;B=4'd15;

#5 A=4'd10;B=4'd5;CI=1'b1;

end

endmodule

【实验心得和体会】

通过设计4位全加器,熟练了原理图输入方法,学会使用Verilog语言输入方法,也能较灵活地使用modlesim软件。

由时序图可以看出实现了4位全加器的功能,Verilog的程序设计是正确的,实验是成功的。

第二篇:EDA全加器实验报告

实验一:1位全加器设计

实验目的:用原理图输入法完成半加器和全加器的设计,熟悉和练习Max+PlusⅡ的应用。

实验原理:1位全加器可以用两个半加器及一个或门连接而成,因此需要首先完成半加器的设计。用最简单的原理图输入法来完成半加器及全加器的设计。

实验内容:

一:(1)、建立一个文件夹,设此文件夹为本项设计工程的工作库。文件夹起名为Quanjiaqi。

(2)、进入原理图输入系统,在File/New下建立新的原理图设计文件。

(3)、在原理图输入窗口中右击选择输入元件项Enter Symbol,在所弹出窗口中查找所需元件INPUT、OUTPUT、AND2、XNOR、NOT并放入当前窗口。完成半加器电路图(如下图)并起名为Banjiqi.gdf保存在Quanjiaqi工作库内。

(4)、选择File/Project/Set Project to Current File项,将当前设计项目设置成工程文件。然后在MAX+PLUSⅡ下拉菜单中选择Compiler项对原理图工程文件进行编译。

(4)、选择File/Project/Set Project to Current File项,将当前设计项目设置成工程文件。然后在MAX+PLUSⅡ下拉菜单中选择Compiler项对原理图工程文件进行编译。

(5)、进入波形文件输入系统,在File/New下建立新的波形设计文件,文件名默认为Banjiaqi.scf。

(6)、选择Node/Node from SNF项,在弹出的窗口首选List键,将节点信号添加到右栏。

(7)、设置波形参量,设置File/End time项为34us,设半加器输入信号a、b为高低电平,保存文件,用默认文件名及扩展名。

(8)、运行时序仿真器:选择MAX+plusⅡ/Simulateor项,并观察分析输出信号co、so。波形图如下

(9)、选择File/open下Banjiaqi.gdf文件,并将其设置成当前工程文件,然后选择File/

C reate Default Symbol项将当前文件设置成包装好的单一元件,留以备用。

二、(1)、重复“一”中的步骤从第(2)开始,将调入元件改成INPU、TOUTPUT、OR2以及第一步中包装入库的Banjiaqi元件,输入原理图,起名为Quanjiaqi.gdf保存在Quanjiaqi工作库中,并对其进行编译。

(2)、设置Quangjiaqi原理图文件的波形文件,并对其进行时序仿真。步骤重复“一”,从第(5)步开始。文件默认为Quanjiaqi.scf输入信号端为ain、bin、cin,输出信号端为sum、cout,对其进行观察分析。

三、(1)、选择Assign/ Device选择EPF10K10LC84-4型号芯片,然后选择Assign/Pin\Location\Chip选项,在弹出的窗口中Node Name栏中输入全加器端口名ain、bin、cin并选择芯片引脚号。从Pin Type选项中选择Input型,Sum、cout选择Output型。

(2)、在引脚锁定完成后,选择MAX+plusⅡ/Compiler选项对文件从新进行编译一次。

(3)、选择MAX+plusⅡ/Programmer选项,在弹出的窗口,然后选择Option/Hardwere Setup硬件选项,并在其下拉菜单中选ByteBlaster(MV)编程方式。

(4)、点击Configure键,将设计文件下载到芯片,用实验箱对芯片进行实验,验证全加器功能。