序言

数字钟是采用数字电路实现对时、分、秒数字显示的 计时装置,广泛用于个人家庭,车站, 码头办公室等公共场所,成 为人们日常生活中不可少的必需品,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,运运超过老式钟表, 钟表的数字化给人们生产生活带来了极大的方便而且大大地扩展了钟表原先的报时功能。因此,研究数字钟及扩大其应用,有着非常现实的意义。

目录

摘要…………………………………………………………………………………………3

1. 方案选择和论证…………………………………………………………………………4

1.1系统基本方案选择和论证………………………………………………………………4

1.1.1芯片的选择方案和论证…………………………………………………………… 4

1.1.2 显示模块选择方案和论证………………………………………………………… 4

1.1.3脉冲发生器的选择方案和论证…………………………………………………… 4

1.2 电路设计最终方案决定……………………………………………………………… 4

2.各模块的功能原理及器件选择………………………………………………………… 5

2.1功能要求 …………………………………………………………………………………5 2.2设计方案 ……………………………………………………………………………… 5

2.3 单元电路的设计…………………………………………………………………………5

2.3.1主体电路部分……………………………………………………………………………6

2.3.2振荡电路……………………………………………………………………………… 6

2.3.3计数电路……………………………………………………………………………… 7

2.3.4校时电路………………………………………………………………………………11

2.3.5译码与显示电路 …………………………………………………………………… 12

2.4主要设备及器件………………………………………………………………………… 14

3.结果分析…………………………………………………………………………… 15

4设计小结 …………………………………………………………………………………16

5 参考文献……………………………………………………………………………………16

附录整体电路图 ………………………………………………………………………………17

【摘要】数字时钟电路系统由主电路和扩展电路两大部分组成的。主电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能。振荡器是数字钟的核心,振荡器的频率越高,计时精度越高。有555构成的多谐振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,在经分频器输出标准脉冲.秒计数器满60分后向分数器进位,分数器计满60后向小时计数器进位,小时计数器按照“12翻1”规律计数。计数器的输出经译码器送显示器。计时出现误差时可以用校时电路进行校时,校分,校秒。扩展电路必须在主体电路正常运行的情况下才能进行功能扩展。

【关键词】数字时钟,振荡器,计数器,分频器,校时电路,译码器。

【Abstract】

The Digital Clock Circuit System primarily consists of two components--the main circuit and extended circuit. The main circuit assumes the basic functions of a digital clock, while the extended circuit contributes to certain added functions. The oscillator acts as the core of this system, the higher frequency the oscillator affords, more precise timing it will give. The multi-resonance oscillator ,made up of 555 circuit , can produce stable high-frequency impulsive signals, which will provide the clock with fiducial timing. Normal impulsive signals will be gotten by a frenquency divider .When the second-counter counts to 60 , it contributes a carry to the minute-counter, so as the minute-counter to the hour-counter . Worth the whistle , when the hour-counter counts to 12 , it will return to 1 automatically .The output of the Counter will be conveyed to the LED via the Decoder .The error of the timing can be made up with a calibrating circuit ,minute and second available .The extended circuit can achieve its functions on condition that the main circuit works smoothly .

【Key-words】

Digital Clock , oscillator, Counter, frenquency divider, calibrating circuit,Decoder.

多功能数字钟设计

1 方案选择和论证

1.1系统基本方案选择和论证

1.1.1芯片的选择方案和论证:

方案一:

采用89C51芯片作为硬件核心,采用Flash ROM,内部具有4KB ROM 存储空间,能于3V的超低压工作,而且与MCS-51系列单片机完全兼容,但是运用于电路设计中时由于不具备ISP在线编程技术, 当在对电路进行调试时,由于程序的错误修改或对程序的新增功能需要烧入程序时,对芯片的多次拔插会对芯片造成一定的损坏。

方案二:

采用74LS系列的芯片为核心,虽然结构简单,但通俗易懂,不像单片机系统的复杂内部结构。既能更好的了解数字钟的工作原理,也是广大初学者的首选芯片之一。

1.1.2显示模块选择方案和论证:

方案一:

采用LCD液晶显示屏,液晶显示屏的显示功能强大,可显示大量文字,图形,显示多样,清晰可见,但是价格昂贵,需要的接口线多,所以在此设计中不采用LCD液晶显示屏.

方案二:

采用点阵式数码管显示,点阵式数码管是由八行八列的发光二极管组成,对于显示文字比较适合,如采用在显示数字显得太浪费,且价格也相对较高,所以也不用此种作为显示.

方案三:

采用七段数码管以其原理简单、功能单一、界面美观大方等诸多优点,所以选择它作为显示部分。

1.1.3脉冲发生器的选择方案和论证:

方案一:

晶振的频率为32768Hz,因其内部有15级2分频集成电路,所以输出端正好可得到1Hz的标准脉冲。

方案二:

采用由三与非门构成的环形振荡器为核心的电路产生1HZ脉冲信号,但它受温度的影响很大,频率的稳定性不高,所以很难满足设计要求。

方案三:

采用CMOS型555芯片,输入阻抗高达10 数量级,定时长,功耗小,非常适合本电路的设计要求。

数量级,定时长,功耗小,非常适合本电路的设计要求。

1.2 电路设计最终方案决定

综上各方案所述,对此次作品的方案选定: 采用以74LS系列的芯片为核心设计; 555提供时钟脉冲; 七段数码管作为显示。

2 各模块的功能原理及器件选择

2.1 功能要求

基本功能

(1)时的计时要求为“12翻1”,分和秒的计时要求为60进制

(2)准确计时,以数字形式显示时,分,秒的时间

(3)校正时间

扩展功能

(1)定时控制;

(2)自动报整点时数;

2.2设计方案

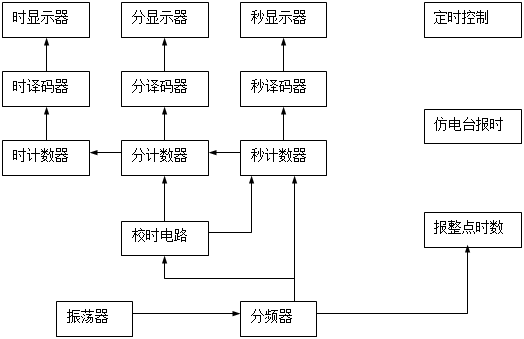

根据设计要求首先建立了一个多功能数字钟电路系统的组成框图,框图如图1所示。

1s

主体电路 扩展电路

图1 多功能数字钟系统组成框图

由图1可知,电路的工作原理是:多功能数字钟电路由主体电路和扩展电路两大部分组成。其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能。

振荡器产生的高脉冲信号作为数字钟的振源,再经分频器输出标准秒脉冲。秒计数器计满60后向分计数器个位进位,分计数器计满60后向小时计数器个位进位并且小时计数器按照“12翻1”的规律计数。计数器的输出经译码器送显示器。计时出现误差时电路进行校时、校分、校秒。扩展电路必须在主体电路正常运行的情况下才能进行扩展功能。

2.3单元电路的设计

数字电子钟的设计方法很多种,例如,可用中小规模集成电路组成电子钟;也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟;还可以利用单片机来实现电子钟等。

在本次设计,电路是由许多单元电路组成的,因此首先必须对各个单元电路进行设计。

2.3.1 主体电路部分

主体电路部分的电路主要由振荡电路、计数电路、显示电路以及校时电路四大部分组成。下面将对各部分电路进行设计。

2.3.2 振荡电路

(1)振荡器

振荡电路由振荡器和分频器产生 1Hz时钟脉冲和扩展部分所需的频率,下面对振荡器进行介绍。

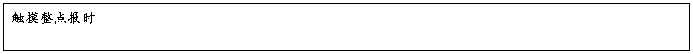

振荡电路的种类较多,这里采用由555 定时器构成的多谐振荡电路来产生,其原理图可参见图2。振荡电路的输出为方波,其主要参数为频率和占空比。由于分频电路采用边沿触发,因此对方波信号的占空比并没有严格要求。根据设计要求,振荡电路输出方波的频率为10Hz,周期等于0.1s。根据振荡周期的计算公式:T=T1+T2=(R1+2R2)C1ln2 可以确定振荡电路中各元件的参数。 先确定电容值,选取C1=0.1μF,则取R2=510kΩ,则R1=409kΩ,可由一只390kΩ 的固定电阻和一只47kΩ 精密可调电阻构成。通过调节精密可调电阻的大小来获得较为精确的输出信号频率。确定了各元件的参数以后,就可以得到振荡电路原理图。

图2 555振荡器

数字秒表的计时精度取决于振荡电路的输出信号频率精度,而振荡电路的输出信号频率精度取决于电路元件参数的精度。所示振荡电路中的电阻、电容的参数易受温度等外部因素的影响,因此很难获得很高的频率精度。在精确计时的电子表中,一般采用由石英晶体构成的振荡器。

(2)分频器

分频器的作用是将由石英晶体产生的高频信号分频成基时钟脉冲信号和扩展部分所需的频率。在此电路中,分频器的功能主要有两个:一是产生标准脉冲信号;二是功能扩展电路所需的信号,如仿电台用的1KHz的高频信号和500Hz的低频信号等。选用3片中规模集成电路计数器74LS90可以完成以上功能。因每片为1/10分频,3片级联则可获得所需要的频率信号,即第1片的Q0端输出频率为500Hz,第2片的Q3端输出为10Hz,第3片的Q3端输出为1Hz。

2.3.3计数电路

分和秒计数器都是模数M=60的计数器,其计数规律为00-01-...-58-59-00...选74LS92作十位计数器,74LS90作个位计数器,再将它们级联成模数M=60的计数器。

时计数器是一个“12翻1”的特殊进制计数器,即当数字钟运行到12时59分59秒,秒的个位计数器再输入一个秒脉冲时,数字钟自动显示为01时00分00秒,实现日常生活中习惯用的计时规律。

下面将分别介绍60进制计数器和“12翻1”小时计数器。

(一)60进制计数器

电路如图3所示:

图3 六十进制计数器

电路中,74LS92作为十位计数器,在电路中采用六进制计数;74LS90作为个位计数器在电路中采用十进制计数。当74LS90的14脚接振荡电路的输出脉冲1Hz时74LS90开始工作,它计时到10时向十位计数器74LS92进位。

下面对电路中所用的主要元件及功能介绍。

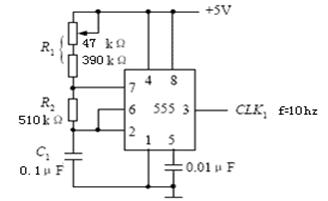

① 十进制计数器 74LS90

74LS90是二—五—十进制计数器,它有两个时钟输入端CPA和CPB。其中,CPA和 组成一位二进制计数器;CPB和

组成一位二进制计数器;CPB和 组成五进制计数器;若将

组成五进制计数器;若将 与

与 相连接,时钟脉冲从

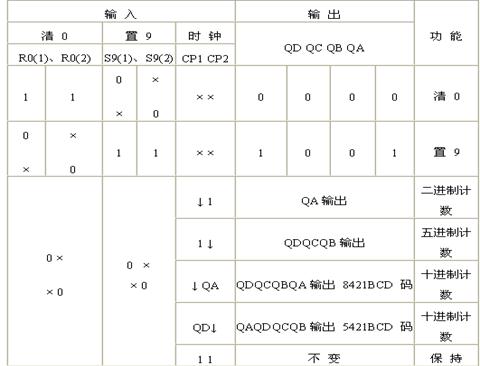

相连接,时钟脉冲从 输入,则构成了8421BCD码十进制计数器。74LS90有两个清零端R0(1)、R0(2),两个置9端R9(1)和R9(2),其BCD码十进制计数时序如表1, ,二—五混合进制计数时序如表2,74LS90的管脚图如图4。

输入,则构成了8421BCD码十进制计数器。74LS90有两个清零端R0(1)、R0(2),两个置9端R9(1)和R9(2),其BCD码十进制计数时序如表1, ,二—五混合进制计数时序如表2,74LS90的管脚图如图4。

图4 74LS90的管脚图

表1 BCD码十进制计数时序 表2 二—五混合进制计数时序

② 异步计数器74LS92

② 异步计数器74LS92

所谓异步计数器是指计数器内各触发器的时钟信号不是来自于同一外接输入时钟信号,因而触发器不是同时翻转。这种计数器的计数速度慢。一异步计数器 74LS92是二—六—十二进制计数器,即 和

和 组成二进制计数器,

组成二进制计数器, 和

和 在74LS92中为六进制计数器。当

在74LS92中为六进制计数器。当 和

和 相连,时钟脉冲从

相连,时钟脉冲从 输入,74LS92构成十六进制计数器。74LS92的管脚图如图5,计数功能表如图6。

输入,74LS92构成十六进制计数器。74LS92的管脚图如图5,计数功能表如图6。

图5 74LS92的管脚图

图6 74LS92 计数功能表

(二) “12翻1”小时计数器电路

图7 “12翻1”小时计数器电路

(1) 电路如图7所 示

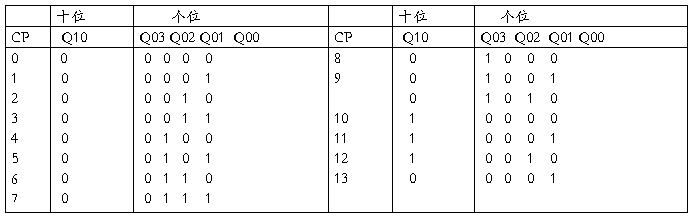

“12翻1”小时 计数器是按照“01—02—03—04—05—06—07—08—09—10—11—12—01”规律计数的,计数器的计数状态转换表如表3所示。

表3“12翻1”小时计时时序

(二)电路的工作原理

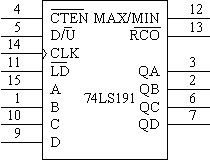

由表4可知:个位计数器由4位二进制同步可逆计数器 74LS191构成,十位计数器由双D触发器74LS74构成 ,将它们组成 “12翻1”小时计数器。

由表可知:计数器的状态要发生 两次跳跃:一是:计数器计到9,即个位计数器的状态为 =1001后,在下一计数脉冲的作用下计数器进入暂态1010,利用暂态的两个1即

=1001后,在下一计数脉冲的作用下计数器进入暂态1010,利用暂态的两个1即 使个位异步置0,同时向十位计数器进位使

使个位异步置0,同时向十位计数器进位使 =1;二是计数到12后,在第13个计数脉冲作用下个位计数器的状态应为

=1;二是计数到12后,在第13个计数脉冲作用下个位计数器的状态应为 =0001,十位计数器的

=0001,十位计数器的 =0。第二次跳跃的十位清“0”和个位置“1”的输出端

=0。第二次跳跃的十位清“0”和个位置“1”的输出端 、

、 、

、 来产生。对电路中所用的主要元件及功能介绍。

来产生。对电路中所用的主要元件及功能介绍。

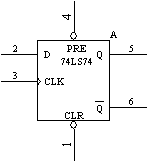

① D触发器74LS74

在电路中用到了D触发器74LS74,74LS74的管脚图如图8。

图8 74LS74的管脚图

下面将介绍一些有关触发器的内容:

触发器,它是由门电路构成的逻辑电路,它的输出具有两个稳定的物理状态(高电平和低电平),所以它能记忆一位二进制代码。触发器是存放在二进制信息的最基本的单元。按其功能可为基本RS触发器触、JK触发器、D触发器和T触发器。

这几种触发器都有集成电路产品。其中应用最广泛的当数JK触发器和D触发器。不过,深刻理解RS触发器对全面掌握触发器的工作方式或动作特点是至关重要的。事实上,JK触发器和D触发器是RS触发器的改进型,其中JK触发器保留了两个数据输入端,而D触发器只保留了一个数据输入端。D触发器有边沿D触发器和高电平D触发器。74LS74为一个电平D触发器。

② 计数器74LS191

74LS191的管脚图如图9。

图9 74LS191的管脚图

2.3.4 校时电路

(一)电路如图10所示

图10 校时电路

(二)电路的工作原理

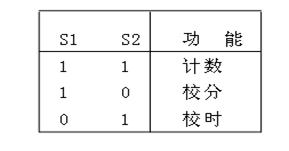

校时电路的作用是:当数字钟接通电源或者出现误差时,校正时间。校时是数字钟应具有的基本功能。一般电子表都具有时、分、秒等校时功能。为了使电路简单,在此设计中只进行分和小时的校时。校时有“快校时”和“慢校时”两种,“快校时”是通过开关控制,使计数器对1Hz校时脉冲计数。“慢校时”是用手动产生单脉冲作校时脉冲。图中S1校分用的控制开关,S2为校秒用的控制开关,它们的控制功能如表4所示,校时脉冲采用分频器输出的1Hz脉冲,当S1或S2分别为“0”时可以进行“快校时”。如果校时脉冲由单次脉冲产生器提供,则可以进行“慢校时”。

表4校时开关的功能

(三)对电路中所用的主要元件及功能介绍

在此电路中,用到的元器件有两块四2输入与非门74LS00 、一块六反相器74 LS04、两个电容、两个电阻以及两个开关。

四-2输入与非门74LS00

集成逻辑门是数字电路中应用十分广泛最基本的一种器件,为了合理的使用和充分利用其性能,必须对它的主要参数和逻辑功能进行测试。74LS00与非门的主要参数为:

输出高电平:指与非门有一个以上输入端接地或接低电平时的输出电平值。

输出低电平:指与非门的所有输入端均接高电平时的输出电平值。

开门电平:指与非门输出处于额定低电平时允许输入高电平的最小值。

关门电平:指与非门输出处于高电平状态时允许输入低电平的最大值。

电压传输特性:是指门的输出电压随输入电压而变化的曲线,由它可以得到门电路的输出高电平、输出低电平、关门电平和开门电平等。

低电平的输出电源电流;是指输入所有端都悬空,输出端空载时,电源提供器件的电流。

高电平输出电源电流:是指输出端空载,每个门各有一个以上的输入端接地,电源提供给器件的电流。

低电平输入电流:是指被测输入端接地,其余输入端悬空时,由被测输入端流出的电流值。

高电平输入电流:指被测输入端接高电平,其余输入端接地,流入被测输入端的电流值。

扇出系数:门电路能驱动同类门的个数,它是衡量门电路负载能力的一个参数,TTL与非门有两种不同性质的负载,即灌电流负载和拉电流负载,因此有两种扇出系数。即低电平扇出系数和高电平扇出系数。

2.3.5译码与显示电路

(一)电路如图11所示

图11 译码与显示电路

(二)电路的工作原理

译码是编码的相反过程,译码器是将输入的二进制代码翻译成相应的输出信号以表示编码时所赋予原意的电路。常用的集成译码器有二进制译码器、二—十制译码器和BCD—7段译码器、显示模块用来显示计时模块输出的结果。

(三)对电路中的主要元件及功能介绍

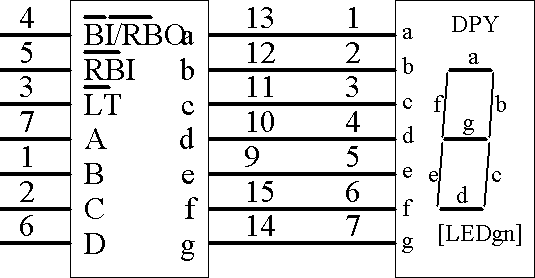

(1)译码器74LS48

译码器是一个多输入、多输出的组合逻辑电路。它的工作是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数字分配,存储器寻址和组合控制信号等。译码器可以分为通用译码器和显示译码器两大类。在电路中用的译码器是共阴极译码器74LS48,用74LS48把输入的8421BCD码ABCD译成七段输出a-g,再由七段数码管显示相应的数。 74LS48的管脚图如图12。在管脚图中,管脚LT、RBI、BI/RBO都是低电平是起作用,作用分别为:

LT为灯测检查,用LT可检查七段显示器个字段是否能正常被点燃。

BI是灭灯输入,可以使显示灯熄灭。

RBI是灭零输入,可以按照需要将显示的零予以熄灭。BI/RBO是共用输出端,RBO称为灭零输出端,可以配合灭零输出端RBI,在多位十进制数表示时,把多余零位熄灭掉,以提高视图的清晰度。也可用共阴译码器74LS248,CD4511。

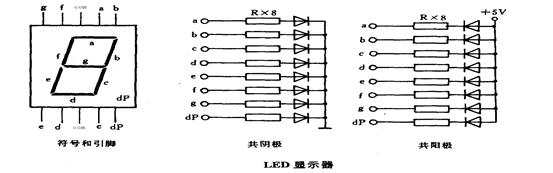

(2)LED显示器

通常所说的LED显示器由7个发光二极管组成,因此也称之为七段LED显示器,其排列形状如图所示。显示器中还有一个圈点型发光二极管(在图中用dp表示),用于显示小数点。通过七个发光二极管亮暗的不同组合,可以显示多种数字、字母以及其它符号。

LED显示器中的发光二极管共有两种连接方法:

·共阳极接法

把发光二极管的阳极连在一起构成公共阳极。使用时公共阳极com接+5V。阴极端输入低电平的段发光二极管导通点亮,输入高电平的则不点亮。

·共阴极接法

把发光二极管的阴极连在一起构成公共阴极。使用时公共阴极com接地,阳极端输入高电平的段发光二极管导通点亮,输入低电平的则不点亮。

图12 74LS48的管脚图

(3)七段LED显示器的工作原理

七段LED显示器需要由驱动电路驱动。在七段LED显示器中,共阳极显示器,用低电平驱动;共阴极显示器,用高电平驱动。点亮显示器有静态和动态两种方式:。

①静态显示器

所谓静态显示,就是当显示器显示某一字符时,相应段的发光二极管恒定地导通或截止。这种显示方法的每一位都需要有一个8位输出口控制。

静态显示器的优点是显示稳定,在发光二极管导通电流一定的情况下,显示器的亮度高。控制系统在运行过程中,仅仅在需要更新显示内容时,CPU才执行一次显示更新子程序。这样大大节省了CPU的时间,提高了CPU的工作效率;缺点是位数较多时,所需的I/O口太多,硬件开销太大。

②动态显示器

所谓动态显示就是一位一位地轮流点亮各位显示器(扫描),对于显示器的每一位而言,每隔一段时间点亮一次。在同一时刻只有一位显示器在工作(点亮),利用人眼的视觉暂留效应和发光二极管熄灭时的余辉效应,看到的却是多个字符“同时”显示。显示器亮度既与点亮时的导通电流有关,也与点亮时间和间隔时间的比例有关。调整电流和时间参数,可实现亮度较高且较稳定的显示。

动态显示器的优点是节省硬件资源,成本较低。但在控制系统运行过程中,要保证显示器正常显示,CPU必需每隔一段时间执行一次显示子程序,占用CPU大量时间,降低了CPU的工作效率,同时显示亮度较静态显示器低。

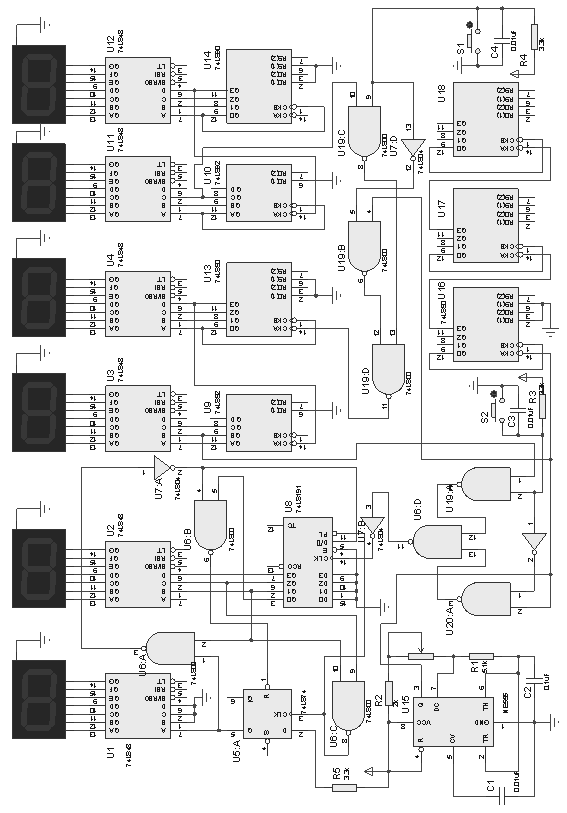

主体电路部分是由上面的以上的各个单元电路组成的,电路图见附件

2.4 主要设备及器件

3 结果分析

经过精心的准备,我们组员用了半天的时间将焊板以及元器件用导线连接起来。但在我们连线成功后,接通电源后发现共阴极LED显示管没有亮,经过检查我们没有把3号和8号引脚接地,如果是共阳极那就是将这两脚接电源。但是接好之后我们发现驱动电路的过程中发现数码管不能正常显示的状况,经检验发现主要是由于接触不良的问题,其中包括线的接触不良和芯片的接触不良,在实验过程中,数码管有几段二极管时隐时现,有时会消失.用5V电源对数码管进行检测,一端接地,另一端接触每一段二极管,发现二极管能正常显示的,再用万用表欧姆档检测每一根线是否接触良好,在检测过程中发现有几根线有时能接通,有时不能接通,把接触不好的线重新接过后发现能正常显示了。当我们改正错误后,我们的LED数码显示管灯亮了,可是发现新的问题了:我们的六个显示器有两个只能显示号管脚;我们的秒指针没有变化;我们的开关没有起到调节作用。

为了解决这些问题,我们从信号的发生装置NE555的输出开始检查,我们发现NE555三号脚可以发出脉冲,可是在分频电路的输出端没有收到连续的信号脉冲,我们首先排除了芯片坏的可能性,在检查分频电路时也没有发现虚焊,假焊和错焊的情况,于是我们和兄弟组的人员讨论,结果他们也发现错误。我们暂时把这个问题搁置继续从分频电路的输出1Hz的90芯片出发,我们发现自己在焊接时把74LS90和74LS92芯片的接地端全部以74LS90的方式接地了即将所以芯片的2号脚和6号脚接地了,而74LS92的只有6号脚接地。我们马上改正后显示管马上就显示正常了。我们继续检查,当我们检查到校时电路时,我们发现在与74LS00芯片相接的3.3K电阻,按钮开关和0.01uF电容的接地端出现错误,开关没有接上去。我们改正后,我们的校时电路可以正常工作了。我们的问题只剩下秒表没有脉冲了,终于我们发现了其中一块芯片74LS90坏了。我们更换了芯片,并且我们调节好滑动变阻器的电阻,检测到74LS90输出的是1Hz的信号电压时,我们接通了电源,调试成功。

4 设计小结

通过本次课程设计,我受益匪浅。这是我进大学来的第一次课程设计,在这个过程中我不仅将我所学的理论在实践中进行了检验,也切切实实地提高了我分析问题、解决问题的能力,增强了我对电子技术的理解和应用能力。

在设计中,我也曾遇到过很多不懂的地方,除请教老师和同学外,根据课题需要,我学会了上网去搜索相关的文献资料和专业知识来获取问题的答案,同时了解了不少芯片以及电子元器件的使用方法、特性,学会了使用电烙铁,万用表测量器件好坏以及分析检测电子电路的问题以及简单的维修技术,理解了数码管的工作原理,掌握了电路图、PCB图的设计方法,学会电路的仿真安装与调试,这些都会对我以后的学习有很大的帮助。此外,我更深刻的体会到团结合作精神的可贵,三个臭皮匠顶上一个诸葛亮,在设计中我们组的四个成员相互交流,相互帮助,坦诚的交换意见,一起为作好设计为目标而努力,大家一起讨论各种方案及各种环节要注意的问题,还记得第一次调试电路板失败时,大家并没有气垒,而是相互鼓励地分工进行电路的检查,终于有志者事竟成,最后我们成功地完成了此次设计。

参考文献

附录一

1、数字电子技术(第二版),江晓安等编著,西安电子科技大学出版社

2、数字电子技术基础(第四版),阎石主编,高等教育出版社

3、数字电路设计与制作,汤山俊夫(日)著,科学出版社

4、模拟及数字电子技术实验教程,徐国华等编著,北京航空航天大学出版社

数字钟设计总图