数字电路课程设计

——数字秒表

按照数字电路课程设计的要求,我们试验小组于1月4日开始着手,经过5小时的设计、连接与调试,最终调试成功,又经过几次的线路优化和改进,达到了令人满意的效果。

本次电子线路课程设计,将设计并制作出一个简单的电子秒表,来加深对各种电子器件功能的理解.

功能简介:

此秒表的计时精确度为0.01秒,记时范围为00:00~59:99秒.在此基础上,我们又在电路中加了一个与秒记时位同步的二极管,其可以随着秒记时位的变动来闪烁.各种控制功能如下,

启动:此功能来控制计时的开始,并且在计时暂停状态时可用来继续在先前计时的基础上进行累计计时.

暂停:此功能可在计时结束时来控制计时停止.

清零:此功能用来把秒表的计时置为零,为下次计时做好准备.

按键分配及其功能:

此电路共使用按钮开关和接触开关各一个:按钮开关用来控制启动/暂停功能,当按一下开关时电路启动,开始计时.再次按开关时停止计时,此时显示器显示所计时间.若在暂停状态再次按此开关,电路在先前计时的基础之上继续计数。

主要元器件:

元器件名称: 数目:

74LS163四位二进制同步计数器 4

74LS00四2输入与非门 4

CD4511七段译码器 4

LED七段显示器 4

555器件 1

电阻 8

电容 1

发光二极管 1

工作原理:

对电路设计要求进行细致的分析便可知,此秒表总体可分为三个模块:模6000计数器、100Hz脉冲信号发生器和对各种功能的控制线路.模6000计数器可以用同步计数器74LS163级联而成,然后通过CD4511七段译码器译码,最终由七段显示器显示计数结果;100Hz脉冲信号发生器可以由555定时器构成多谐震荡器来实现;控制线路可以通过计数器的各种功能脚来实现,也可以通过控制脉冲的通断等方式来达到控制目的.

电路设计方案:

⑶. 模6000计数器:

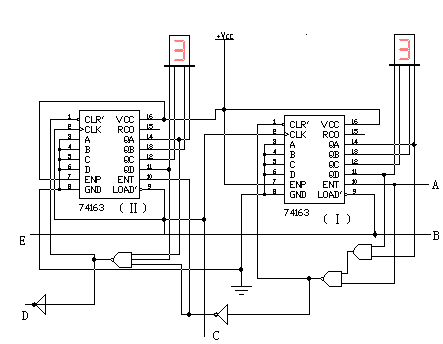

对于计数器,我们采用四片74LS163通过同步级联(既都使用同一脉冲信号)的方式实现(其部分电路图如下),低位(Ⅰ)通过QA和QB端来控制自身的清零,既当计数到9(其BCD码为1001)时清零,在下个脉冲到来时进行清零.同时,其控制清零端取反之后还要控制其高位变为计数状态,以向高位进位;对于高位(Ⅱ),也采用QA和QB端来进行控制清零,与低位不同的是控制端上要加上低位的清零控制信号,达到只有在本位为9和低位为9同时满足的情况下才清零;端口A和端口B预留做控制线路使用,端口C加脉冲信号,端口D实现向(Ⅱ)的高位输出控制信号,端口E来连接另外两个74LS163的LOAD’脚.由于另外两个计数器可采用同样的方式连接,且工作原理与此两位计数器基本相同,故在此不再进行说明.

对于计数器,我们采用四片74LS163通过同步级联(既都使用同一脉冲信号)的方式实现(其部分电路图如下),低位(Ⅰ)通过QA和QB端来控制自身的清零,既当计数到9(其BCD码为1001)时清零,在下个脉冲到来时进行清零.同时,其控制清零端取反之后还要控制其高位变为计数状态,以向高位进位;对于高位(Ⅱ),也采用QA和QB端来进行控制清零,与低位不同的是控制端上要加上低位的清零控制信号,达到只有在本位为9和低位为9同时满足的情况下才清零;端口A和端口B预留做控制线路使用,端口C加脉冲信号,端口D实现向(Ⅱ)的高位输出控制信号,端口E来连接另外两个74LS163的LOAD’脚.由于另外两个计数器可采用同样的方式连接,且工作原理与此两位计数器基本相同,故在此不再进行说明.

⑵.100Hz脉冲信号发生器:

⑵.100Hz脉冲信号发生器:

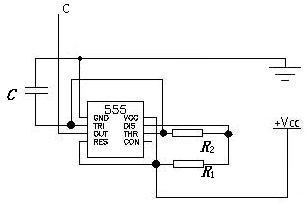

脉冲信号发生器可由555定时器构成多谐震荡器来实现,其电路图如右所示。图中的C端口接计数电路图中的C端。通过查找相关材料可知,此电路产生脉冲信号的频率为 由于材料有限,我们使用了比较接近要求的电阻和电容,来大致实现秒表的计时功能。

由于材料有限,我们使用了比较接近要求的电阻和电容,来大致实现秒表的计时功能。

⑶.控制线路:

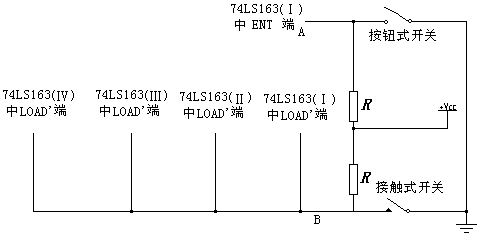

控制线路的原理图如下所示,图中的A和B端口分别接计数电路图中的A和B端口,当按钮开关断开时,计数器(Ⅰ)的ENT端为高电位,既计数器处于计数状态,秒表进行计数;当按钮开关闭合时,ENT端为低电位,计数器停止计数,由于计数器(Ⅰ)停止计数,则后续计数器也停止计数,既秒表处于暂停状态;若暂停时在断开按钮开关,可知秒表继续记时。当接触式开关接触时,B端点为低电位,此时每个计数器的LOAD’端有效,由于每个计数器上的脉冲依然存在,所以计数被置为零,实现了清零的功能。

控制线路的原理图如下所示,图中的A和B端口分别接计数电路图中的A和B端口,当按钮开关断开时,计数器(Ⅰ)的ENT端为高电位,既计数器处于计数状态,秒表进行计数;当按钮开关闭合时,ENT端为低电位,计数器停止计数,由于计数器(Ⅰ)停止计数,则后续计数器也停止计数,既秒表处于暂停状态;若暂停时在断开按钮开关,可知秒表继续记时。当接触式开关接触时,B端点为低电位,此时每个计数器的LOAD’端有效,由于每个计数器上的脉冲依然存在,所以计数被置为零,实现了清零的功能。

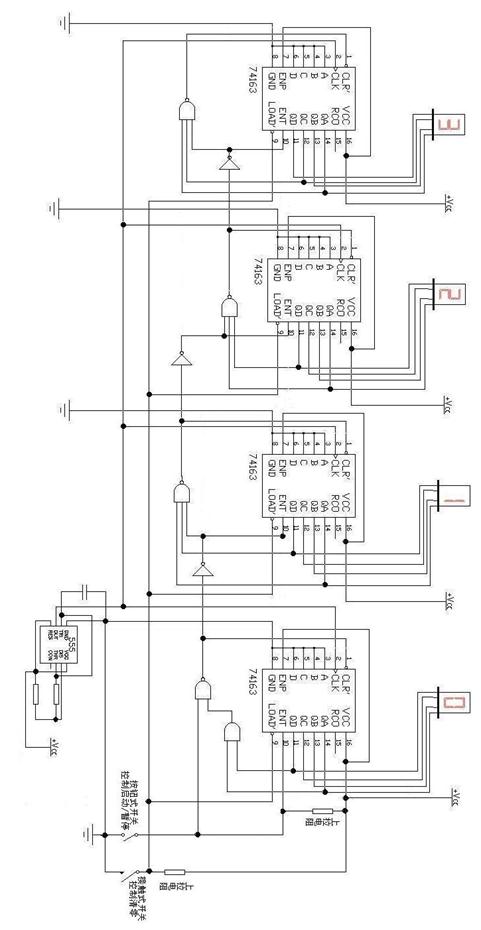

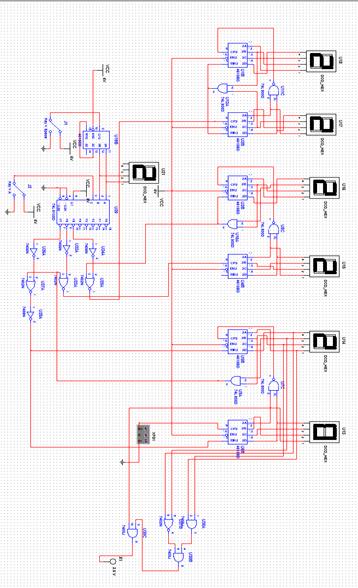

⑷. 完整电路图:

最终能实现所要求的电路图如下,

设计感想:

在此次数字电路课程设计中,我们并不是一帆风顺,起先以为在EWB上仿真通过就可以轻松的连线了 ,其实不然,连线和调试才是最重要的环节。在连线过程中不仅仅需要考虑每一个元器件的摆放位置而使的连线变的方便容易,同时还需要考虑其美观性,而调试更是一项艰苦的工作。我们在调试中就遇到了许多困难,例如当我们第一次接通电源后,发现最低位是1、2、3、4、5、6、7、8、9、0循环,但在0和1之间却要间隔几秒,经过半个小时的调试也没能发现原因,最后我们决定更换器件,就在这时,我们发现74LS00的八脚没有接地,就这样一个问题迎刃而解了;在对清零模块的调试中,经过反复的试验和论证,最终我们选择了采用置数的方式,这样就大大的减少了电路的复杂性;在对暂停模块的设计中,我们也有两套方案,一种是切断CP脉冲,另一种是利用74163器件自身带的保持功能,最后我们采用了后者,这样可以使电路运行更稳定。总之,我们坚定步伐,稳扎稳打,将困难逐个解决,最后达到令自己满意的效果。

通过这次课程设计,我学到了很多东西,但也又很多地方值得我去思考。首先,应认识到自己在知识点的掌握方面上还存在不足,需要继续学习,动手能力还比较弱,实践中需要的技巧有待提高和完善;其次,我们在进行研究和探索问题的过程中,需要十足的耐心和认真负责的工作态度。因为在对有些现象的探索过程中,常常漫长而又乏味,容易使人产生烦躁情绪,进而对工作产生不利影响,而且,再整个过程中,任何一个稍不留神的马虎都可能产生意想不到的结果,培养认真负责的工作态度显的尤为重要;再有则应是对我们团队精神的要求,由于在整个过程中由你和自己的搭档共同努力,所以彼此间配合的挈合好坏十分重要,过分的主观主义和推卸工作的态度都是不可取的,而应多进行换位思考,作到与队友相互关心,相互体谅,以最积极的方式投身到工作中去。

20##年1月7日

第二篇:数电实验课程设计总结报告(电子表)

数字电路课程设计

数字定时器:

课程设计任务书:

1)集成数字定时器

2)技术指标

1、设计一个数字定时器,要求它具有数字钟的功能,又可以按预定时刻发出控制信号对被控对象实施开关控制

2、时钟功能:具有24小时计时方式,显示时、分、秒。计时范围要求自00点00分00秒到23点59分59秒

3、要求具有校时电路,可对小时、分、秒分别校准。

4、可以同时设置四个以上的预定时刻,时刻的预选以5分钟为单位。

5、被控对象在达到预选时刻后,电铃连续响10秒,而监听器在10秒内断续鸣叫5次,即想一秒停一秒。

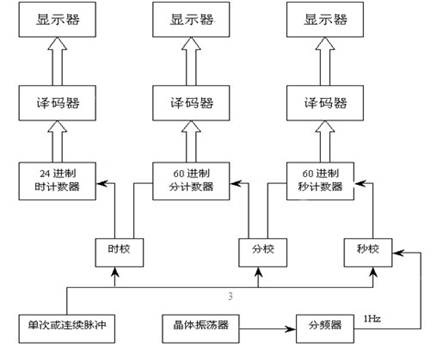

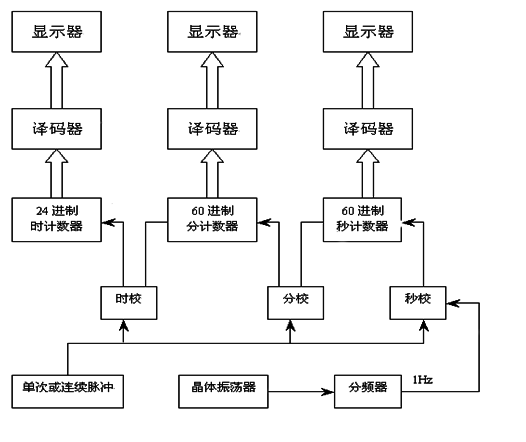

集成数字定时器的组成和工作原理

数字定时器一般由振荡器、分频器、计数器、译码器、显示器及部分扩展电路等组成,其基本逻辑功能框图如下所示:

数字电子钟的基本组成:

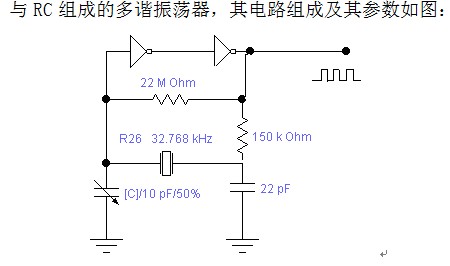

振荡器

振荡器是数字电子钟的核心,其作用是产生一个频率标准,即时间标准信号,然后再由分频器生成秒脉冲,所以,振荡器频率的精度和稳定度就基本决定了数字电子钟的准确度,为产生稳定的时间标准信号,一般采用石英晶体振荡器。如果精度要求不是很高的话我们可以采用由集成逻辑门与RC组成的时钟源振荡器。一般而言,选用石英晶体振荡器所选用的晶振频率为32768Hz,再通过15级2分频集成电路得到1Hz的标准秒脉冲。

分频器

振荡器产生的时标信号频率很高,要使它变成用来计时的“秒”信号,需要若干级分频电路,分频器的级数和每级分频次数要根据时标信号的频率来决定。其功能主要有两个:一是产生标准秒脉冲信号,二是提供功能扩展电路所需的信号。

计数器

有了“秒”信号了就可以根据60秒为一分,60分为一小时,24小时为一天的进制,分别选定没“秒”、“分”、“时”的计数器。从这些计数器的输出可得到一分、一小时、一天的时间进位信号。在秒计数器钟因为是60进制通常用两个十进制计数器的集成片组成,其中秒个位是十进制的、十位是6进制的。可采用反馈归零法变“秒”十位为6进制,实现秒的60进制,同样,分计数器的与秒的一样,只是时计数器里需要变成24进制,也用反馈归零法实现。

译码器及显示器

因为计数器全部采用8421BCD码十进制计数集成芯片,所以“秒”、“分”、“时”的个位和十位都有四个状态输出端(Qa、Qb、Qc、Qd)。将这些输出端,接至译码电路,就可产生驱动七段数码显示器的信号。常用的集成芯片有74LS48和4511等。

校时电路

当数字钟接通电源或者计时出现误差时需要校正时间,校时电路的要求是:在小时校正时不影响分和秒的正常计数;在分校时时不影响时和秒的正常计数。

方案的实现:

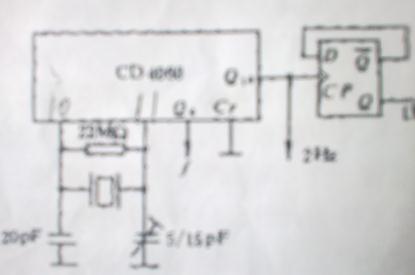

秒脉冲发生器的设计:

本设计采用CD4060CMOS集成电路十四位二进制计数器/分频器来实现。

电路由两部分组成。2hz信号在经过一级D触发器构成的二分频电路就获得了1HZ的秒脉冲。

计数器的设计:

分和秒计数器都是模数为60的计数器,可以选用74LS90芯片级联组成模数为60的计数器。也可以用4518双重BCD加法计数器芯片,采用反馈归零法实现秒60进制,而时计数器是一个二十四进制的特殊进制计数器,其要求是“24翻一”,计数规律是:当数字时钟运行到“23时59分59秒”时计数器再加一个秒脉冲时数字钟自动运行到“00时00分00秒”,实现日常生活的24小时计数制,在次可以选用74LS74与74LS191来实现,也可以选用4518集成芯片采用反馈归零法完成二十四进制。由于4518使用起来简单,所用的芯片也少故本例采用4518来实现。

校时电路的设计:

由设计的要求可知该电路对校时电路的要求还是比较高的,设计的校时电路中三个控制开关S1,S2,S3分别用来实现“时”、“分”、“秒”的校准,开关处于正常位置分别接高电平,所以“时”、“分”、“秒”计数器按正常计数。当将S1置校时位置时,S1闭合,由分频器送来0.5秒的脉冲信号直接进入“时”计数器,使小时指示每0.5秒计一个字达到快速校时的目的。当“时”校准后,复位开关S1,再按下开关S2置“校分”位置,和校时的原理一样,将0.5秒的脉冲信号接入“分”计数器的CP端使“分”快速计数。当分校到合适的数字后,复位开关S2,数字钟进入正常走时状态。“秒”校准开关S3控制着一RS触发器(可以选用74LS74双D触发器集成片中的一D触发器来实现RS的功能)的状态。当S3置一“正常”位置时,触发器置“1”, 端输出低电平,关闭D8,Q端输出高电平,使D7打开,“秒”信号正常进入“秒”计数器,使时钟正常计时。若开关S3置于“秒校”位置,则触发器置零,Q端输出低电平,封锁D7,“秒”信号不能通过,而 端输出高电平,打开D8,使0.5秒的信号进入“秒”计数器,此时“秒”计数器快速计时。待“秒”校准后,松开复位S3,使其恢复置正常位置。其中周期为0.5秒的脉冲信号取自分频器。另外开关S1、S2、S3、在搏动时可能会产生抖动的现象,为了减少这种现象的发生可以在每个开关的两端各接一个电容以缓解抖动。

电路设计好之后先通过仿真来验证电路的可行性:

经仿真之后,进行安装与调试:

在实验面板上组装数字式电子钟时,应严格按图连接引脚,注意走线整齐,布局合理,器件的悬空端、清“0”端,置“1”端要正确处理。首先对照图对应安装好各元器件。并通过检查确认没问题才进行下一步操作。另外芯片、数码管、三极管、蜂鸣器……的安装一定要注意极性。千万别装反了。插拔芯片时要注意用力均匀,避免芯片管脚在插拔过程中变弯、折断。实践证明,新安装的电路板往往难以达到预期的效果,这是因为在设计的时候不可能周全地考虑元件的误差、器件参数的分散性、寄生参数等各种各样的客观因素。此外,电路板的安装中仍存在有可能没有查出来的错误。需要通过电路板的整体测试与调整,才可发现设计方案中的不足,之后查出电路安装中的错误并采取措施加以改进和纠正,就可以使之达到预定的技术要求。

电路安装完毕后,必须在不通电的情况下,对电路板进行认真细致的检查,以便纠正安装错误。检查应特别注意:元器件引脚之间有无短路、断路。IC座是否插反。电源的正、负极性有没有接反,正、负极之间有没有短路现象,电源线、地线是否接触良好。

设计心得及体会

这次实验总体来说完成的比较顺利,虽然中间也有一些考虑不周的小失误,但总体还成成功完成了实验。

本次我们组所选择的实验题目是一个纯数电的题目。相对于模电题目来说,这个题目所使用的芯片较多,超过以往历次实验,使用了10片以上的芯片,如此多的芯片导致线路连接起来十分复杂,使用了至少100根导线连接,复杂的电路要求十分准确的连接线路,在初次连接时就要确保正确,一个小小的连接错误就可能使整个系统失效,并且检查起来十分困难。我们在初次连接时使用了分块连接分块检查功能的方法,每连接一部分电路就验证一次功能,确保电路的正确性。

虽然电路连接很复杂,但是相对于模拟电路,调试起来十分轻松,没有模电各种滤波,系统参数的调节等麻烦。在仿真成功,电路连接正确的情况下,系统经过简单调试,很快工作了起来。但在定时电路中出现了一些小问题,在经过电路修改后,系统正常工作了起来。

这次实验中我们第一次使用所学的知识做了个具有完整功能的系统,虽然功能只与5元的电子表类似,但始终是我们的劳动成果,为我们以后设计更加复杂的系统做好准备。