数字电子技术实验报告

一、实验目的:

1. 掌握TTL逻辑门电路的主要参数意义

2. 掌握TTL逻辑门电路主要参数以及测量方法

3. 通过与非门实现与门、或门、异或门。

二、实验设备;

1. 数字电路实验箱

2. 74LS00

3. 函数发生器、示波器

三、实验原理;

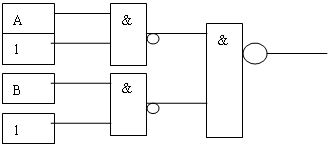

1. 实验室所用电路板中配备有与非门,可以通过各种逻辑运算,从而利用与非门实现与门、或门、异或门等逻辑门电路。

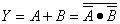

2. Y=A·B= ,从公式可以看出,可以将

,从公式可以看出,可以将 与1接入与非门的两个输入端(输入1的端口悬空即可)。

与1接入与非门的两个输入端(输入1的端口悬空即可)。

3.  ,从公式可以看出可以将A和1接入一个非门(2步骤中已经实现非门),从而得到

,从公式可以看出可以将A和1接入一个非门(2步骤中已经实现非门),从而得到 ,同理可以得到

,同理可以得到 ,然后将

,然后将 和

和 接入与非门的两个输入端,就可得到Y。

接入与非门的两个输入端,就可得到Y。

4. Y=A =

= =

= =

= 。

。

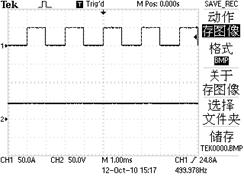

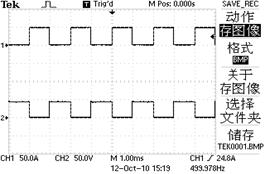

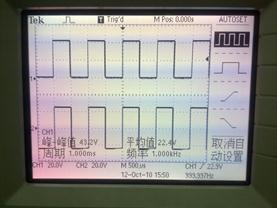

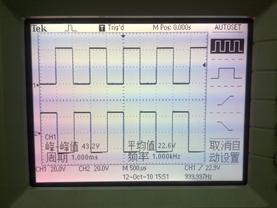

5. 取信号A为方波,峰峰值是5V,偏移量为2.5V,频率为1000Hz,B取为逻辑开关。

四、实验结果图

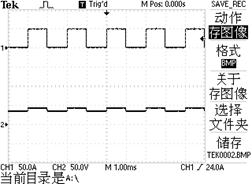

1. 与门

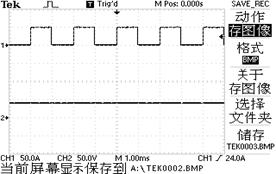

2. 或门

3. 异或门

当B=0时,Y=A =A 当B=1时,Y=A

=A 当B=1时,Y=A =

=

第二篇:数字电子技术课程实验报告

数字电子技术课程

20##-2012学年第一学期

学校:吉林大学应用技术学院

班级:541033

专业:电子信息

学号:20

姓名:秦雪君

一百进制加/减计数器电路的制作

设计目的:

本次实习的内容是数字电子技术课程设计,综合运用EWB技术课程和其它相关课程知识,结合实际,培养,分析和解决简单电路设计的能力。深化,巩固和拓展所学知识。

通过本次实习,熟练掌握了EWB软件的操作技能,并且将所学的数电知识熟练运用到课件设计中,并进行演示所得结果是否与预想一致,实现其电路。

设计步骤:

(1) 查阅资料,了解计数器的组成及其工作原理

(2) 构思电路总框图

(3) 确定元件

(4) 设计电路图

(5) 运用EWB对电路图进行仿真。调试,直到得到所要的效果

(6) 整理总结报告

实验器材:

内容:

(1)设计一个一百进制加/减计数器,利用一个CB555定时器制作一个多谐振荡,使其振荡周期为1s,作为被计数脉冲。

(2)加计数范围为0-99。减计数范围为99-0。计数器输出8421BCD码。

(3)译码、锁存、驱动电路将8421BCD码译成十进制数并驱动七段数码管LED显示。

(4)控制电路能实现:加法计数控制、减法计数控制、加减计数的相互转换控制及保护功能。

(5)计数器在工作过程中,能实现加减互换,并能实现保持、清零、计数的功能

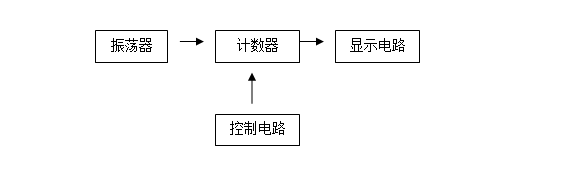

基本原理框图:

要求:

(1)按照设计内容设计十进制加/减计数器。

(2)根据设计内容要求,观察加减计数器的变化。

(3)尽量减小误差。

实验过程:

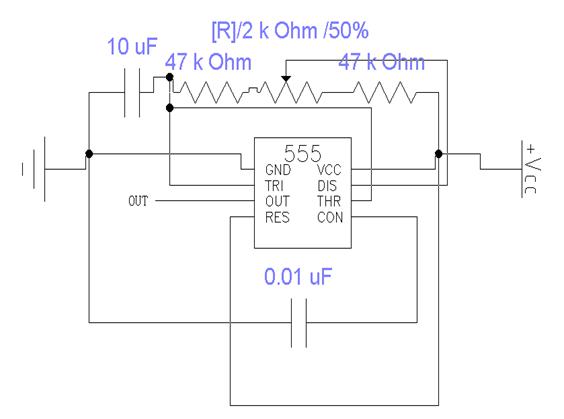

(1)多谐振荡器

利用555定时器连接的多谐振荡器,周期为1s,输出脉冲幅度大于3V小于5V,输出脉冲的占空比q=2/3。

由CB555的特性参数可知,当电源电压取为5V时,在100mA的输出电流下输出电压的典型值为3.3V,所以取VCC=5V可满足对输出脉冲幅度的要求。可知:

q=(R1+R2)/(R1+2R2)=2/3

故得到R1=R2.

又因为

T=T1+T2=(R1+2R2)Cln2=1

若取C=10μF,则代入上式得到

3R1Cln2=1

R1=1/(3Cln2)Ω=48kΩ

因R1=R2,所以取两只47kΩ的电阻与一个2kΩ的电位器串联,即得下图:

计数器:

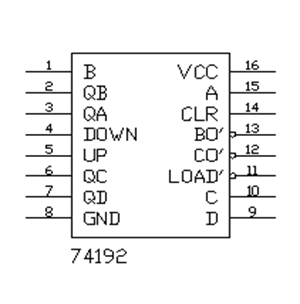

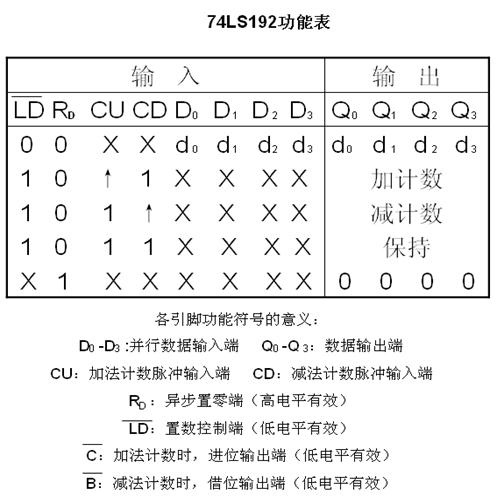

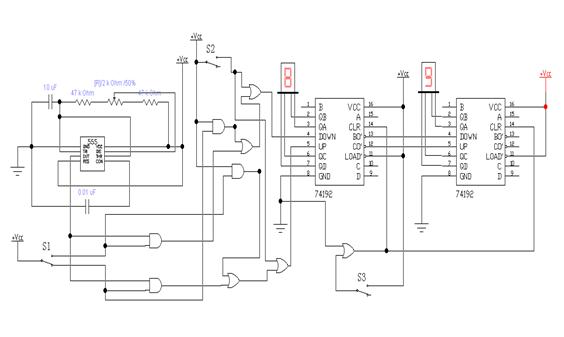

电路里使用了集成器件74LS192,它是可预置的一百进制同步加/减计数器。QA、QB、QC和QD输出组成BCD码,接到数码显示器上。

实验电路图

说明:开关S1控制电路计数加减

开关S2控制电路计数保持

开关S3控制电路计数清零

实验心得

本次实习主要是软件设计和调试,电路较为简单,使用Multisim软件,及EWB软件利用74LS190集成块、555定时器、以及一些逻辑门电路设计成一个简单的100进制加减计数器,并实现了预想的功能:加减计数、计数清零、计数保持。在这次实习中学到了很多东西。

在做这个课程设计前,首先做了很多准备,我先把课本上的重点知识复习了一遍,然后到图书馆查找相关资料,电路设计方面的书籍,设计过程中,用EWB仿真方便很多,不过设计所需芯片在仿真上出现一些问题,一些管脚的位置与实际的不同,仿真调试没达到预期。但我想理论上是绝对没错的,于是直接进行实际接线,分模块调试,接好一片,检查一片,仔细对着管脚图接线,最终达到了预期功能。这让我看到了理论与实践还是存在差别,我们需要在实践中发现错误,并检查错误,提高自己的动手能力和实际解决问题的能力。

电路在设计中遇到了很多问题,有的实验器件没有,只好换其它器件代替,终于在不断地改进中设计成功了。仿真时有时也遇到意想不到的问题,只能求教其他同学,通过同学之间的交流来提升自己,锻炼了自己读电路的能力,了解了一些芯片的功能,同时也让自己的专业技能得到锻炼,为进一步的硬件设计打好基础。通过这次实习,我也知道了团队精神的重要性,相互学习、取长补短,在各方面提高自己的能力。