实验教学说明

1.所有实验的软件设计平台主要是QuartusII 9.1。

2.所有实验的硬件平台可选Cyclone FPGA:EP1C6。

3.上机所有实验项目文档均建立在C:\DXnnn。

nnn为学号后三位数。

4. ▲注:目录、文件名不能有中文字;每个实验单独在DXnnn下建子目录。

共4个实验(Project),即4个子目录。

5.必须符合实验报告给定的格式,即在本教案中添加实验内容,不改变格式。

实验报告完成后,将教学说明和目录删去。正文5号宋体。

▲注:实验报告为word文档,名为DXnnn姓名.doc,中间没有空格。

6.各实验要含输入(图或Verilog程序)、RTL综合电路图和仿真结果等主要

部分的屏幕硬拷贝。每个贴图要清晰、信息要全又没有多余。

7.每位同学要提交实验报告(电子稿),同时提交打印稿或手写稿,

总页数控制在10—16页。课程设计报告提交wly88623390@126.com

8.QuartusII 的操作方法、步骤与及设计内容,参见教材章节。

其余可参考老师提供的电子文档。

青 岛 科 技 大 学

实验报告

实验课程:EDA技术与Verilog实验

姓名: 标准名 学号: 07030100

年级: 07级 专业班级: 电信071

台号: 实验日期: 20##-12-18

自动化与电子工程学院

目 录

实验一 运算电路的设计与仿真. 4

实验二 触发器的设计与仿真. 6

实验三 模15加法计数器的设计与仿真. 8

实验四 3位线性反馈移位寄存器的设计与仿真. 10

实验一 运算电路的设计与仿真

一、实验目的

1.设计一个1位全加器,设计模块分层次。

2. 先设计半加器,再用半加器构成1位全加器。

3.对设计的两层电路分别进行编译综合与仿真分析。

二、实验准备

1.阅读教材第4章有关内容。

2.画出设计的逻辑电路图。

三、实验内容与步骤

1.在自己建立的工作目录下,输入所设计的逻辑电路图。

2.按步骤进行编译综合。

3. 编辑输入波形。

4. 进行仿真和分析。

四、仿真结果及分析

(屏幕硬拷贝图:半加器、全加器电路图、全加器综合RTL图、全加器仿真波形)

(仿真结果简单分析: 一定要对照输入输出波形结果一一进行分析)

▲注:先创建项目,后输入设计文档。

▲注:全加器为顶层模块,必须与创建项目时指定的顶层模块名一致。

半加器另命名,不能与顶层模块名一样。

▲注:画完半加器后,file→create→create symbol生成库模块。

▲注:编辑输入波形前,一定先设置end time:100uS;并且Fit in window。

▲注:仿真前,再全编译一次。

▲注:若有修改,则再全编译一次。

实验二 触发器的设计与仿真

一、实验目的

1.用Verilog设计一个边沿触发器(可选T、RS),要求带有一个异步、一个同步置位或复位端。

2.对设计的触发器进行编译综合、仿真分析。

二、实验准备

1.阅读教材第7章相关内容。

2.用Verilog语言写出设计描述。

。

三、实验内容与步骤

1.在自己建立的工作目录下,编写输入所设计的程序。

2.按步骤进行编译综合。

3. 编辑输入波形。

4. 进行仿真和分析。

四、仿真结果及分析

(屏幕硬拷贝图:Verilog描述、综合RTL电路图、仿真波形)

(仿真结果简单分析: 一定要对照输入输出波形结果一一进行分析)

▲注:先创建项目,后输入设计文档。

▲注:项目的顶层命名 、Verilog文件名、module 定义的模块名三者

必须一致。

▲注:仿真时,注意set和reset只在初始时短时有效一次,

并且不能同时有效。注意是同步还是异步方式。

▲注:编辑输入波形前,一定先设置end time:100uS;并且Fit in window。

▲注:仿真前,再全编译一次。

▲注:若有修改,则再全编译一次。

实验三 模15加法计数器的设计与仿真

一、实验目的

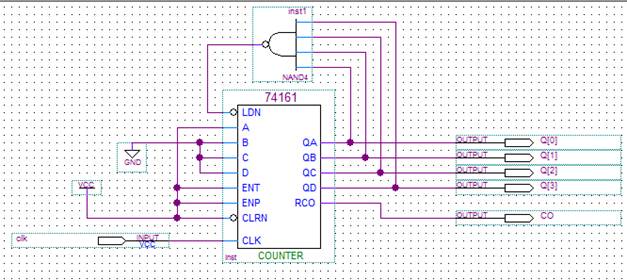

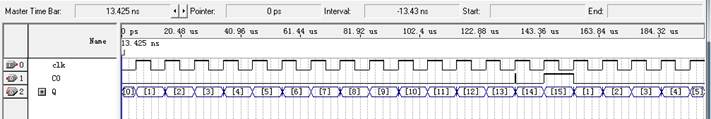

1.用Maxplus2库中的74161模块,设计一个模15加法计数器。

2.对设计的电路进行编译综合、仿真分析。

二、实验准备

1.阅读教材第8章相关内容。

2.画出设计的电路图。

三、实验内容与步骤

1.在自己建立的工作目录下,编写各模块程序,绘制总电路框图。

2.按步骤进行编译综合。

3. 编辑输入波形。

4. 进行仿真和分析。

四、仿真结果及分析

(屏幕硬拷贝图:设计输入、综合RTL电路图、仿真波形)

(仿真结果简单分析: 一定要对照输入输出波形结果一一进行分析)

▲注:先创建项目,后输入设计文档。

▲注:项目的顶层命名 、Verilog文件名、module 定义的模块名三者

必须一致。

▲注:仿真时,注意置数、复位方式。

▲注:编辑输入波形前,一定先设置end time:200uS,Tclk=10uS;

并且Fit in window。

▲注:仿真前,再全编译一次。

▲注:若有修改,则再全编译一次。

实验四 3位线性反馈移位寄存器的设计与仿真

一、实验目的

1.用Verilog设计一个3位线性反馈移位寄存器。

2.对设计的电路进行仿真分析。

二、实验准备

1.阅读教材第8章有关内容。(P200)

2.用Verilog语言设计一个3位线性反馈移位寄存器。

三、实验内容与步骤

1.在自己建立的工作目录下,编写输入所设计的程序。

2.按步骤进行操作和仿真

四、仿真结果及分析

(屏幕硬拷贝图)

▲注:先创建项目,后输入设计文档。

▲注:项目的顶层命名 、Verilog文件名、module 定义的模块名三者

必须一致。

▲注:在操作中间做修改后,一定要再存盘,并全编译一次。

▲注:Project中,不能有多余的文件(如多余的Verilog,描述、多余的波

形文件),若有,将可能导致全编译时加入修改前的中间结果。

▲注:编辑输入波形前,一定先设置end time:10S,Tclk=1S;

Tsignal=0.1S,0.05S。并且Fit in window。

▲注:仿真前,再全编译一次。

▲注:若有修改,则再全编译一次。

▲注:仿真波形输入,初始状态不能为0.

第二篇:eda电子设计使用verilog语言电子琴实验报告

电子设计自动化课程设计报告

院 系: 信息工程学院

专 业: 电子信息工程

学 号:

姓 名:

指导教师:

2013 年 月 日

目 录

1设计目的………………………………………………………3

2题目描述与要求………………………………………………3

3课程设计报告内容……………………………………………3

3.1设计原理与思路……………………………………………3

3.2操作过程……………………………………………………4

3.3设计和调试过程中出现的问题及解决方法………………7

4设计总结和心得体会…………………………………………8

一、课程设计目的

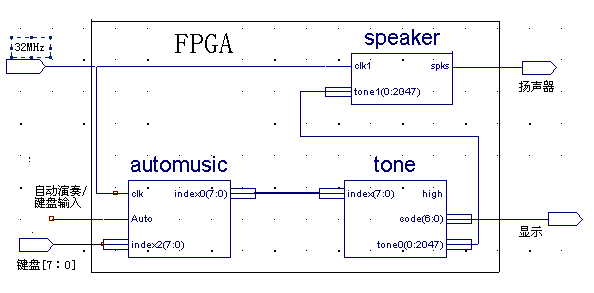

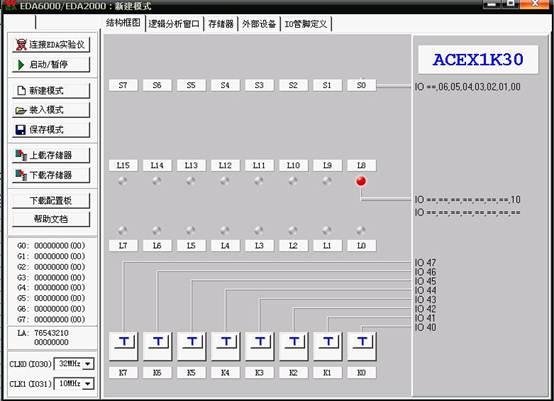

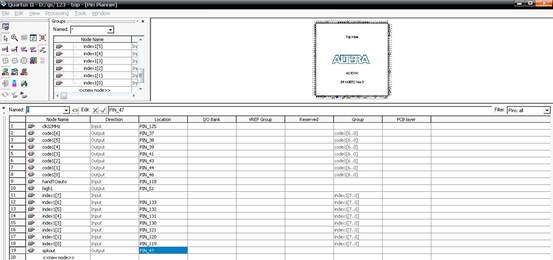

使用VerilogHDL语言进行前端设计,并使用Quaruts软件在实验箱上实现仿真,实现硬件电子琴。电子琴要求有8个音阶,使用外部时钟信号32MHz,能同步显示音阶。

二、课程设计题目描述和要求

题目:简易电子琴的设计

主要功能:(1)设计一个八音电子琴。

(2)由键盘输入控制音响,同时可自动演奏乐曲。

(3)用户可以将自己编制的乐曲存入电子琴,演奏时可选择键盘输入乐曲或者已存入的乐曲。

三、课程设计报告内容

三、课程设计报告内容

3.1设计原理与思路

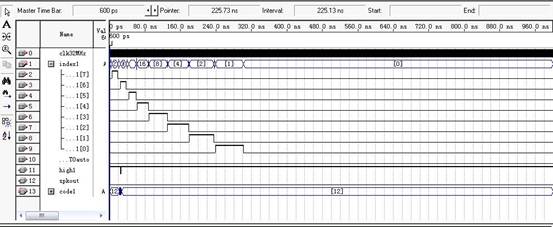

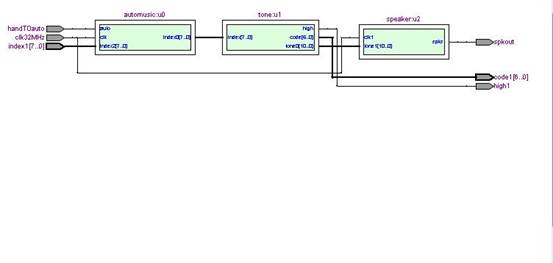

系统由数控分频器、乐曲存储模块以及发声模块组成。数控分频器对FPGA的基准频率进行分频,得到与各个音阶对应的频率输出。乐曲存储模块产生节拍控制和音阶选择信号,即在此模块中可存放一个乐曲曲谱真值表,由一个计数器来控制此真值表的输出,而由计数器的计数时钟信号作为乐曲节拍控制信号。由发声模块产生音符对应的频率的信号来使扬声器发音。

(1)模块automusic

模块automsic由auto信号来选择发声的方式,auto=0时系统自动播放内置的音乐,auto=1时由键盘来手动演奏音乐。

(2)模块TONE

模块Tone是音阶发生器,当8位发声控制输入Index中某一位为高电平时,则对应某一音阶的数值将从端口Tone输出,作为获得该音阶的分频预置值;同时由Code输出对应该音阶简谱的显示数码,如‘5’,并由High输出指示音阶高8度显示。

(3)模块Speaker

模块Speaker中的主要电路是一个数控分频器,它由一个初值可预置的加法计数器构成,当模块Speaker由端口Tone获得一个2进制数后,将以此值为计数器的预置数,对端口Clk12MHZ输入的频率进行分频,之后由Spkout向扬声器输出发声。

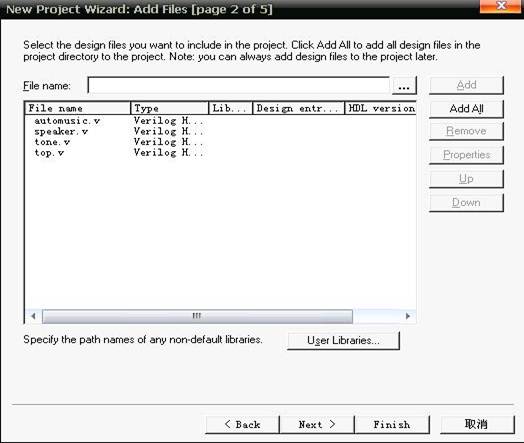

3.2操作过程

新建工程

添加模块

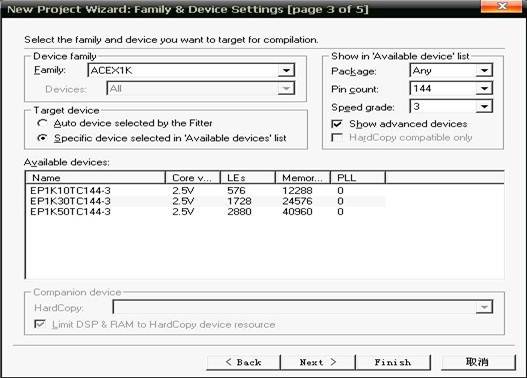

查找对应芯片

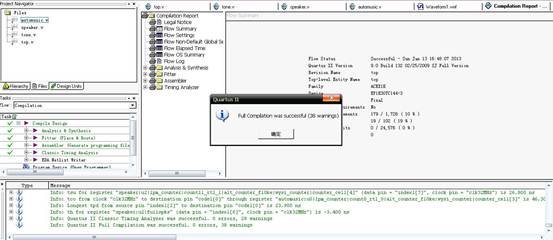

调试程序

波形仿真

生成逻辑图

设置管脚

3.3设计和调试过程中出现的问题及解决方法

在初次编写分频模块时候,使用的是比较基本的计数器分频法,编写程序后在modelsim软件中进行了仿真,发现无法观察到分频情况。经过分析,原因是由于分频比过大,因此在波形图中很难观察到。而且由于预分频的占空比很小,更难以观察到高电平。在原因找到后,为了考察程序的性能,我们将输入频率减小。同时适当缩小分频比,这样就得到了模块仿真中的分频波形。

四、设计总结和心得体会

通过这次课程设计发现,只有理论水平提高了;才能够将课本知识与实践相整合,理论知识服务于教学实践,以增强自己的动手能力。这个实验十分有意义 我获得很深刻的经验。通过这次课程设计,我们知道了理论和实际的距离,也知道了理论和实际想结合的重要性,,也从中得知了很多书本上无法得知的知识。学习不但要立足于书本,以解决理论和实际教学中的实际问题为目的,还要以实践相结合,理论问题即实践课题,解决问题即课程研究,学生自己就是一个专家,通过自己的手来解决问题比用脑子解决问题更加深刻。学习就应该采取理论与实践结合的方式,理论的问题,也就是实践性的课题。这种做法既有助于完成理论知识的巩固,又有助于带动实践,解决实际问题,加强我们的动手能力和解决问题的能力。

参考文献:(五号,宋体加粗)

[1] 潘松,《EDA实用教程》,科学出版社,20##年

附录:(源程序)

module top(clk32MHz,handTOauto, code1,index1,high1,spkout);

input clk32MHz,handTOauto; //32MHz系统时钟,键盘输入/自动演奏

input [7:0] index1;//键盘输入信号

output [6:0] code1; //音符显示信号

output high1,spkout;//高低音节信号,音频信号

wire [10:0] tone;

wire [7:0] indx;

automusic u0(.clk(clk32MHz),.index2(index1),.index0(indx),.auto(handTOauto));

tone u1(.index(indx),.tone0(tone),.code(code1),.high(high1));

speaker u2(.clk1(clk32MHz),.tone1(tone),.spks(spkout));

Endmodule

module automusic(clk,auto,index2,index0);//实现自动演奏功能。

input clk,auto;//系统时钟;键盘输入/自动演奏

input [7:0] index2;//键盘输入信号

output [7:0] index0;//音符信号输出

reg [7:0] index0;

reg [4:0] count0;

reg clk2;

reg [22:0] count;

always @(clk,auto) //此过程完成对系统时钟8M的分频,得到4Hz的信号clk2

begin

if (auto)

begin

count=23'd0;

clk2<=1'b1;

end

else if (clk)

begin

count=count+1'b1;

if (count==23'd4000000) clk2<=1'b1;

else if (count==23'd8000000) begin clk2<=1'b0; count=23'd0;end

end

end

always @(posedge clk2)//此过程完成自动演奏部分曲的地址累加

begin

if (count0==5'd31)

count0<=5'd0;

else

count0<=count0+1'b1;

end

always @(count0,auto,index2)

begin

if (!auto)

case(count0) //此case语句:存储自动演奏部分的曲

5'd0: index0<=8'b00000100; //3

5'd1: index0<=8'b00000100;

5'd2: index0<=8'b00000100;

5'd3: index0<=8'b00000100;

5'd4: index0<=8'b00010000;//5

5'd5: index0<=8'b00010000;

5'd6: index0<=8'b00010000;

5'd7: index0<=8'b00100000;//6

5'd8: index0<=8'b10000000;//8

5'd9: index0<=8'b10000000;

5'd10: index0<=8'b10000000;

5'd11: index0<=8'b00000100;

5'd12: index0<=8'b00000010;//2

5'd13: index0<=8'b00000010;

5'd14: index0<=8'b00000001;//1

5'd15: index0<=8'b00000001;

5'd16: index0<=8'b00010000;//5

5'd17: index0<=8'b00010000;

5'd18: index0<=8'b00001000;//4

5'd19: index0<=8'b00001000;

5'd20: index0<=8'b00001000;

5'd21: index0<=8'b00000100;

5'd22: index0<=8'b00000010;

5'd23: index0<=8'b00000010;

5'd24: index0<=8'b00010000;

5'd25: index0<=8'b00010000;

5'd26: index0<=8'b00001000;

5'd27: index0<=8'b00001000;

5'd28: index0<=8'b00000100;

5'd29: index0<=8'b00000100;

5'd30: index0<=8'b00000010;

5'd31: index0<=8'b00000010;

default: ;

endcase

else index0<=index2; //键盘输入音符信号输出

end

Endmodule

module tone(index,code,high,tone0); //音阶发生器程序。

input [7:0] index;//音符输入信号

output [6:0] code;//音符显示信号

output high;//高低音显示信号

output [10:0] tone0;//音符的分频系数

reg high;

reg [6:0] code;

reg [10:0] tone0;

always @(index)//此过程完成音符到音符的分频系数译码,音符的显示,高低音阶

begin

case(index)

8'b00000001: begin tone0=11'd773; code=6'b1001111;high=1'b1;end

8'b00000010: begin tone0=11'd912; code=6'b0010010;high=1'b1;end

8'b00000100: begin tone0=11'd1116;code=6'b1001100;high=1'b1;end

8'b00010000: begin tone0=11'd1197;code=6'b0100100;high=1'b1;end

8'b00100000: begin tone0=11'd1290;code=6'b0100000;high=1'b0;end

8'b01000000: begin tone0=11'd1372;code=6'b0001111;high=1'b0;end

8'b10000000: begin tone0=11'd1410;code=6'b0000000;high=1'b0;end

default: begin tone0=11'd2047;code=6'b0000001;high=1'b0;end

endcase

end

endmodule

module speaker(clk1,tone1, spks);//实现数控分频

input clk1;//系统时钟

input [10:0] tone1;//音符分频系数

output spks;//驱动扬声器的音频信号

reg [10:0] tone2;

reg spks;

reg preclk,fullspks,count2;

reg [3:0] count;

reg [10:0] count11;

always @(posedge clk1) //此过程对系统时钟进行4分频

begin

count=count+1'b1;

if (count==4'h2)

preclk<=1'b1;

else

if (count==4'h4)

begin

preclk<=1'b0;

count=4'h0;

end

end

always @(posedge preclk) //此过程按照tone1输入的分频系数对8MHz的脉冲再次分频,得到所需要的音符频率

begin

if (count11<tone1)

begin

count11=count11+1;

fullspks<=1'b1;

end

else

begin

count11<=0;

fullspks<=1'b0;

end

end

always @(posedge fullspks) //此进程对fullspks进行2分频

begin

count2=~count2;

if (count2)

spks<=1'b1;

else

spks<=1'b0;

end

Endmodule